Hello! 大家好,本次項目主題是“基于FPGA的ECG信號采集與處理系統設計”,與眾多STM32或Arduino等單片機直接利用軟件編程調用庫函數不同,本項目以底層邏輯為切入點進行數字電路設計,更加關注電路底層的細節,包括基礎模塊的劃分、接口信號的定義、verilog代碼設計、仿真驗證以及板級調試,在滿足性能要求下,同時會評估資源消耗問題,希望大家能和我一起一步一步的完成此次工程項目,而不是簡單的copy。其中難免有錯誤,希望各位指正。

引言: FPGA開發和數字IC設計十分相似,而兩者最基礎是verilog代碼設計,verilog是硬件描述語言,實現的數字電路具備硬件并行處理的優點,所以verilog設計思想與基于軟件的編程語言是有很大不同的,復雜的verilog代碼設計不是隨隨便便直接在板子上調試成功的。 本項目側重對設計代碼的仿真驗證,而不是簡簡單單對代碼 “搬運工”,達到所謂“快速”入門的假現象。在FPGA開發中,每一行verilog代碼已經決定了電路的性能和功能,仿真是對verilog代碼設計的有效驗證方法,因為代碼存在的bug在仿真中會一一被定位出來,“速成”FPGA開發都是假的,不能一行一行代碼看懂和敲出來,verilog學習的時長都是無用功,正確設計方法+動手練習是FPGA開發/數字電路設計的正確打開方法。

以下是我個人設計的方法: 首先根據你的硬件條件包括FPGA板型和其他硬件(AD、VGA、LCD、舵機、攝像頭等等),確定一個硬件的詳細設計方案; 接著根據需求和參考資料將整體劃分到各個小模塊,并確定各個模塊接口之間的數據信號和控制信號;畫時序圖主要是根據數據信號走向需要哪些控制信號,而控制信號主要實現方式就是cnt、enable、flag等等。

其次按照圖紙就可以敲代碼了,而verilog代碼語法不是很難,主要是算術運算符、賦值運算符、關系運算符、邏輯運算符、條件運算符、位運算符以及移位拼接等,一般設計會這些足夠了,而往往多數初學者覺FPGA設計很簡單啊,大概指的這部分語法簡單,但是在敲代碼過程中還要考慮到組合邏輯以及時序邏輯中常用的模塊,{組合邏輯主要包括常用邏輯門(與門、或門、非門、異或等)、比較器、半加器、全加器、乘法器、數據選擇器、三態門,時序邏輯主要包括D觸發器、兩級D觸發器、帶異步復位的D觸發器、帶異步復位同步清零的D觸發器、移位寄存器、單口RAM、偽雙口RAM、真雙口RAM、單口ROM、有限狀態機等}。而這些基本單元在寫代碼過程做到心中有數,因為這些決定了設計的PPA(Performance,Power,Area); 最后再通過仿真工具對設計的代碼進行驗證,首先是功能仿真也就是RTL行為級仿真,主要是檢查代碼中的語法錯誤以及代碼行為的正確性,但是不包括延時信息,驗證之前“模塊劃分與接口定義”階段。其次是后仿真也就是時序仿真,在設計布局布線后提供一個時序仿真模型,驗證之前“畫接口信號時序”階段。

步驟一:項目框架

目的意義 在我國,隨著生活節奏加快,心血管疾病的發病率有逐年遞增的趨勢;同時由于人們生活水平和健康意識的不斷提高,對心臟類疾病進行實時監護的需求也不斷增加。但是,心血管疾病本身具有無癥狀性(病人在發生心肌缺血時并沒有胸痛、心絞痛等常見癥狀)和間歇性。 選擇這個主題主要原因之一是開發一種可以幫主人們日常生活的非侵入性設備—基于FPGA的ECG信號采集與處理。市場上有許多ECG信號檢測產品可以提高效率(尺寸較小,將數據保存在云中等等),但是其中任何一件產品都很少涉及到復雜信號處理,并沒有與數據庫進行比對。

內容及結構安排:

本文基于Xilinx公司的Artix-7系列芯片xc7a35tcpg236-1和AD83232采集板搭建一套硬件平臺用以異常ECG信號檢測系統。使用Vivado和ModelSim設計和仿真各個系統模塊的功能,本系統主要有AD8232信號采集,FPGA存儲和處理,C#GUI顯示及matlab處理。其中FPGA處理是核心部分,由以下模塊構成:AD模塊、RAM模塊、UART模塊及濾波模塊。本文采用Verilog HDL硬件描述語言進行編程,XADC具有兩個專用的差分輸入引腳Vp和Vn,可用于采樣模擬信號,通過ADC模塊完成100 MHz到360 Hz的數據采樣,同時采用低通濾波器消除共模噪聲;在所有存儲單元中存滿ECG的樣本數據后,將生成一個脈沖以觸發向PC的傳輸。UART模塊將接收一個信號,該信號使用TX模塊進行發送,當接收UART檢測到起始位時,它將開始以稱為波特率的特定頻率讀取輸入位。

本項目主要有以下方面:

1.FPGA學習流程。編寫項目詳細設計方案,主要包括數據通路和控制通路的設計,模塊劃分與接口信號的定義,數據通路原理圖以及控制通路時序圖,verilog代碼的具體設計,以及仿真驗證,下載到FPGA開發板調試。在verilog代碼設計過程會描述時序圖,用到IP核,數據通路的寄存器消耗資源進行評估。

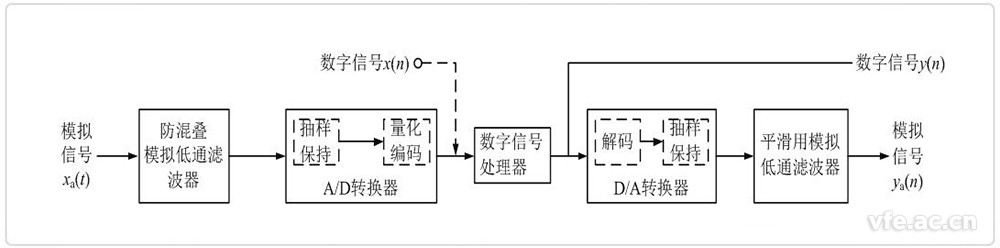

2.用到的濾波處理。在信號處理中,數字濾波器是一種對采樣的離散時間信號執行數學運算以減少或增強該信號某些方面的系統。數字濾波器系統通常由一個模數轉換器對輸入信號進行采樣,使用FPGA或ASIC代替通用微處理器或具有特定并行架構的專用DSP,以加快諸如過濾之類的操作。

項目簡介: 包含四大部分:AD采集模塊、RAM存儲模塊、濾波處理模塊、UART模塊。 首先,AD8232放大器輸出是一個介于0至3.3V之間的模擬值,ADC模塊的輸入應為1V,因此需要進行分壓。放置在放大器的輸出和FPGA板的輸入(Vp引腳)之間,AD模塊包括PLL和XADC 完成100 MHz到360 Hz的數據采樣。 其次,我們利用RAM模塊存儲通過ADC采集的樣本。模塊具有2個命令模式:讀取和寫入。這兩種狀態由啟用寫模式時為高電平和禁用寫模式時為低電平的信號控制。

Step1:確定整個設計思路,ECG信號檢測的總體框圖,確定程序流程框圖 Step2: AD模塊、包括XADC和分頻時鐘接口定義,進行具體verilog代碼設計和仿真驗證 Step3:RAM讀寫模塊、根據狀態機進行接口定義,進行具體verilog代碼設計和仿真驗證 Step4:Digital filter模塊、UART模塊接口定義,進行具體verilog代碼設計和仿真驗證 Step5:進行功能擴展,并將以上所有模塊集成在一起,并且做整個仿真驗證以及板級調試,通過在C#GUI中顯示及保存為.csv文件,利用MATLAB進行相關算法處理,整理打包完整的開源方案所有資料。

編輯:jq

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636335 -

ECG

+關注

關注

4文章

132瀏覽量

53942

原文標題:《來實戰》第6期:基于FPGA的ECG信號采集與處理系統設計

文章出處:【微信號:cirmall,微信公眾號:電路設計技能】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

零線電流處理系統

中科億海微FPGA高速信號采集板:助力工業智能控制的高效采集與精準處理

【VPX650 】青翼凌云科技基于 VPX 系統架構的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX雙FMC接口通用信號處理平臺

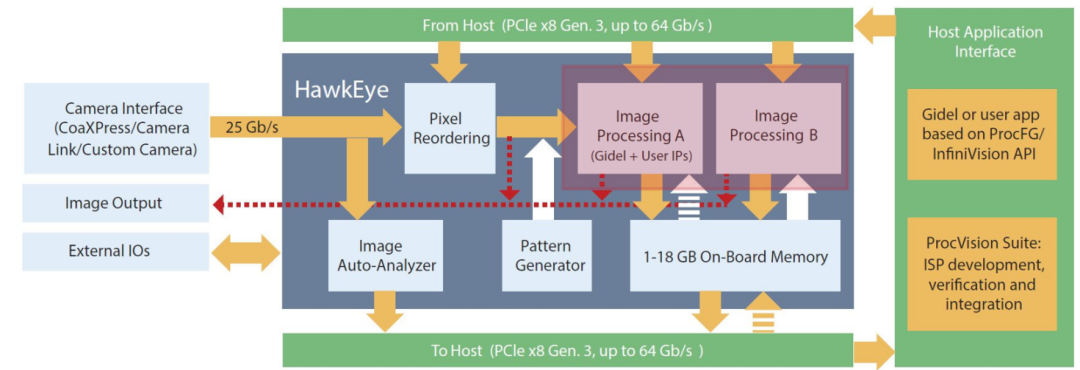

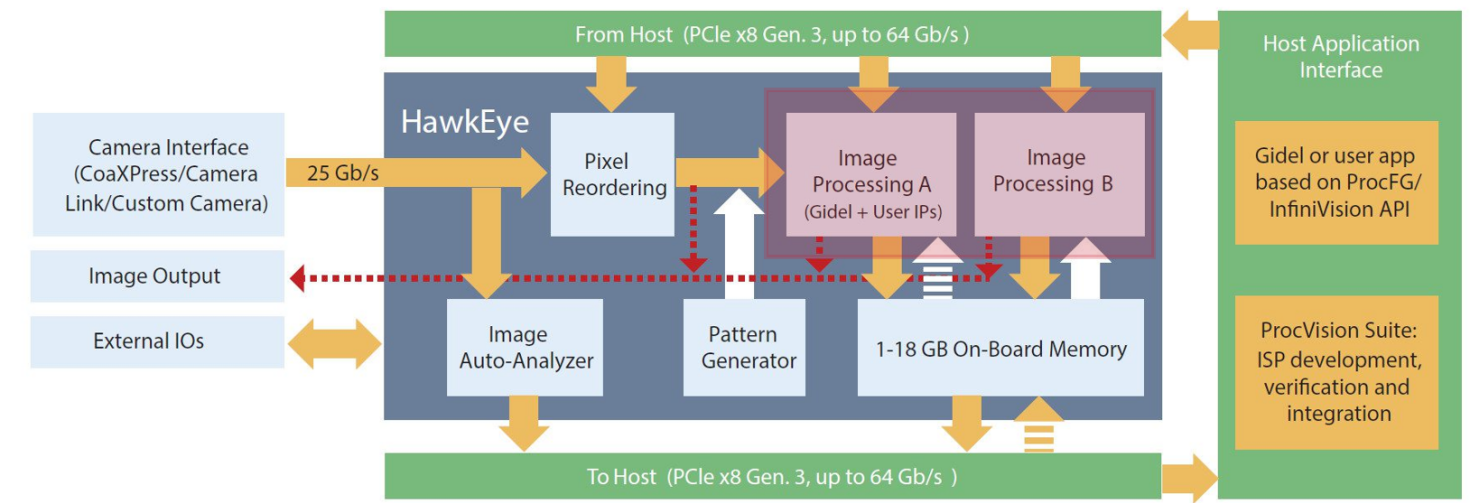

友思特方案 | FPGA 加持,友思特圖像采集卡高速預處理助力視覺系統運行提速增效

FPGA的ECG信號采集與處理系統是怎么樣設計的呢?

FPGA的ECG信號采集與處理系統是怎么樣設計的呢?

評論