在生成ROM時(shí)需要提供coe文件,如下圖所示。這個(gè)coe文件本質(zhì)上就是Memory的初始化文件,Xilinx對(duì)其有具體的格式要求。

coe文件格式

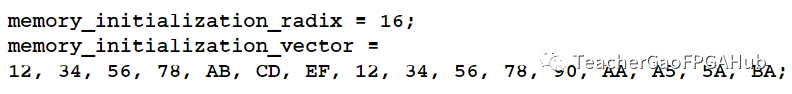

coe文件格式要求如下圖所示,其中前兩行是固定的。其中第一行定義了Radix,可以是2、10或16,意味著第2行定義的數(shù)據(jù)向量內(nèi)容可以是二進(jìn)制、十進(jìn)制或十六進(jìn)制。這里需要說明的是定義的數(shù)據(jù)向量各個(gè)數(shù)據(jù)之間可以是空格,也可以是逗號(hào)(但此時(shí)最后一個(gè)數(shù)據(jù)要以分號(hào)結(jié)尾)或者回車換行符。

生成coe文件

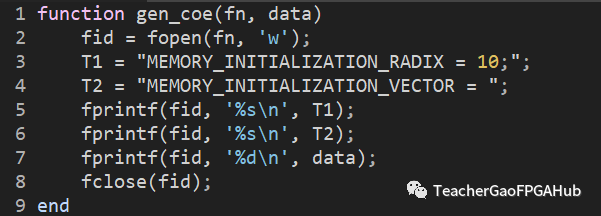

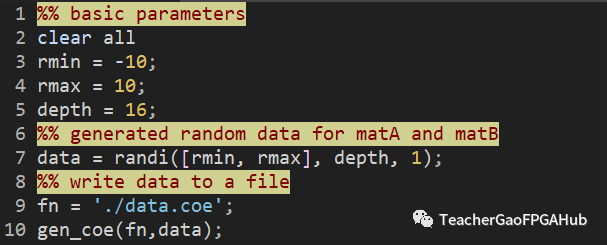

Matlab作為主流的算法開發(fā)與驗(yàn)證平臺(tái)之一往往成為很多數(shù)據(jù)的重要來源,因此,在Matlab下生成coe文件是非常普遍的操作。這里要用到Matlab提供的一些文件操作函數(shù),如fopen、fprintf和fclose等。在此,我們定義函數(shù)gen_coe,它接收兩個(gè)參數(shù)fn和data。其中fn為生成的coe文件名,data為行或列向量。要求為十進(jìn)制整數(shù)。

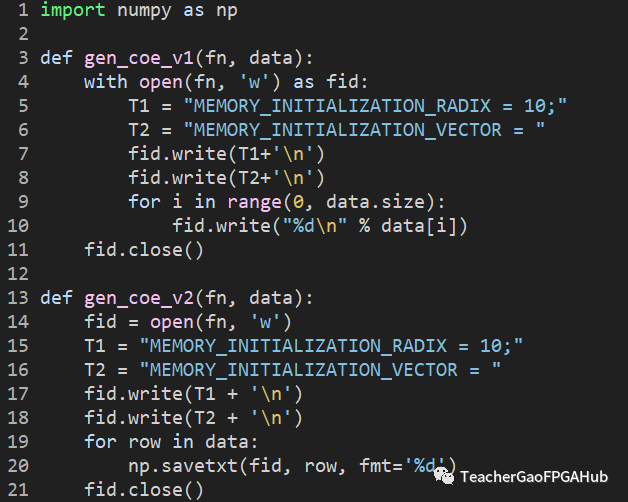

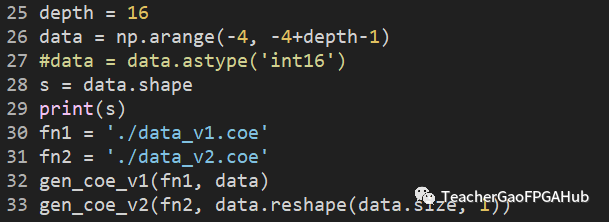

Python提供了擴(kuò)展庫Numpy,可以方便地實(shí)現(xiàn)對(duì)矩陣的操作,利用Python也可以快捷地生成coe文件。這里提供兩個(gè)版本。兩個(gè)函數(shù)都有相同的參數(shù)fn和data,含義與上文提到的Matlab函數(shù)保持一致。在gen_coe_v1中,通過write()完成了寫數(shù)據(jù)操作。在gen_coe_v2中,則是通過np.savetxt完成了寫數(shù)據(jù)操作。在這個(gè)案例中,np.savetxt接收3個(gè)參數(shù),第一個(gè)參數(shù)為文件ID,第二個(gè)參數(shù)為矩陣的行索引,第三個(gè)參數(shù)為寫入格式。

原文標(biāo)題:如何生成ROM的coe文件

文章出處:【微信公眾號(hào):Lauren的FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1661文章

22442瀏覽量

637498 -

ROM

+關(guān)注

關(guān)注

4文章

579瀏覽量

89224 -

Memory

+關(guān)注

關(guān)注

1文章

80瀏覽量

30738

原文標(biāo)題:如何生成ROM的coe文件

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何將Primus生成的波形文件導(dǎo)入MATLAB

求助,關(guān)于mcs文件生成的問題求解

使用NucleiStudio生成tb仿真需要的.verilog文件

win10環(huán)境下使用vivado生成.bit與.mcs文件

RISCV指令二進(jìn)制編碼利用matlab生成E203仿真可用文件

如何在Vivado上仿真蜂鳥SOC,仿真NucleiStudio編譯好的程序

scons使用dist生成的工程缺少文件怎么解決?

使用env生成的keil文件好多文件找不到路徑,為什么?

如何使用 PinConfigure 工具生成 GPIO 代碼文件和 OrCAD/Protel IC 組件?

AICube生成部署文件失敗的原因?怎么解決?

Simcenter FLOEFD BCI-ROM和Package Creator模塊

Analog Devices / Maxim Integrated PD60-4H-1461-CoE單軸步進(jìn)電機(jī)數(shù)據(jù)手冊(cè)

基于FPGA搭建神經(jīng)網(wǎng)絡(luò)的步驟解析

如何生成ROM的coe文件?

如何生成ROM的coe文件?

評(píng)論