摩爾定律,雖命名為“定律”,但究其本質更像是一條預言,一條在過去的 50 年間始終引導半導體行業發展的偉大預言。但是,現階段摩爾定律下工藝的無限制成長終會遭遇一道名為“物理極限”的壁壘,如何繞過壁壘以延續乃至超越摩爾定律成為了現如今業界的發展重心。

如果說系統級芯片(System on Chip,英文簡稱 SoC)技術是摩爾定律不斷發展所產生的重要產物,那么系統級封裝(System in Package,英文簡稱 SiP)技術便是實現超越摩爾定律的關鍵路徑。在“后摩爾定律”所提供的關鍵助力之下,SiP 生態系統正持續成長以緩解因晶體管尺寸日趨物理極限產生的壓力。

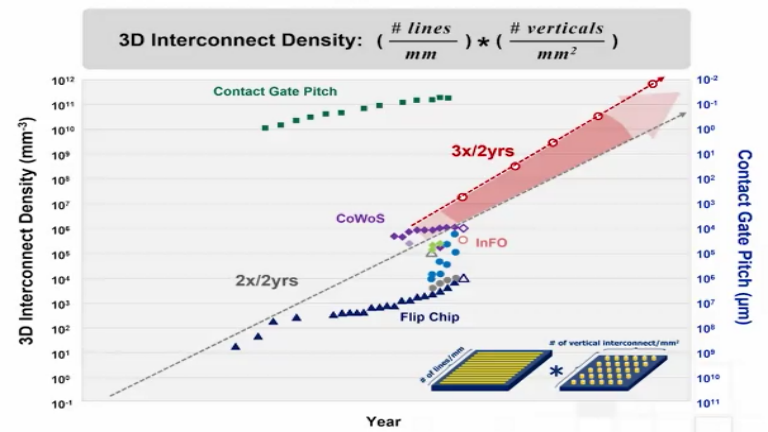

(圖片來源:TSMC) 隨著 5G 通信及機器學習技術應用的快速普及,系統級封裝 SiP 技術在短短的時間內便已經成為實現微系統功能多樣化、集成異構化、體積及成本最小化的最優方案。

對于 SiP 技術的生態系統,除了業內人士非常熟悉的半導體材料和計算機輔助設計(CAD)軟件之外,IC 基板技術及與之關聯的供應鏈同樣是 SiP 生態系統的重要一環。上圖所示為當前半導體封測行業中常見的基板技術及其趨勢。 目前從技術發展的趨勢來看,雙面塑模成型技術、電磁干擾屏蔽技術、激光輔助鍵合技術可以并稱為拉動系統級封裝技術發展的“三駕創新馬車”。NO.1雙面塑模成型技術雙面塑模成型技術(Double-Sided Molding Technology)之所以成為系統級封裝工程專家的新寵,主要有兩個原因: (一)有效減少封裝體積以節省空間。 (二)有效縮短多個裸芯(Bare Dies)及被動元件之間的連接線路以降低系統阻抗、提升整體電氣性能。 更小的封裝體積、更強的電氣性能,為雙面塑模成型技術在 SiP 領域的廣泛應用前景提供了良好的基礎。下圖所示為一例由長電科技成功導入規模量產的雙面塑模成型 SiP 射頻前端模塊產品。

長電科技的雙面封裝 SiP 產品采用了多項先進工藝以確保雙面塑模成型技術的成功應用。該產品采用了 C-mold 工藝,實現了芯片底部空間的完整填充,并有效減少了封裝后的殘留應力, 保證了封裝的可靠性。

同時 Grinding 工藝的應用,使封裝厚度有了較大范圍的選擇,同步實現精準控制產品的厚度公差。為了去除流程中殘留的多余塑封料,長電科技還采用了 Laser ablation 工藝,以確保產品擁有更好的可焊性。

這項技術看似稀松平常,實則機關暗藏,每一項創新技術的成功落地都要經歷許多挑戰。雙面塑模成型(Double-Sided Molding Technology)技術的落地主要面臨著以下三大挑戰: (一)塑模成型過程中的翹曲問題。 (二)背面精磨(Back Grinding)過程中的管控風險。 (三)激光灼刻(Laser Ablating)及錫球成型(Solder Ball Making)中的管控風險。 面對全新工藝所帶來的諸多挑戰,長電科技選擇直面困難,攻克一系列技術難題,并成功于 2020 年 4 月通過全球行業領先客戶的認證,實現了雙面封裝 SiP 產品的量產。 在這項全新突破的工藝中,長電科技嚴格把控生產流程,采用高度自動化的先進制程,將在雙面塑模成型過程可能發生的各類風險隱患進行了有效降低。

原文標題:詳解 SiP 技術體系中的三駕創新馬車(一)

文章出處:【微信公眾號:長電科技】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

半導體

+關注

關注

339文章

30767瀏覽量

264440 -

SiP

+關注

關注

5文章

540瀏覽量

107757 -

長電科技

+關注

關注

5文章

394瀏覽量

33503

原文標題:詳解 SiP 技術體系中的三駕創新馬車(一)

文章出處:【微信號:gh_0837f8870e15,微信公眾號:長電科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

漏致勢壘降低效應如何影響晶體管性能

MUN5136數字晶體管技術解析與應用指南

電壓選擇晶體管應用電路第二期

晶體管的定義,晶體管測量參數和參數測量儀器

晶體管的基本結構和發展歷程

0.45-6.0 GHz 低噪聲晶體管 skyworksinc

多值電場型電壓選擇晶體管結構

晶體管架構的演變過程

下一代高速芯片晶體管解制造問題解決了!

無結場效應晶體管詳解

LP395 系列 36V 功率晶體管數據手冊

多值電場型電壓選擇晶體管結構

晶體管電路設計(下)

智能計算新紀元:具記憶功能的晶體管問世

SiP正持續成長以緩解因晶體管尺寸日趨物理極限的壓力

SiP正持續成長以緩解因晶體管尺寸日趨物理極限的壓力

評論