在大多數(shù)電子系統(tǒng)中,降噪是一個(gè)重要設(shè)計(jì)問題。與功耗限制、環(huán)境溫度變化、尺寸限制以及速度和精度要求一樣,必須處理好無(wú)所不在的噪聲因素,才能使最終設(shè)計(jì)獲得成功。這里,我們不考慮用于降低“外部噪聲”(與信號(hào)一起到達(dá)系統(tǒng))的技術(shù),因?yàn)槠浯嬖谝话悴皇茉O(shè)計(jì)工程師直接控制。相比之下,防止“內(nèi)部噪聲”(電路或系統(tǒng)內(nèi)部產(chǎn)生或耦合的噪聲)擾亂信號(hào)則是設(shè)計(jì)工程師的直接責(zé)任。今天我們就說說“接地”,而且是針對(duì)高頻工作的“接地"

“接地”(Grounding)一般指將電路、設(shè)備或系統(tǒng)連接到一個(gè)作為參考電位點(diǎn)或參考電位面的良好導(dǎo)體上,為電路或系統(tǒng)與“地”之間建立一個(gè)低阻抗的通道。

地線是作為電路或系統(tǒng)電位基準(zhǔn)點(diǎn)的等電位體,是系統(tǒng)中各個(gè)電路的公共導(dǎo)體,任何電路的電流都會(huì)經(jīng)過地線形成回路。然而,任何導(dǎo)體都存在著一定的阻抗,當(dāng)?shù)鼐€中有電流通過時(shí),根據(jù)歐姆定律,地線上就會(huì)有電壓存在,那么地線就不是一個(gè)等電位體。所以在實(shí)際設(shè)計(jì)電路或系統(tǒng)時(shí),關(guān)于地線上各點(diǎn)的電位一定相等的假設(shè)就不是成立的,實(shí)際的情況是底線上各點(diǎn)存在電位差,有的相位差還可能很大。地線的公共阻抗會(huì)使各接地點(diǎn)間形成一定的電壓,從而就會(huì)產(chǎn)生接地干擾。

如上面所說,地線作為導(dǎo)體,存在一定的阻抗,顧名思義,阻抗也就是由電阻和感抗兩部分組成,即:

導(dǎo)體的阻抗是頻率的函數(shù),隨著頻率的升高,阻抗增加很快。對(duì)于高速數(shù)字電路而言,電路的時(shí)鐘頻率是很高的,脈沖信號(hào)包涵豐富的高頻成分,因此會(huì)在地線上產(chǎn)生較大的電壓,則地線阻抗對(duì)數(shù)字電路的干擾十分可觀。

在電子產(chǎn)品的PCB設(shè)計(jì)中,抑制或防止地線干擾是需要考慮的最主要問題之一。所謂干擾,必然是發(fā)生在不同的單元電路、部件或系統(tǒng)之間,而地線干擾是指通過公用地線的方式產(chǎn)生的信號(hào)干擾。注意這里所提到的信號(hào),通常是指交流信號(hào)或者跳變信號(hào)。地線干擾的形式很多,有人把它歸結(jié)成兩類:地線環(huán)路干擾、公共阻抗干擾,其實(shí)應(yīng)該還要加上地線環(huán)路的電磁耦合干擾,因此是三類。下圖可以很好的說明三類地線干擾的成因。

一、地環(huán)路干擾。

橫向,每根導(dǎo)線上的電流不同,因此會(huì)產(chǎn)生差模電壓,對(duì)電路造成影響。具體的說就是“其他電路單元B”的地線電流,在J、N、L、M形成的“地線環(huán)路”中,對(duì)放大器A1和A2造成了影響。由于這種干擾是由電纜與地線構(gòu)成的環(huán)路電流產(chǎn)生的,因此成為地環(huán)路干擾。

二、地環(huán)路電磁耦合干擾。

在實(shí)際電路的PCB上,J、N、L、M形成的“地線環(huán)路”將包圍一定的面積,根據(jù)電磁感應(yīng)定律,如果這個(gè)環(huán)路所包圍的面積中有變化的磁場(chǎng)存在,就會(huì)在環(huán)路中產(chǎn)生感生電流,形成干擾。空間磁場(chǎng)的變化無(wú)處不在,于是包圍的面積越大干擾就越嚴(yán)重。

三、公共阻抗干擾。

認(rèn)真考察上圖所示的電路結(jié)構(gòu),我們將發(fā)現(xiàn),J、N、L、M中,有一條連接是多余的,隨便去除其一,仍然可以滿足各個(gè)接地點(diǎn)的連通關(guān)系,同時(shí)又可以消除地線環(huán)路。那么,將哪一條連線去除比較合理呢?這時(shí)就要考慮另一類的干擾問題——公共阻抗干擾。

①去除J:這是最差的方案。J去除后地線環(huán)路似乎消失了,可是另一個(gè)更可怕的環(huán)路又形成了(I、N、L、M),其中I是信號(hào)線,因此干擾比原來(lái)有線J時(shí)還要嚴(yán)重。

②去除M:環(huán)路消失,但是我們發(fā)現(xiàn),此時(shí)放大器A2的地線電流需要流過J、N到達(dá)接地零點(diǎn),注意N段是A1和A2共同的接地線,因此A2接地電流在N上形成的電壓降就加到了A1上,形成干擾。這種因共用一段地線而形成的干擾稱為“公共阻抗干擾”。

③去除L:不僅不能解決A2與A1之間的公共阻抗干擾問題,還引起了“B單元電路”與A1、A2之間的公共阻抗干擾問題。

④去除N:看來(lái)這是最后的方法。其實(shí)這樣做將使M成為A1、A2的“公用阻抗”,同樣形成干擾。還是存在問題!但是,我們注意到,此法中的干擾是A1對(duì)A2的干擾,A2是后級(jí),工作信號(hào)強(qiáng)度遠(yuǎn)大于A1,因此A1對(duì)A2的干擾,很難造成不良后果。

最合理的走線方案是:去除N,然后將M的下端直接連到“接地信號(hào)零點(diǎn)”上。

以上是關(guān)于接地干擾產(chǎn)生的原因,下面再介紹的幾種常見的接地方式,結(jié)合前面對(duì)接地干擾產(chǎn)生原因的了解,有助于我們?cè)趯?shí)際設(shè)計(jì)PCB板電路時(shí),正確的選擇干擾最小的接地方式,設(shè)計(jì)出合理的電路或系統(tǒng)。

信號(hào)接地方式可以大體上分為:?jiǎn)吸c(diǎn)接地、多點(diǎn)接地、混合接地和懸浮接地。

單點(diǎn)接地。單點(diǎn)接地就是把真?zhèn)€電路系統(tǒng)中的某一點(diǎn)作為接地的基準(zhǔn)點(diǎn),所有電路及設(shè)備的地線都必須接到這一點(diǎn)上,并以該點(diǎn)作為電路、設(shè)備的零電位參考點(diǎn)。單點(diǎn)接地又分為串聯(lián)單點(diǎn)接地和并聯(lián)單點(diǎn)接地。如下圖所示:

圖2.串聯(lián)單點(diǎn)接地

對(duì)于串聯(lián)式單點(diǎn)接地方式,如果該電路的功率很大,會(huì)產(chǎn)生很大的電路回流,在有限阻抗上會(huì)產(chǎn)生一個(gè)電壓降,造成電路和基準(zhǔn)地之間的電壓參考值的差異可能使系統(tǒng)不能如預(yù)期的那樣工作。如存在多種不同功率等級(jí)的電路,不能采用串聯(lián)式單點(diǎn)接地方式,因?yàn)榇蠊β孰娐樊a(chǎn)生大的回地電流,將影響低功率器件和電路。如果說一定要采取這種接地方法,那么最敏感的電路必須直接設(shè)置在電源輸入位置處,并且盡量遠(yuǎn)離低功率器件和電路。串聯(lián)單點(diǎn)接地方式和結(jié)構(gòu)都比較簡(jiǎn)單,如果各個(gè)電路的接地引線比較短,其阻抗也會(huì)相對(duì)小。如果各個(gè)電路的接地電平差別不大,可以采用這種接地方式。

并聯(lián)單點(diǎn)接地方式中,每個(gè)電路單元獨(dú)用地線連接到同意地點(diǎn),其優(yōu)點(diǎn)是各電路的地點(diǎn)為只與本電路的地電流及地線阻抗有關(guān),不受其他電路的影響。低頻時(shí)可有效的避免各電路單元之間的低阻抗干擾,但是也存在很多缺點(diǎn)。主要表現(xiàn)在:首先,各個(gè)電路分別采用獨(dú)立地線接地,需要多跟地線,勢(shì)必增加地線長(zhǎng)度,從而增加地阻抗,結(jié)構(gòu)復(fù)雜使用麻煩;其次,這種接地方式會(huì)造成各地線互相間的耦合,并且隨著頻率增加,地線阻抗、地線電感、電線電容都會(huì)增大,這種接地方式不適用高頻電路。

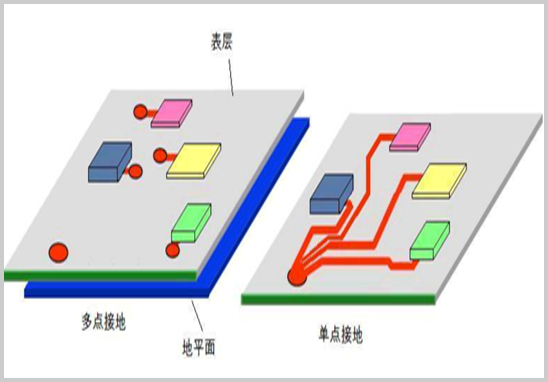

多點(diǎn)接地。多點(diǎn)接地是指某一個(gè)系統(tǒng)中各個(gè)需要接地的電路、設(shè)備都直接接到距離它最近的接地平面上,一邊接地長(zhǎng)度最短,接地阻抗減到最小。

當(dāng)電子系統(tǒng)的工作頻率高于1MHz時(shí),以致工作波長(zhǎng)與系統(tǒng)接地引線的長(zhǎng)度可比擬時(shí),地線就象一根終端短路的傳輸線,地線的電流、電壓呈駐波分布,地線變成了輻射天線,而不能起到地線的作用。為了減少接地阻抗,避免輻射,地線的長(zhǎng)度應(yīng)小于1/20波長(zhǎng),因而單點(diǎn)接地方法是不合理的,通常采用多點(diǎn)接地技術(shù)。多點(diǎn)接地電路結(jié)構(gòu)簡(jiǎn)單,接地線上可能出現(xiàn)的高頻駐波現(xiàn)象顯著減少,但多點(diǎn)接地可能會(huì)導(dǎo)致設(shè)備內(nèi)部形成許多接地環(huán)路,容易對(duì)設(shè)備內(nèi)部的敏感店里產(chǎn)生地環(huán)路干擾。

一般來(lái)說,頻率在1MHz以下時(shí)可采用單點(diǎn)接地方式,頻率高于10MHz時(shí)可采用多點(diǎn)接地方式,而頻率在1——10MHz時(shí),通常采用混合接地方式。

混合接地。混和接地是單點(diǎn)接地和多點(diǎn)接地的復(fù)合。在PCB 中存在高低頻混合頻率時(shí),常使用這種接地方式。

圖5.混合接地-容性耦合 圖6.混合接地-感性耦合

圖5和圖6提供了兩種混和接地方法。對(duì)于電容耦合型電路,在低頻時(shí)呈現(xiàn)單點(diǎn)接地結(jié)構(gòu),而在高頻時(shí)呈現(xiàn)多點(diǎn)接地狀態(tài)。這是因?yàn)殡娙輰⒏哳l電流分流到了地。這種方法成功的關(guān)鍵在于清楚使用的頻率和接地電流預(yù)期流向。在接地拓?fù)浣Y(jié)構(gòu)中使用電容和電感,使我們能用一種優(yōu)化設(shè)計(jì)的方式控制射頻電流。通過確定射頻電流要通過的路徑,可以控制PCB 的布線。對(duì)射頻電流回路缺乏認(rèn)識(shí)可能導(dǎo)致輻射或敏感度方面的問題。

懸浮接地。懸浮地是指設(shè)備的地線系統(tǒng)與殼體構(gòu)件的接大地系統(tǒng)在電氣上相互絕緣,以防止殼體構(gòu)件中的電磁干擾傳導(dǎo)到設(shè)備中去。但是,由于設(shè)備不與公共地相連,故懸浮接地容易在兩者之間造成靜電積累,當(dāng)電荷積累到一定程度后,在設(shè)備與公共地之間的電位差可能引起劇烈的靜電放電,產(chǎn)生干擾放電電流。懸浮接地不適用于通信系統(tǒng)中。

了解了以上的內(nèi)容,那么在實(shí)際的BCB板的印刷中,要以上面的理論依據(jù)為基礎(chǔ)對(duì)地線進(jìn)行合理布局。在對(duì)地線布局時(shí),通常要注意以下幾點(diǎn):

一、數(shù)字地與模擬地要分開;

二、數(shù)字電路地線不要構(gòu)成閉合環(huán)路;

三、多層PCB中,盡量將地線層和電源層放置在相鄰的層中;

四、地線、電源線和信號(hào)線寬度設(shè)計(jì)要合理。

以上這些注意點(diǎn),要在實(shí)際操作中慢慢研究體會(huì)。

在進(jìn)行高速電路設(shè)計(jì)時(shí),合理的接地設(shè)計(jì)是最有效的電磁兼容設(shè)計(jì)技術(shù)。據(jù)統(tǒng)計(jì),90%的電磁兼容問題是由于布線和接地不當(dāng)造成的。好的布線和接地既能夠提高抗擾度,又能減小干擾發(fā)射,同時(shí)也有可能再成本較低的情況下解決許多電磁干擾問題,所以在進(jìn)行高速電路的PCB板設(shè)計(jì)時(shí),合理的設(shè)計(jì)接地至關(guān)重要。

一般提倡電源和信號(hào)電流最好通過“接地層”返回,而且該層還可為轉(zhuǎn)換器、基準(zhǔn)電壓源和其它子電路提供參考節(jié)點(diǎn)。但是,即便廣泛使用接地層也不能保證交流電路具有高質(zhì)量接地參考。

圖 1所示為簡(jiǎn)單電路采用兩層印刷電路板制造,頂層上有一個(gè)交直流電流源,其一端連到過孔 1,另一端通過一條 U 形銅走線連到過孔 2。兩個(gè)過孔均穿過電路板并連到接地層。理想情況下,阻抗為 0,電流源上的電壓為 0 V。

圖 1. 電流源的原理圖和布局,PC板上布設(shè)U形走線,通過接地層返回。

這個(gè)簡(jiǎn)單的原理圖遠(yuǎn)不能反映真實(shí)的情況,但了解電流如何在接地層中從過孔 1 流到過孔 2,將有助于我們看清實(shí)際問題所在,并找到消除高頻布局接地噪聲的方法。

電感與電流環(huán)路的面積成比例,二者之間的關(guān)系可以用圖 2 所示的右手法則和磁場(chǎng)來(lái)說明。環(huán)路之內(nèi),沿著環(huán)路所有部分流動(dòng)的電流所產(chǎn)生的磁場(chǎng)相互增強(qiáng)。環(huán)路之外,不同部分所產(chǎn)生的磁場(chǎng)相互削弱。因此,磁場(chǎng)原則上被限制在環(huán)路以內(nèi)。環(huán)路越大則電感越大,這意味著:對(duì)于給定的電流水平,它儲(chǔ)存的磁能更多,阻抗更高,因而將在給定頻率產(chǎn)生更大電壓。

圖2. 磁力線和感性環(huán)路

在圖中所示的簡(jiǎn)單例子中,面積最小的環(huán)路顯然是由 U 形頂部走線與其正下方的接地層部分所形成的環(huán)路。圖 3(左)則顯示了大多數(shù)交流電流在接地層中選取的路徑,它所圍成的面積最小,位于 U 形頂部導(dǎo)線正下方。實(shí)際應(yīng)用中,接地層電阻會(huì)導(dǎo)致低中頻電流流向直接返回路徑與頂部導(dǎo)線正下方之間的某處(右圖)。不過,即使頻率低至 1-2 MHz,返回路徑也是接近頂部走線的下方。

圖 3. 接地層中不含(左圖)和含(右圖)電阻的交流電流路徑

如何避免布局問題?一旦了解電流在接地層中的返回路徑,就可以找出并糾正常見布局問題。例如在圖4 中,路徑 A 被認(rèn)定是關(guān)鍵路徑,應(yīng)當(dāng)保持最短,遠(yuǎn)離數(shù)字線路,并且不得有過孔。路徑 B 不那么重要,但需要穿過路徑 A。通常是切開路徑 A 下面的接地層,然后經(jīng)過兩個(gè)過孔并在路徑 A 下方布設(shè)路徑 B。

圖4. 路徑交叉時(shí)的典型 PCB 布局問題

但結(jié)果令人遺憾,兩個(gè)信號(hào)的接地回路中均引入了電感,因?yàn)橹袛嗟慕拥貙邮箖蓷l環(huán)路的面積均變得更大。路徑 A 傳導(dǎo)高頻信號(hào),因此接地層的開口上將出現(xiàn)感應(yīng)壓降。對(duì)于典型的 ECL或 TTL 信號(hào),此壓降可能大于數(shù)百毫伏,足以嚴(yán)重影響 12 位、10 MHz 轉(zhuǎn)換器或 8 位、20-MHz 轉(zhuǎn)換器的性能。簡(jiǎn)單的補(bǔ)救方法是在接地層的切口上添加一根導(dǎo)線,使環(huán)路面積保持較小。

電源干擾是另一個(gè)值得關(guān)注的問題。電源線的特性阻抗必須盡可能低。為使此比值較小,需要使接地層始終位于電源線下方,以便降低電感并提高電容。有選擇地將旁路電容放在關(guān)鍵位置上,可以進(jìn)一步提高電容。如果只顧及到電容,例如將 0.1 μF 電容放在電源引腳上以降低其阻抗,則電感為 30 nH 的電源線在每次瞬變之后將具有大約 3MHz 的阻尼振蕩。

fqj

-

電感

+關(guān)注

關(guān)注

54文章

6265瀏覽量

106442 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1651瀏覽量

83345

發(fā)布評(píng)論請(qǐng)先 登錄

PCB接地設(shè)計(jì)實(shí)戰(zhàn)避坑指南:從“環(huán)路”到“干凈地”的進(jìn)階之路

解析ISO72x系列單通道高速數(shù)字隔離器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

ISO776x系列高速六通道數(shù)字隔離器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

CDx4HC251和CDx4HCT251高速CMOS 8輸入多路復(fù)用器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

高速比較器 LT1016:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

DLP5500數(shù)字微鏡器件:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

PCB設(shè)計(jì)中單點(diǎn)接地與多點(diǎn)接地的區(qū)別與設(shè)計(jì)要點(diǎn)

關(guān)于高速數(shù)字電路“接地”要點(diǎn)的詳細(xì)介紹

關(guān)于高速數(shù)字電路“接地”要點(diǎn)的詳細(xì)介紹

評(píng)論