ASIC設(shè)計的“四大神器”,折疊(Fold ),展開(Expand),重定時(Retiming),資源共享(Resource Sharing) 。

折疊&展開

Fold & Expand,折疊和展開

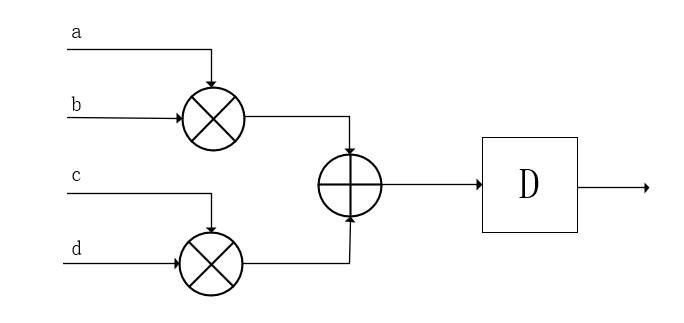

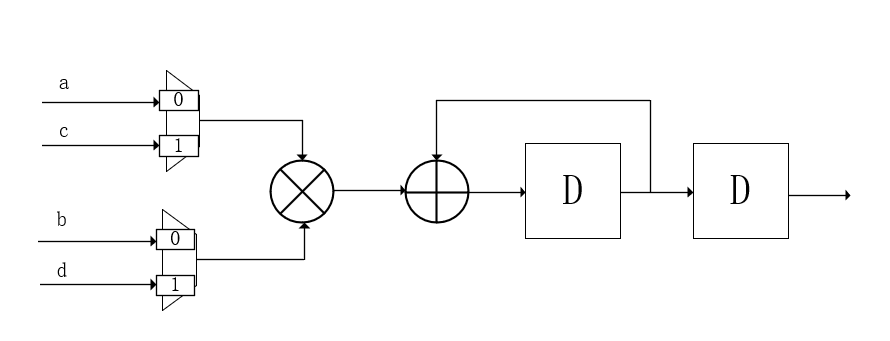

一拍得出結(jié)果,使用了兩個乘法器,面積大,速度快。

兩拍得出結(jié)果,使用了1個乘法器,面積小,速度慢。

這個過程就叫做折疊,展開可以看作是折疊的逆操作,在實際工程中,我們根據(jù)需求適當(dāng)?shù)氖褂眠@個兩個技術(shù),實現(xiàn)設(shè)計最優(yōu)化。

提高速度和降低面積是兩個矛盾的目標(biāo),所以在具體的設(shè)計中要折中(Trade-off),一個好的設(shè)計追求的極致是讓乘法器等占用面積大的邏輯盡量不要空閑。高度復(fù)用。

重定時

筆試題中常有問,什么是Retiming技術(shù)?

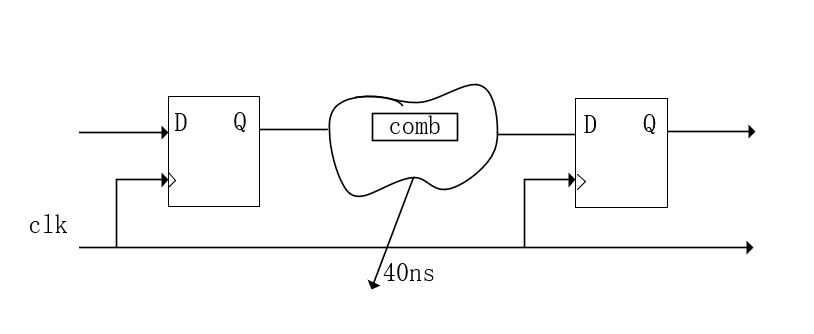

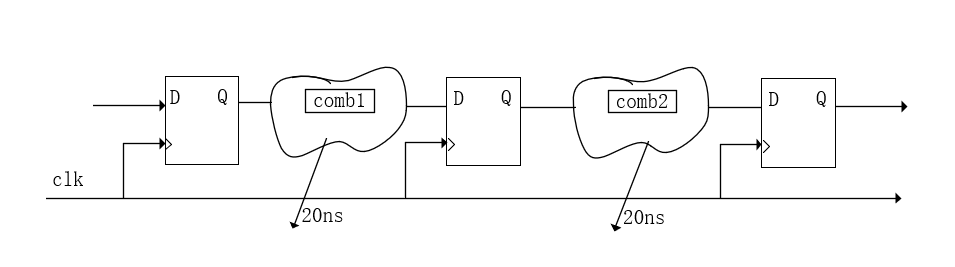

Retiming就是重新調(diào)整時序,例如電路中遇到復(fù)雜的組合邏輯,延遲過大,電路時序不滿足,這個時候采用流水線技術(shù),在組合邏輯中插入寄存器加流水線,進(jìn)行操作,面積換速度思想。

我們知道任何的數(shù)字電路都可以等效成組合邏輯加D觸發(fā)器打拍,兩個D觸發(fā)器之間的組合邏輯路徑?jīng)Q定了,系統(tǒng)的工作頻率,決定芯片的性能。所以為了提高芯片的工作頻率,使用流水線技術(shù)在組合邏輯中插入寄存器。

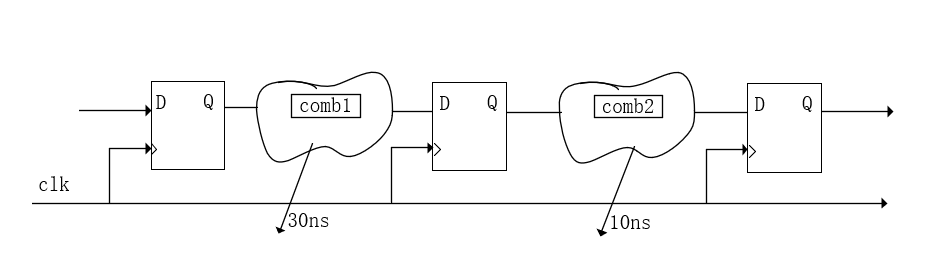

插入寄存器的位置需要慎重選擇,不同的位置數(shù)據(jù)的打拍所消耗的寄存器的數(shù)量也不同,比方說你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省則省。

前面插入寄存器的位置使得comb1的延遲為30ns,comb2的延遲為10ns,系統(tǒng)的最高工作頻率是由最長路徑?jīng)Q定的。也就是說你這個系統(tǒng)最高工作頻率的周期,不小于30ns,前面是插入pipeline,這個時候我們不改變時序,采用重定時技術(shù),使得各個組合邏輯之間的延遲相當(dāng)。

資源共享

從設(shè)計的角度來說,最常見的就是計數(shù)器,能用一個計數(shù)器實現(xiàn)的,就別用倆,底層模塊之間相同的邏輯盡量使用一塊電路,減少重復(fù)的設(shè)計。

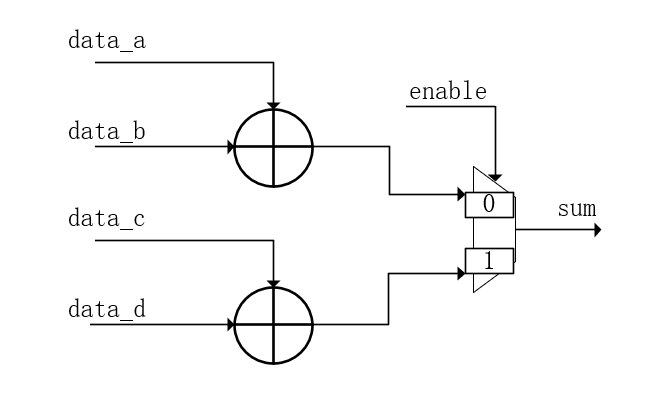

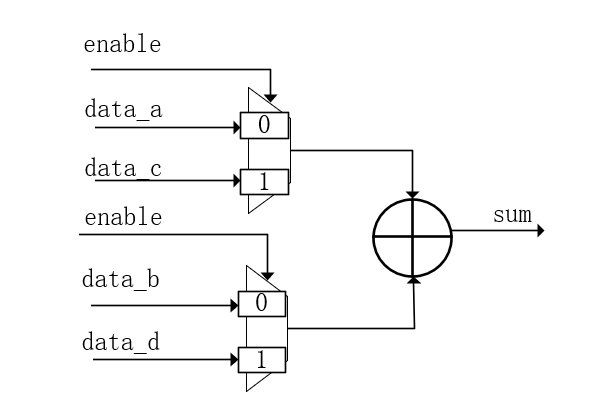

基本邏輯單元的共享舉例,面積:加法器 > 比較器 > 選擇器。俗稱加比選。

乘法器本質(zhì)上也是全加器。

所以就有先選后比,先選后加,先選后乘。

畫個圖意思一下。

最基本的層次共享是基于基本元器件的共享,綜合工具能做較多的自動優(yōu)化,在布局布線時還能進(jìn)一步提高資源利用率,通常情況下是在同一模塊內(nèi)進(jìn)行優(yōu)化,但如果你的工具足夠強大,則可以打破模塊邊界進(jìn)行優(yōu)化。像很多模塊被打散揉在一起布線是可能的,從后端看也看不到模塊邊界。工具的布線優(yōu)化人工都很難干預(yù)。

最后

以上是從基本電路設(shè)計的角度上和數(shù)據(jù)通路上進(jìn)行歸類,控制邏輯的話,簡單來說一個字,狀態(tài)機大法好。這個問題我們下次再聊。

責(zé)任編輯:lq

-

asic

+關(guān)注

關(guān)注

34文章

1274瀏覽量

124593 -

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

129998

原文標(biāo)題:干貨 | ASIC設(shè)計之“四大神器”

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

什么是OVP芯片?深度解析DC9336V過壓保護(hù)的四大核心技術(shù)原理

淺談SOI晶圓制造技術(shù)的四大成熟工藝體系

后摩智能六篇論文入選四大國際頂會

和而泰發(fā)布四大自研核心技術(shù)平臺

星海SSxx系列肖特基二極管技術(shù)解析:四大封裝的參數(shù)特性與場景適配

匯川技術(shù)四大架構(gòu)重磅發(fā)布

空氣是如何“鉆空子”的?壓鑄件氣密檢測泄漏的四大元兇

AI芯片,需要ASIC

四大核心要素驅(qū)動汽車智能化創(chuàng)新與相關(guān)芯片競爭格局

英飛凌碳化硅產(chǎn)品創(chuàng)新的四大支柱綜述(二)

慕尼黑上海電子展上,村田中國展示四大前沿創(chuàng)新

助焊劑四大功能及特性

無線傳輸中的四大“隱形指揮官”:頻段、功率、靈敏度和空速

ASIC設(shè)計的“四大神器”

ASIC設(shè)計的“四大神器”

評論