隨著現場可編程門陣列(FPGA)已發展成為真正的可編程系統級芯片,利用這些芯片設計印制電路板(PCB)的任務變得愈加復雜。目前動輒數百萬門的電路密度和6Gbps以上的收發器數據傳輸率及其它考慮事項影響著系統開發人員在機械和電氣方面的板級設計工作。裸片、芯片封裝和電路板構成了一個緊密連接的系統,在這個系統中,要完全實現FPGA的功能,需要對PCB板進行精心設計。

采用高速FPGA進行設計時,在板開發之前和開發期間對若干設計問題進行考慮是十分重要的。其中包括:通過濾波和在PCB板上的所有器件上均勻分配足夠功率來減小系統噪聲;正確連接信號線,以把反射減少;把板上跡線之間的串擾降至;減小接地反彈和Vcc降低(也稱為Vcc凹陷)的影響;正確匹配高速信號線上的阻抗。

任何人在為性能極高的FPGA設計IC封裝時,都必須特別注意信號完整性和適于所有用戶和應用的多功能性之間的平衡問題。例如,Altera的Stratix II GX器件采用1,508引腳封裝,工作電壓低至1.2V,并具有734個標準I/O、71個低壓差分信令(LVDS)信道。它還有20個高速收發器,支持高達6.375Gbps的數據率。這就讓該架構能夠支持許多高速網絡和通信總線標準,包括PCI Express和SerialLite II。

在設計中,用戶可以通過優化引腳排列來減少串擾。信號引腳應該盡可能靠近接地引腳,以縮短封裝內的環路長度,尤其是重要的高速I/O。在高速系統中,主要的串擾源是封裝內信號路徑之間的電感耦合。當輸出轉換時,信號必須找到通過電源/接地平面的返回路徑。環路中的電流變化產生磁場,從而在環路附近的其它I/O引腳上引起噪聲。同時轉換輸出時,這種情形加劇。因為環路越小,感應就越小,故電源或接地引腳靠近每個高速信號引腳的封裝可以把附近I/O引腳上的串擾影響減至。

為了把電路板成本降至,并把所有信號路徑的系統信號完整性提高到,需要對電路板材料、分層數目(堆疊)和版圖進行精心的設計和構建。把數百個信號從FPGA發送到板上或其周圍是一個很困難的任務,需要使用EDA工具來優化引腳的排列和芯片的布局。有時采用稍微大點的FPGA封裝能夠降低板成本,因為它可以減少電路板的層數及其它的板加工限制。

PCB板上的一條高速信號路徑,由一條板上跡線代表,其對中斷非常敏感,如電路板層和電路板連接器之間的通孔。這些及其它中斷都會降低信號的邊緣速率,造成反射。因此,設計人員應該避免通孔和通孔根(via stub)。如果通孔是不可避免的,應讓通孔引線盡可能地短。對差分信號進行布線時,讓差分對的每一條路徑使用一個相同結構的通孔;這就讓通孔引起的信號中斷處于共模中。如果可能的話,在常規通孔處使用盲孔。或使用反鉆,因為通孔根的損耗導致的中斷會更少。

為了改善時鐘信號的信號完整性,應該遵循以下原則:

在時鐘信號被發送到板上元件之前,盡可能將之保持在單個板層上;始終以一個平面作為參考面。

沿鄰近接地平面的內層發送快速邊緣信號,以控制阻抗,減小電磁干擾。

責任編輯:lq

-

FPGA

+關注

關注

1660文章

22415瀏覽量

636496 -

pcb

+關注

關注

4406文章

23882瀏覽量

424425 -

電路板

+關注

關注

140文章

5317瀏覽量

108230

原文標題:利用高速FPGA設計PCB的要點及相關指導原則

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電子工程師設計相關要點與案例分析

PCB拼板三大細節要點

ADC模數轉換實戰:硬件設計與軟件開發要點指南!

從入門到精通:PCB設計必須遵守的5大核心原則

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

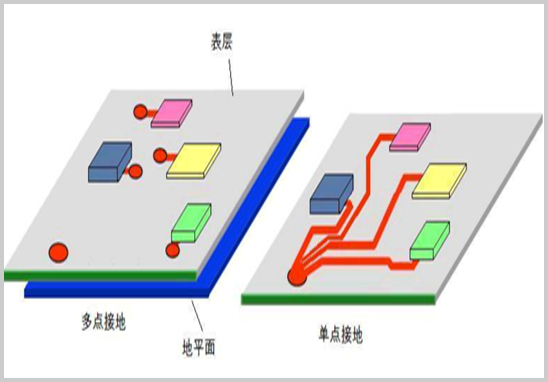

PCB設計中單點接地與多點接地的區別與設計要點

利用高速FPGA設計PCB的要點及相關指導原則

利用高速FPGA設計PCB的要點及相關指導原則

評論