做過layout的朋友一定會有一種這樣的感覺,串行通道恐怕是最容易設(shè)計的部分了。通道就一對差分線,芯片端串行部分信號pin的密度都相對低,出線也十分簡單,最多在通道上有一對AC耦合電容,有些廠商甚至已經(jīng)將電容集成在芯片中了。

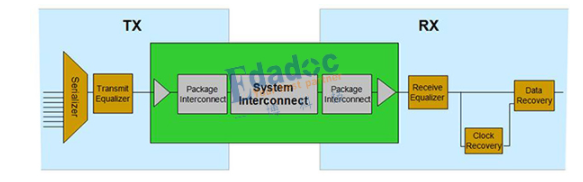

和所有的互聯(lián)結(jié)構(gòu)一樣,SERDES無非也就是輸出,輸入,與互連通道。

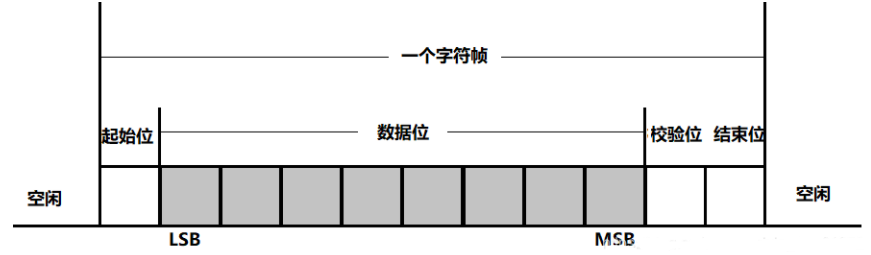

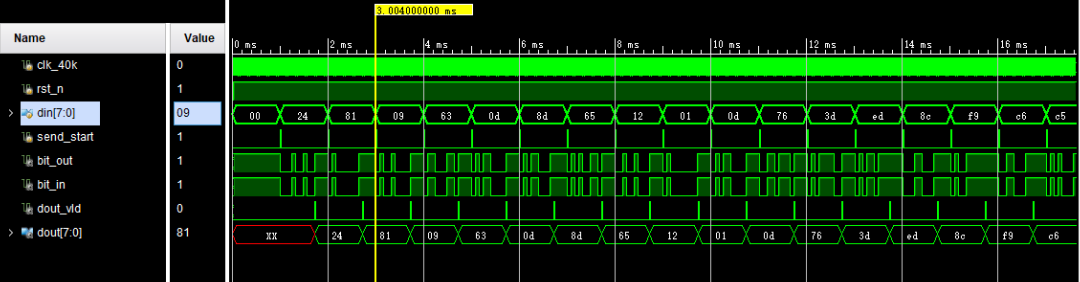

不過,SERDES在芯片端比一般的信號要多出一些東西。首先,需要在TX端完成將并行信號變成串行信號過程,該過程通過串行器來實現(xiàn),將n個速率為x的并行信號,變成一個速率為n*x的串行信號,這樣在1/x的時間內(nèi),串行信號就包含了n個信息。在這個過程中,參考時鐘的質(zhì)量就至關(guān)重要了,我想,誰都不愿意看到在并行信號中地位相同的兩個信號,變成串行信號之后一個占150ps一個卻只有50ps了吧。

當(dāng)然,為了保證信號的直流平衡(不要有長0長1的出現(xiàn))等性能,在將數(shù)據(jù)進行串并轉(zhuǎn)換之前,會將信號進行編碼。在數(shù)據(jù)串化之后,會經(jīng)過預(yù)加重模塊,再出芯片,來到我們的信道上。

簡單來說TX就是一個編碼》》串化》》預(yù)加重》》輸出的過程。

而通道上,就是我們熟悉走線,過孔,連接器了。這些在之后的文章中做具體說明。

這里還有一個容易被大家忽略的東西,就是器件的封裝。雖然很多協(xié)議對通道的要求是并不包含芯片封裝的,但是一個好的芯片封裝可以為通道增加非常多的裕量,這也是為什么很多通道性能并不是很好但是芯片工作起來非常順暢的原因之一。同樣是BGA封裝,flip chip的寄生電感是wire bonding的30%。當(dāng)然,更好的性能自然意味著更高的成本,just you know。

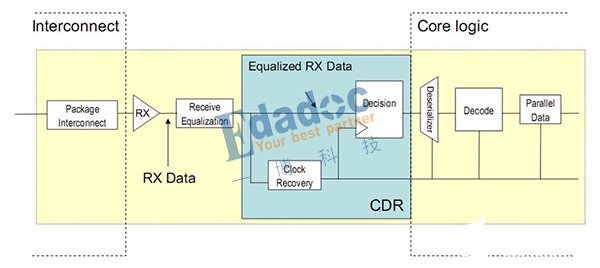

在串行通道的RX端,進行著與TX相反的過程。首先經(jīng)過一個均衡器,將信號進行均衡處理。再通過CDR(clock data recovery)將串行信號解串為并行信號。

大道至簡。可是在這至簡的大道背后,各位工程師們可是在編碼,均衡,封裝等地方做了非常多的努力呢。

編輯:hfy

-

Layout

+關(guān)注

關(guān)注

15文章

424瀏覽量

75383 -

并行信號

+關(guān)注

關(guān)注

0文章

6瀏覽量

7336 -

SerDes

+關(guān)注

關(guān)注

8文章

236瀏覽量

36962 -

串行信號

+關(guān)注

關(guān)注

0文章

30瀏覽量

8762 -

耦合電容

+關(guān)注

關(guān)注

2文章

157瀏覽量

20836

發(fā)布評論請先 登錄

常用串行總線(一)——UART協(xié)議(Verilog實現(xiàn))

串行通訊與并行通訊介紹

串行lvds數(shù)據(jù)轉(zhuǎn)并行TTL數(shù)據(jù)

串行和并行的區(qū)別

串行和并行的區(qū)別

請問2.8寸LCD屏能改成串行的嗎?

并行與串行有什么區(qū)別

串行信號和并行信號有什么優(yōu)缺點?

串行通訊與并行通信數(shù)字信號的相關(guān)資料分享

串行口通信原理及操作

我們該“串行”還是“并行”?

什么是串行總線和并行總線?

解析常用串行總線——UART協(xié)議(上)

解析常用串行總線——UART協(xié)議(下)

串行系列:并行信號變成串行信號過程

串行系列:并行信號變成串行信號過程

評論