設計用于網絡應用程序的ASIC面臨著獨特的挑戰。一是這些設備的帶寬和延遲性能測試需要比其他類型的IC所需的仿真周期大得多的仿真周期。當然,擴展的模擬會減慢整個設計過程。為了解決這些以及其他問題,思科工程師采用了將仿真與仿真相結合的做法,以改善和加速驗證過程。

過去,思科會為每個新的IC追求獨特的驗證機制。為了節省工作量和時間,該公司與其工具供應商Mentor Graphics合作,對可應用于多種設計的方法進行了標準化。

思科系統公司Core ASIC Group的驗證經理Afzal Malik說:“向現成的仿真產品遷移非常有益,特別是大型芯片和系統的出現。”Malik參與了針對企業和園區交換網絡的專用集成電路(ASIC)系列的仿真,Catalyst 9000系列是思科最成功的產品系列之一。

Malik的小組使用仿真來針對難以發現的深度循環漏洞。沒有仿真,這些類型的錯誤最終會在硅片中實現,而修復它們的成本非常高。該小組設定的目標是通過仿真來檢測所有錯誤,在正式發布之前將正式的驗證仿真和硬件仿真相結合,從而達到100%的覆蓋率。達到這些目標將縮短產品上市時間。

挑戰僅始于帶寬和等待時間性能測試,這些測試需要如此長的仿真運行時間。由于過多的構建和運行時間,因此很難在仿真中測試復雜系統中的多芯片交互。隨著接口不斷發展,設計驗證小組花時間開發驅動程序和監視器。某些網絡協議(例如PTP 1588和鏈接暫停和優先級流控制(PFC))需要大量仿真,并且運行時間很長才能達到穩定狀態。

網絡ASIC通常是大型設計,這意味著代碼覆蓋和功能覆蓋需要更多時間。此外,對最新網絡標準的驗證要求增強測試平臺組件。最后的挑戰是硬件/軟件的協同驗證,這涉及在磁帶輸出之前在硬件上運行實際的軟件。

Malik指出,仿真對于塊級驗證和基本集成測試是不可替代的,但是隨著設計尺寸的增加,仿真性能會下降,尤其是在使用多個ASIC的系統上。為了克服挑戰,僅憑仿真是不夠的。

與驗證過程相關的一些術語應在此處定義。后門初始化和前門初始化是指如何從內存中加載或提取內容。前門流程意味著設計本身用于將數據移入和移出內存。后門流程是測試平臺或軟件在不使用設計的情況下將數據移入和移出內存的一種方式。測試工程師經常想預加載內存內容,或者在測試運行結束時或在測試過程中途從內存中提取數據,而后門訪問通常用于這種類型的內存加載或提取。

Malik報告說,他的小組在90%以上的測試中使用后門初始化模擬。模擬不是前門驗證的理想解決方案。當軟件配置ASIC并運行生產軟件時,前門初始化成為必要條件。

為了應對挑戰,思科的設計驗證工程師針對這種ASIC設計引入了Mentor Graphics的Veloce2仿真器。仿真的運行速度比仿真快一千倍,并且其運行時性能不會隨著設計尺寸的增加而降低。

與FPGA系統不同,基于Veloce的仿真環境提供了完整的調試可見性。編譯和運行步驟與模擬相似,因此易于使用。Malik指出,例如,可以在仿真中重用各種各樣的驗證組件,尤其是記分板,檢查器和功能覆蓋點。

該小組使用仿真技術進行設計培訓。馬利克(Malik)確認,即使在仿真中進行多單元級驗證也是在芯片級獲得前幾個數據包的良好起點。

仿真不僅可以幫助您發現深層的漏洞,而這些漏洞本來就很費時間進行檢測,但它還可以幫助您執行真正的軟件,在芯片上運行性能測試以及進行系統級驗證。對于線速測試,流量控制和Internet混合(IMIX)測試,仿真也很方便。在仿真中可以有效地執行暫停測試,數據路徑測試和負載平衡。

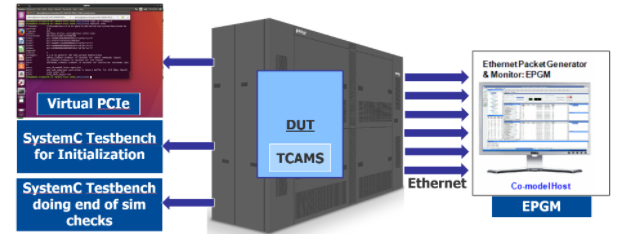

軟件和硬件團隊都使用Cisco的ASIC驗證環境。虛擬PCIe接口(左)通常供軟件團隊在通過標準PCIe接口與交換ASIC進行通信的控制平面上引導其OS或內核。從軟件的角度來看,軟件團隊的運作就像在使用ASIC一樣。但是,設計本身在仿真器中。資料來源:思科

對于功能驗證,思科做了兩件事。它為前門初始化設計了一個測試平臺。它進行了所有C ++ / System C測試檢查器和模擬檢查,甚至是實時檢查,并將其移植到仿真器上。它還使用Mentor的以太網數據包生成器監視器(EPGM)作為生成以太網數據包或不同類型數據包的IP。

思科提出設計的步驟包括:

標識設計中未仿真的部分,例如,測試設計(DFT)邏輯。有些問題可能會導致捆綁,導致編譯器在編譯仿真器設計時將其刪除。

Testbench問題包括:

- 創建一個對Veloce友好的事務處理程序以配置ASIC

- 部署EPGM以發送和分析以太網數據包

- 在SystemC和C ++中創建模擬檢查結束

- 綜合仿真器的功能范圍

設計調試的主要功能包括:

- EPGM分析窗口

- 觸發交易器以捕獲波形

- 其他自定義觸發波形生成

硬件實現的斷言和它們可以生成的監視器(這些關鍵斷言是觸發的異常,可以自動生成用于調試的波形。)

完整的波形上傳

思科與Mentor共同開發了EPGM,這是一種用于聯網ASIC的虛擬解決方案,為期數年。它支持多核模型并擴展性能。它具有基于TCL的界面,可以相當快速地編寫復雜的測試用例,并具有預置的觸發器來捕獲波形。可變端口組是最近增加的一種超級端口模式,它允許單個構建支持多種端口模式,而不是針對芯片的可能配置進行多次構建。

在調試分析方面,Cisco獲取每流統計信息,例如帶寬/等待時間/總幀數,所有錯誤-不按順序,CRC和前導錯誤-由EPGM捕獲并報告。此外,該小組在ASIC內實現了自定義檢查程序和費率監視器。

關于加速的結果可能會有所不同,具體取決于ASIC和應用程序的大小。在前門中,通過仿真進行初始化大約需要6,000分鐘。在仿真中,該小組將時間縮短到30分鐘–在這些復雜的ASIC上進行了數以萬計的前門寫操作。通過使用Mentor的入站流進行新的優化流程,Malik的團隊將其縮減到不到五分鐘的時間,而前門初始化只需幾分鐘。僅使用模擬,該過程通常需要幾天的時間。

借助給定配置的運行時性能,Cisco可以在仿真中每分鐘處理40個數據包,而在仿真中則可以每分鐘處理60萬個數據包。比仿真高15,000倍!

馬利克指出,所描述的方法不是專有的。他說:“這是我們對Mentor Strato解決方案所提供功能的實現。”

現在,Malik和他的團隊是經驗豐富的仿真用戶,他們計劃將其用于其他驗證任務。硅前軟件開發,多芯片系統驗證,硅就緒性和硅前功率分析是您關注的幾個領域。例如,在進行硅前軟件開發期間,他們可以啟動控制平面OS,并在磁帶輸出之前在實際的ASIC上運行應用程序。該領域是有益的,尤其是對于診斷和系統軟件團隊而言。

Malik的團隊也希望在軟件開發領域進行投資,以證明其在仿真方面所做的努力是合理的。對于Malik及其團隊而言,在磁帶發布之前開發和驗證診斷軟件非常重要。使用實際系統軟件的新驗證功能也需要在流片之前在硬件中進行驗證。診斷,內核和應用程序軟件團隊現在可以開始調試,并在仿真平臺上迅速提高速度。

多芯片驗證仍然是另一個領域。思科的系統很復雜–模塊化系統具有管理卡和帶有多個ASIC相互通信的線卡。這些都是可擴展的系統,嘗試在仿真中驗證它們是一個挑戰。

硅長大和準備就緒是另一種可能的應用。當芯片返回時,該小組將進行測試和ASIC認證以進行芯片驗證。當芯片回到實驗室時,仿真將為您提供領先優勢。硅前功率分析,Mentor支持的領域以及Veloce用戶Cisco的領域正在積極調查中。

Malik已經為思科的驗證流程展望了未來,該流程將統一用于回歸和覆蓋范圍分析。這種流程需要對標準功能覆蓋流程進行一些更改,在這些功能中,需要在設計內部合成和映射覆蓋范圍。功率分析是一個正在積極研究的領域,高級趨勢和分析功能也正在將其納入流程。當然,為了提高性能,正在對流程進行逐步改進。

總而言之,Malik保持的仿真幫助思科設計驗證小組達到了確定其ASIC所需的高度信心。使軟件準備好用于硅啟動是一個很大的好處。仿真通常有助于將產品推向市場的時間左移。

Malik總結說,仿真是整體驗證策略的重要補充。快速啟動,成熟的編譯和全面的可見性是關鍵。盡管正在開發出色的技術,但沒有什么可以像仿真那樣提供完整的可見性和完整的調試的。

Lauro Rizzatti博士是硬件仿真方面的驗證顧問和行業專家。

編輯:hfy

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636344 -

asic

+關注

關注

34文章

1274瀏覽量

124593 -

仿真器

+關注

關注

14文章

1051瀏覽量

87277

發布評論請先 登錄

電源模塊的可靠性設計有何秘籍?

如何去實現一種基于SoPC的軟硬件協同設計呢

orcad仿真教程

網絡仿真與OPNET簡介

基于FPGA的模糊CMAC網絡的硬件實現

【應用方案】仿真對比設計一款LED驅動電源8顆LED燈珠電路

所能預見的硬件仿真未來

硬件仿真對網絡設計有何影響?

硬件仿真對網絡設計有何影響?

評論