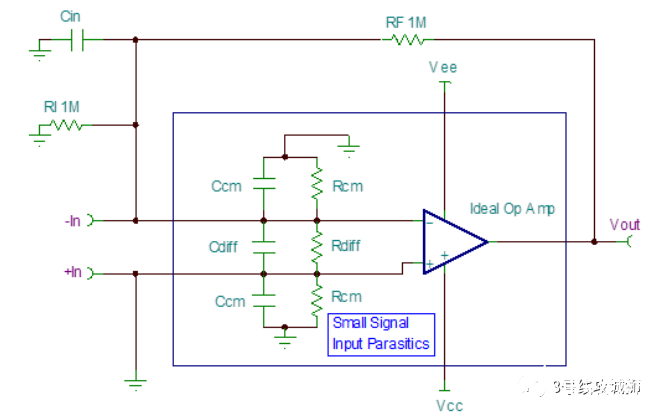

下圖 1 形象的說明了運放的輸入端阻抗的特性。主要有兩個參數,輸入阻抗和輸入電容。對于電壓反饋型運入,輸入阻抗主要由輸入級的決定,一般BJT輸入級的運放。的共模輸入阻抗會大于40MΩ。差模輸入阻抗大于200GΩ。對于JFET和CMOS輸入級的運放,輸入阻抗要大的多。這個阻抗通常表現為電阻性。作為常識被我們所熟知。

圖 1 運放輸入端阻抗特性

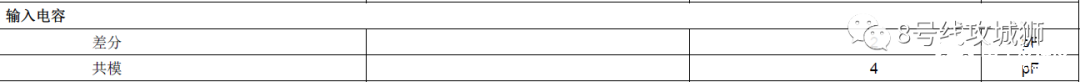

更值得我們多加關注的是運放的輸入電容。這個參數通常在datasheet的表格中所列出,但常被忽視。運放的輸入電容,通常分為共模輸入電容Ccm和差模輸入電容Cdiff。如下圖 2 是OPA333的datasheet中列出的輸入電容。

圖 2 OPA333的輸入電容

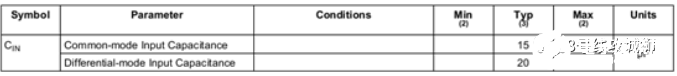

對于有EMI抑制特性的運放,如LMV832,它的輸入電容會被設計的正大的些。下圖 3 是帶EMI抑制功能的LMV832的輸入電容值。

圖 3

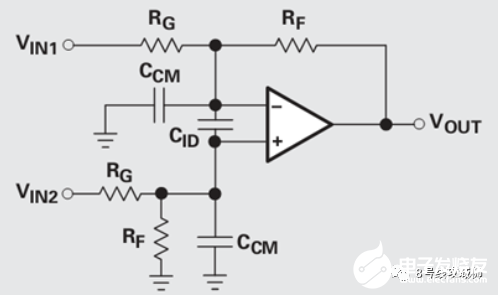

運放的輸入共模電容Ccm 和差模電容 Cdiff會形成運放的輸入電容 Cin。在許多應用中,運算放大器的輸入電容都不會造成問題。但在某些應用中會引起放大電路的不穩定。尤其是反向輸入端的電容,是放大電路不穩定的幾大罪魁禍首之一。如下圖 4 所示是運放在有輸入電容的影響下的模型。

圖 4 等效模型

這個反向輸入端的電容會在運放的環路增益中引入一個極點。正是這個極點的存在,在某些條件下,可能會引起放大電路的不穩定。

運放輸入電容引入的極點如下式。即使這個極點0-dB交截越頻率之內,而是非常靠近0-dB交越頻率,它也有可能引起問題。在這個極點的頻率點上,相位會有45度的相位延遲,它很可能減少放大電路的相位裕度。如放大電路的0-dB交截越頻率是2MHz。在2MHz處的相位裕度是89°。如果這個極點的頻率點也在2MHz處,它將使相位裕度減少45°。而變為φ = 89° – 45° = 44°。44度的相位裕度就顯得的不夠了。

通常放大電路的輸入電容不只由運放的輸入電容組成,還包括布線引起的雜散電容和引腳電容。應盡量避免運算放大器反相輸入端存在外部雜散電容,尤其是在高速應用中。反相輸入周圍區域應去除接地層,從而最大程度地減小PC板雜散電容,此外,該引腳的所有連接都應盡量短。

在一些應用,常會加入反饋電容來增加放大電路的穩定,加入反饋電容后的電路的環路增益為,可見反饋補償電容給環路增益中引入了一個零點。

責任編輯:haq

-

電路

+關注

關注

173文章

6083瀏覽量

178691 -

電容

+關注

關注

100文章

6502瀏覽量

159843 -

阻抗

+關注

關注

17文章

990瀏覽量

49412

發布評論請先 登錄

探索AD8244:高精度、低功耗四通道FET輸入緩沖器的卓越性能

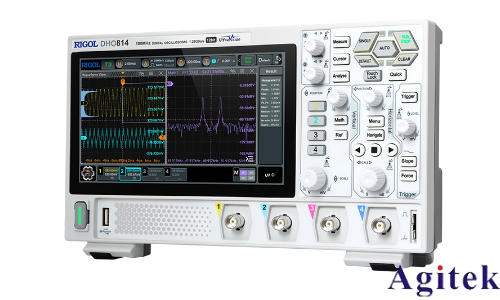

普源示波器DHO824輸入阻抗設置:精準測量的關鍵步驟與實戰技巧

示波器探頭1MΩ和50Ω輸入阻抗的選用

100MΩ輸入阻抗示波器探頭技術特性及應用解析

普源示波器DHO824輸入阻抗設置的關鍵步驟技巧

如何計算集成斬波放大器的ADC失調誤差和輸入阻抗?

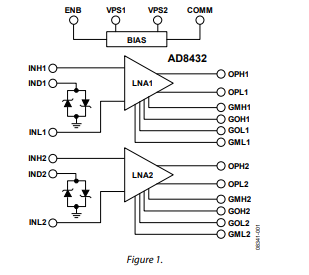

AD8432雙通道超低噪聲放大器,提供可選增益和輸入阻抗技術手冊

輸入阻抗和輸入電容

輸入阻抗和輸入電容

評論