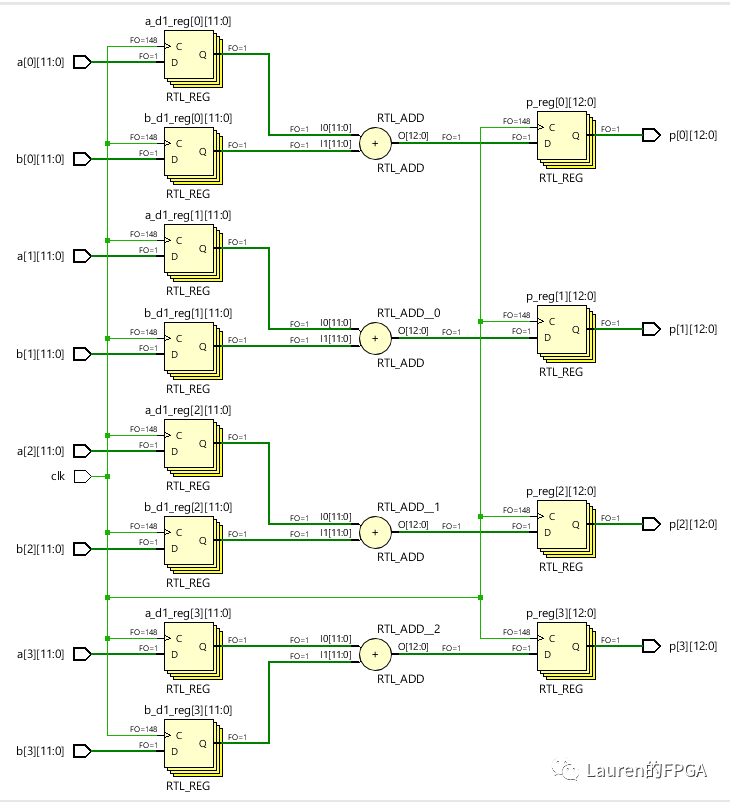

這里并行加法是指多個(gè)加法操作同時(shí)執(zhí)行,這意味著需要消耗多個(gè)加法器。這里我們以4個(gè)12-bit數(shù)相加(加數(shù)和被加數(shù)均為12-bit,故和為13-bit,從而避免了溢出問題)。相應(yīng)的電路圖如下圖所示。圖中的RTL_ADD即為加法器,同時(shí)此電路對(duì)輸入和輸出數(shù)據(jù)均添加了流水寄存器。

此電路對(duì)應(yīng)的RTL代碼如下圖所示,這里我們使用了SystemVerilog來描述。輸入a和b均為4個(gè)12-bit數(shù)據(jù)構(gòu)成的數(shù)組。輸出p也是4個(gè)12-bit構(gòu)成的數(shù)組。代碼第17行至第23行是核心部分,包括了對(duì)輸入、輸出添加流水寄存器和加法操作。

責(zé)任編輯:lq

-

電路圖

+關(guān)注

關(guān)注

10479文章

10755瀏覽量

555235 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

31423 -

數(shù)組

+關(guān)注

關(guān)注

1文章

420瀏覽量

27368

原文標(biāo)題:并行加法的高效實(shí)現(xiàn)

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

并行sram芯片介紹,并行sram芯片應(yīng)用場景

PCA9564:并行總線到I2C總線控制器的卓越之選

探索CD54/74AC283與CD54/74ACT283:高效4位二進(jìn)制加法器的奧秘

解析CD54/74AC283與CD54/74ACT283:4位二進(jìn)制加法器的卓越之選

深入剖析CD54/74AC283與CD54/74ACT283:高性能4位二進(jìn)制加法器

CD54/74AC283與CD54/74ACT283:高性能4位二進(jìn)制加法器的全面解析

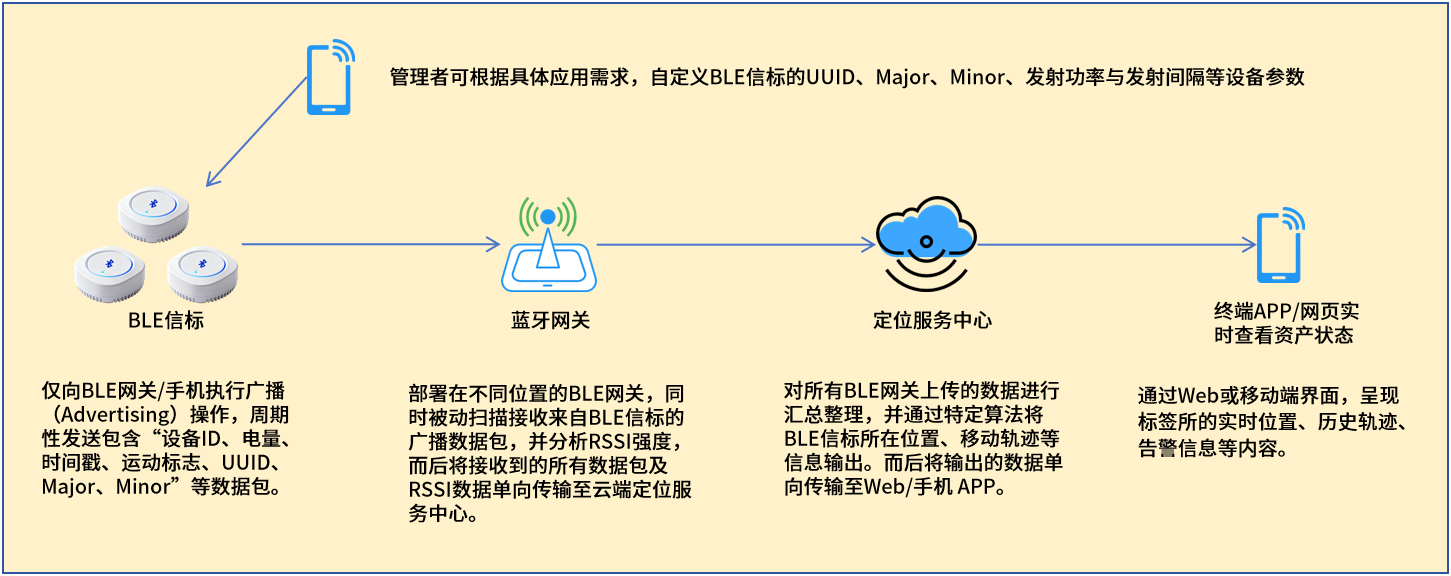

BLE SoC,如何助力管理者實(shí)現(xiàn)高效的資產(chǎn)追蹤?

借助CXL和壓縮技術(shù)實(shí)現(xiàn)高效數(shù)據(jù)傳輸

串行通訊與并行通訊介紹

一文看懂AI大模型的并行訓(xùn)練方式(DP、PP、TP、EP)

TensorRT-LLM的大規(guī)模專家并行架構(gòu)設(shè)計(jì)

EA-BIM 20005:20通道并行EIS測量,讓電池阻抗分析更精準(zhǔn)高效

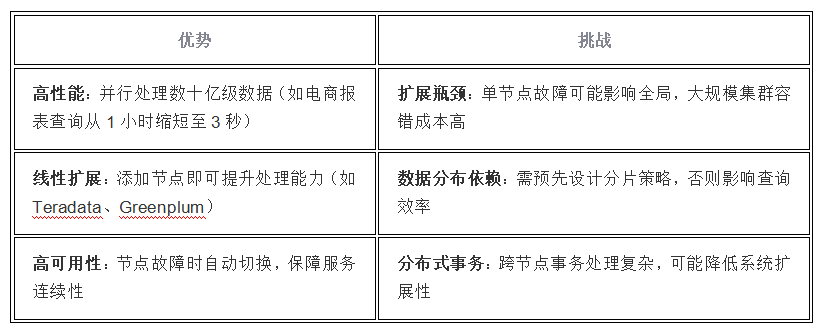

多節(jié)點(diǎn)并行處理架構(gòu)

并行加法的高效實(shí)現(xiàn)

并行加法的高效實(shí)現(xiàn)

評(píng)論