通過對以上電容特性的分析可知,高頻的小電容對瞬間電流的反應最快。例如,一塊IC附近有兩個電容,一個是2.2uF,另一個是0.01uF。當IC同步開關輸出時,瞬間提供電流的肯定是0.01uF的小電容,而2.2uF的電容則會過一段時間才響應,即便小電容離IC遠一些,只要它的寄生電感(包括引線和悍盤電感)比大電容小,那么它依然是瞬間電流的主要提供者。所以,高速設計中的關鍵就是高頻小電容的處理,要盡可能擺放得離芯片電源引腳近一些,以達到最佳的旁路效果。

高速PCB布線中對電容處理的要求,簡單地說就是要降低電感。實際在布局中的具體措施主要有以下6點。

1、減小電容引線/引腳的長度。

2、使用寬的連線。

3、電容盡量靠近器件,并直擬口電源引腳相連。

4、降低電容的高度(使用表貼型電容)。

5、電容之間不要共用過孔,可以考虛打多個過孔接電源/地。

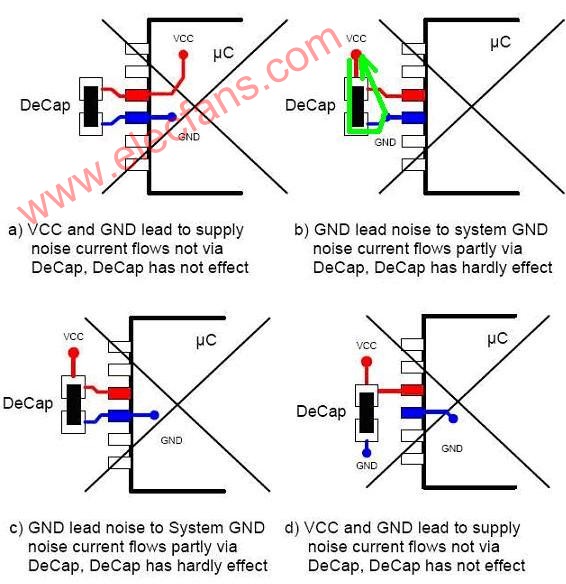

6、電容的過孔盡量靠近焊盤(能打在悍盤上最佳),如圖1-11-21所示。

圖1-11-21電容布局中引線設計趨勢

責任編輯人:CC

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

PCB布線

+關注

關注

22文章

473瀏覽量

43558 -

高速PCB

+關注

關注

4文章

102瀏覽量

25729

發布評論請先 登錄

相關推薦

熱點推薦

提高PCB設備可靠性的具體措施

提高PCB設備可靠性的技術措施:方案選擇、電路設計、電路板設計、結構設計、元器件選用、制作工藝等多方面著手,具體措施如下: (1)簡化方案設計。方案設計時,在確保設備滿足技術、性能指標的前提下,應盡

發表于 09-21 14:49

如何降低PCB互連設計RF效應?

本文將介紹電路板系統的芯片到電路板、PCB板內互連以及PCB與外部器件之間的三類互連設計的各種技巧,包括器件安裝、布線的隔離以及減少引線電感的措施

發表于 09-24 06:25

電網結構優化具體措施有哪些?

瓶頸、消納不足、穩定性弱、經濟性差” 等問題,適配高比例新能源接入與新型電力系統建設需求。具體措施可分為八大核心維度,每個維度均包含可落地的技術或工程手段: 一、輸電網絡優化:強化 “能源主動脈”,適配大規模新能源

電能質量在線監測裝置電源管理優化的具體措施有哪些?

電能質量在線監測裝置電源管理優化的核心是 “ 核心功能不妥協,非核心功能精準控耗 ”,通過硬件選型、軟件邏輯、動態策略三層落地,兼顧功耗降低、實時性保障和穩定性,具體措施如下: 一、硬件層面:從源頭

高速PCB布線降低電感的具體措施

高速PCB布線降低電感的具體措施

評論