當我們啟動Flex Logix時,eFPGA面臨的挑戰是有許多客戶和應用程序,他們似乎都希望eFPGA位于不同的代工廠,不同的節點和不同的陣列大小。每個人都希望eFPGA與在同一節點上的FPGA領導者一樣快且密度高。哦,客戶似乎要等到最后一刻,才需要盡快使用eFPGA。

Xilinx和Altera(現在為Intel PSG)需要大約3年的時間,需要數十或數百個人才能在新的工藝節點中推出新的FPGA系列。Flex Logix如何以更少的團隊開發不到一年的速度和密度的eFPGA?

革命性的FPGA互連

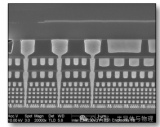

Flex Logix聯合創始人兼高級副總裁程望(Cheng Wang)在加州大學洛杉磯分校(UCLA)攻讀博士學位期間設計了多個復雜度不斷提高的FPGA芯片。在此過程中,他意識到FPGA中使用的傳統網狀互連占據了80%的面積:可編程邏輯僅占20%。因此,他發明了一種新型互連,該互連與網狀結構一樣好,但可以使用一半的晶體管和一半的金屬層來實現!

Cheng,UCLA的Dejan Markovic教授和其他人在ISSCC上發表了有關在他們最終的FPGA項目中使用的這種新互連的論文,并獲得了享有盛譽的杰出論文獎。今天,其中四分之三與Flex Logix有關。

UCLA在互連上申請了專利:Flex Logix是唯一的被許可人。自創立Flex Logix以來,Cheng對互連進行了大量改進,Flex Logix專利涵蓋了這些互連。Flex Logix現在擁有20多項美國已發布專利,這是我們在中國的第一項專利。

我們如何使用專利互連來設計eFPGA

FPGA公司擁有非常龐大的設計團隊,并且需要花費數年的時間,因為他們進行的是全定制設計,這通常保留給包括微處理器在內的超大批量產品使用。

跨多個代工廠和數十個節點需要eFPGA。如果我們每個版本必須雇用50多人,那么eFPGA永遠不會變得經濟或及時可用。

如今,大多數ASIC設計都是使用標準單元完成的:鑄造廠通常免費提供簡單的構建塊,并且已經在工藝,電壓和溫度范圍內進行了表征。可以按照邏輯設計規則組裝標準單元設計,并保證其能正常工作。

但是標準單元設計通常是優化的全定制設計面積的2倍。

FPGA是80%的互連,而Cheng的互連需要?個晶體管。因此,與其使我們的eFPGA變小,不如讓我們的eFPGA全部來自標準單元:使用標準單元增加2倍的面積可以抵消Cheng互連的面積減少50%的影響。因此,在給定的過程節點中,我們最終得到與FPGA領導者相同的密度和性能。

但是,因為我們使用標準單元進行設計,所以從開始之日起不到一年就可以進入市場。并且擁有更小的設計團隊。

因此,如果客戶想要從180nm到5nm的代工廠/節點所需的eFPGA,我們可以在他們的設計進度約束內快速交付。

結論

eFPGA對于加速關鍵工作量并使SoC適應不斷變化的算法和協議非常有價值。借助Flex Logix革命性的互連技術和設計方法,我們可以在不到一年的時間內經濟性地在任何鑄造工藝節點上使用它。

責任編輯:tzh

-

FPGA

+關注

關注

1660文章

22423瀏覽量

636656 -

芯片

+關注

關注

463文章

54031瀏覽量

466432 -

asic

+關注

關注

34文章

1274瀏覽量

124661 -

晶體管

+關注

關注

78文章

10396瀏覽量

147874

發布評論請先 登錄

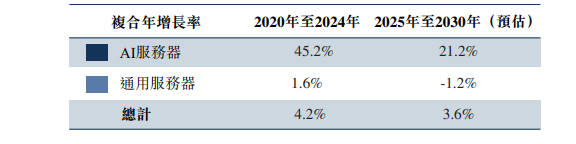

從內存接口到PCIe/CXL、以太網及光互連,高速互連芯片市場分析

TE推出的AMPMODU互連系統有何特點?赫聯電子怎么樣?

沒有專利的opencv-python 版本

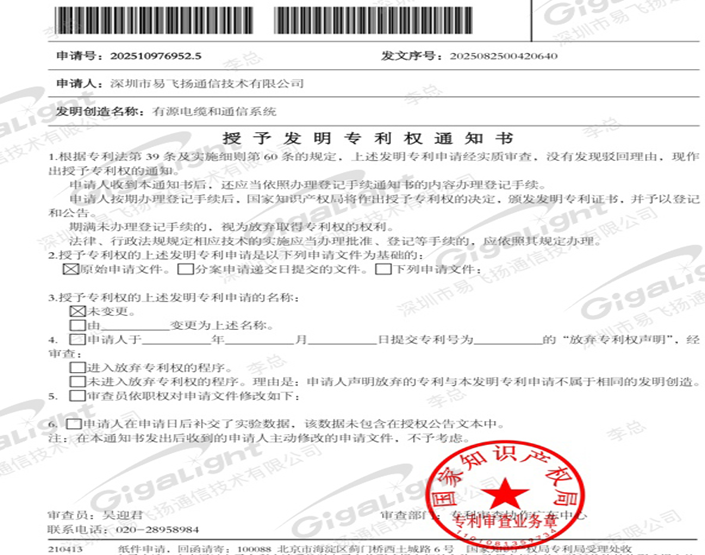

易飛揚獲得一項有源電纜系統的關鍵發明專利

TE推出AMPMODU互連系統具有哪些產品特性?-赫聯電子

無刷雙饋電機專利技術發展

開源FPGA硬件,核心開發者招募中......

輪邊驅動電機專利技術發展

擁抱開源!一起來做FPGA開發板啦!

XSR芯片間互連技術的定義和優勢

TE的高速可插拔I O互連產品有什么用?-赫聯電子

互連層RC延遲的降低方法

半導體芯片中的互連層次

我們如何使用專利互連來設計eFPGA?

我們如何使用專利互連來設計eFPGA?

評論