PCBA 的包工包料加工中阻焊膜是一種很重要的涂覆材料,可以在 PCBA 的焊接過程和焊接之后為 PCBA 板提供介質和機械屏蔽,并且防止焊料在這個位置進行沉積。一般在電子加工廠的加工中常用的焊膜有兩種材料,液態和干膜。

在 PCBA 加工和 SMT 貼片加工中阻焊油墨都是非常重要的,它的主要作用是保護電路板,防止導體沾錫、防止因受潮等原因引起的短路、防止在加工中因為不合格的接觸方式引起的斷路等,并且是保證 PCBA 板能在惡劣環境中正常使用的原因之一。下面簡單介紹 PCBA 包工包料加工中的阻焊膜設計不良有哪些:

1、焊盤與通孔連線。貼裝焊盤連接導通孔之間的導線原則上均應做阻焊。

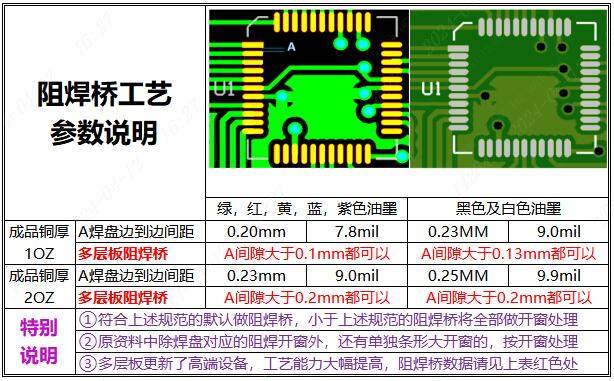

2、焊盤與焊盤之間的阻焊設計,阻焊圖形規格應符合具體元器件焊端分布情形設計:焊盤與焊盤之間如用開窗式阻焊導致焊接時焊盤之間短路,焊盤與焊盤之間設計成引腳獨立阻焊方式,焊接時焊盤之間不會短路。

3、元器件阻焊圖形尺寸不當,過大的阻焊圖形設計,相互會“遮蔽”而導致無阻焊,使元器件間距過小。

4、元器件下有過孔未做阻焊膜,元器件下沒有阻焊的過孔,過波峰焊后過孔上的焊料可能會影響 IC 焊接的可靠性,也可能會造成元器件短路等缺陷。

審核編輯 黃昊宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

PCBA

+關注

關注

25文章

1924瀏覽量

56821

發布評論請先 登錄

相關推薦

熱點推薦

PCB阻焊覆蓋的唯一依據:Gerber文件

?

如果您理解了上述邏輯,其實解決方案就非常簡單清晰了。避免“阻焊做錯”的麻煩,核心是讓“Gerber文件”與“設計需求”完全一致,具體可按以下步驟操作:

1、設計階段明確需求:

明確過孔用途——普通

發表于 01-23 13:58

在并聯使用MOS存在一些問題,要怎樣做才能避免這些問題?

在并聯使用MOS存在一些問題,那我們要怎樣做才能避免這些問題?

首先,器件的一致性一定要好。

在功率MOSFET多管并聯時,器件內部參數的微小差異就會引起并聯各支路電流的不平衡而導致單管過流損壞。

其次是功率。如果功率高于25%

發表于 12-10 08:19

線路板阻焊工藝對PCB的可靠性有何影響?

特性。高頻電路中,阻焊層厚度偏差10μm可導致50Ω傳輸線阻抗波動±3Ω,反射損耗差異達5dB?。激光開窗工藝能將尺寸偏差控制在0.05mm以內,提升10Gbps信號眼圖張開度40%?。 絕緣防護? 阻

什么是SMD&NSMD,怎么區分呢?

被阻焊膜覆蓋,僅有一面參與焊接。而相同焊盤尺寸的情況下,因NSMD銅箔的四周也參與焊接,相當于有三面都參與焊接, 焊接面積要大于SMD ,因

發表于 07-20 15:42

PCB設計中過孔為什么要錯開焊盤位置?

在PCB設計中,過孔(Via)錯開焊盤位置(即避免過孔直接放置在焊盤上)是出于電氣性能、工藝可靠性及信號完整性的綜合考量,具體原因如下: 1. 防止焊料流失,確保焊接質量 焊盤作用 :

如何避免體積表面電阻率測試儀中的“假高阻”現象?

。北京冠測精電儀器設備有限公司深耕材料檢測儀器研發多年,結合豐富的實踐經驗,為您剖析 “假高阻” 現象成因,并提供有效避免策略。? 一、“假高阻” 現象的主要成因? (一)測試環境因素? 濕度干擾 :環境濕度偏高時,

PCB阻焊橋脫落與LDI工藝

本文對貼片廠貼回來的電路板出現芯片引腳間的連錫問題、PCB板(電路板)的阻焊橋脫落有一定意義,特別是做電子產品的工程師強烈建議閱讀、而對于個人DIY的電子玩家也可以了解這些概念。 ? 1. 阻

連接器焊接后引腳虛焊要怎么處理?

焊接是連接電子元器件與PCB(印刷電路板)的關鍵步驟,焊接過程中可能會出現虛焊問題,即焊點未能形成良好的電氣和機械連接。虛焊會導致電路接觸不良、信號傳輸不穩定,甚至設備無法正常工作。本期蓬生電子唐工將帶大家探討連接器焊接后引腳虛焊

Allegro Skill封裝原點-優化焊盤

在PCB設計中,部分文件可能因從Altium Designer或PADS軟件轉換而來,導致兼容性問題。這些問題通常表現為貼片焊盤會自動增加Thermal Pad、Anti Pad以及焊盤缺失阻

用引線連接外部電壓控制LTC6563的adj0、adj1引腳并切換跨阻阻值時,如何避免跨阻放大電路受到空間電磁波干擾?

三條線即為通過穿心電容控制跨阻的三條導線。

但有一個顯而易見的問題:如果我之后將LTC6563的四個通道的選擇引腳、以及0MUX、power mode引腳全部接到外部,由控制板控制,難道這些控制引線每

發表于 03-24 07:50

使用阻焊膜時,要避免“這些“

使用阻焊膜時,要避免“這些“

評論