自動目標識別(ATR)算法通常包括自動地對目標進行檢測、跟蹤、識別和選擇攻擊點等算法。戰場環境的復雜性和目標類型的不斷增長使ATR算法的運算量越來越大,因此ATR算法對微處理器的處理能力提出了更高的要求。由于通用數字信號處理芯片能夠通過編程實現各種復雜的運算,處理精度高,具有較大的靈活性,而且尺寸小、功耗低、速度快,所以一般選擇DSP芯片作為微處理器來實現ATR算法的工程化和實用化。

為了保證在DSP處理器上實時地實現ATR算法,用算法并行化技術。算法并行化處理的三要素是:①并行體系結構;②并行軟件系統;③并行算法。并行體系結構是算法并行化的硬件基礎,并行算法都是針對特定的并行體系結構開發的并行程序。根據DSP處理器的數目,ATR算法的并行實現可以分為處理器間并行和處理器內并行。處理器間并行是指多個DSP處理器以某種方式連接起來的多處理器并行系統,ATR算法在多個處理器上并行招待。

根據處理器使用存儲器的情況,多處理器并行系統又可分為共享存儲器多處理器并行系統和分布式多處理器并行系統。處理器內并行是指在單個DSP處理器內通過多個功能單元的指令級并行(ILP)來實現ATR算法的并行化。本文分別對在共享存儲器多處理器并行系統、分布式多處理器并行系統和指令級并行DSP處理器上并行實現ATR算法進行了探討。

1 在共享存儲器多處理并行系統上實現ATR算法

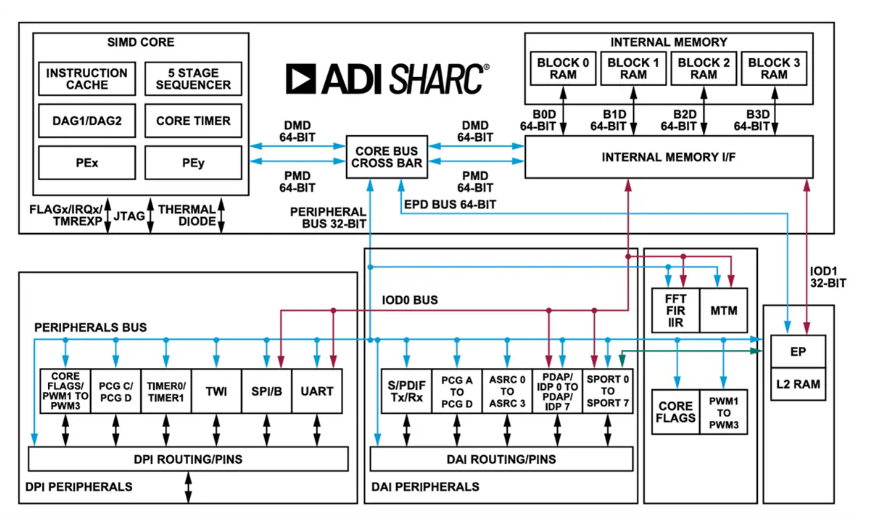

在共享存儲器多處理器并行系統中,各個處理器通過共享總線對所有的存儲器進行操作,實現各個處理器之間的數據通信。而在任一時刻,只允許一個處理器對共享總線進行操作。所以處理器對存儲器進行讀/寫操作時就必須先獲得對共享總線的控制權,這通過總線仲裁電路實現。然而,由于所有的處理器只能通過一條共享總線對存儲器進行訪問,這在處理器數目比較多或者處理器之間頻繁交換數據的情況下容易引起總線沖突和等待而降低整個并行系統的運行速度。共享存儲器多處理器并行系統的優點是結構簡單,當處理器的數目較少時,可以達到較高的加速比。 ADSP2106x處理器支持最為常用的共享存儲器多處理器并行系統,組成多處理器系統的每一片ADSP2106x的片內存儲器統一編址,任一ADSP2106x可以訪問其它任何一片ADSP2106x的片內存儲器。由于片內SRAM為雙口存儲器,因而這種訪問并不中斷被訪問處理器的正常工作。每個處理器片內SRAM既是該處理器的局部存儲器,又是共享存儲器的部分。在不增加輔助電容的情況下,通過外部總線接口直接相連的處理器數量最多為6個。由于每個處理器的工作程序放在其片內的雙口SRAM中,因此各個處理器可以實現并行處理,這是ADSP2106x的存儲器結構所決定的。 ATR算法在共享存儲器多處理器并行系統中實現時,在編寫并行算法程序方面應當重點考慮的問題包括: (1)均衡地把任務分配給各個處理器 ATR算法在共享存儲器多處理器并行系統中實現任務級并行,因此必須把ATR算法劃分為計算量均衡的多個任務,把各個任務分配給多個處理器,才能發揮多處理器并行系統的最大并行效率。 (2)盡量減少多處理器之間數據通信 由于多處理器只能通過一條共享總線對存儲器進行訪問,這在多處理器之間頻繁交換數據的情況下容易引起總線競爭而降低整個并行系統的運行速度。 (3)利用單個處理器的并行編程特性 充分應用單個處理器的并行編程特性,有利于縮短各個處理器上任務的運行時間。例如,ADSP2106x的32位浮點運算單元包含一個乘法器、一個加法器和移位邏輯電路,它們并行工作;比特倒轉尋址在傅立葉變換運算時非常有用;循環尋址在作卷積、數字濾波運算時經常用到等。

2 在分布式多處理器并行系統上實現ATR算法

在分布式多處理器并行系統中,多處理器有各自獨立的存儲器,多個處理器通過通信口相連構成分布式多處理器并行系統。分布式多處理器并行系統的加速比和處理器的數目呈線性關系,所以只要增加處理器的數目,分布式多處理器并行系統的處理能力就能夠成比例地增加。分布式多處理器比較適合于構成大規模并行系統。

目前,計算量過大仍然是制約許多有效的ATR算法實時實現的個主要因素。ATR算法在分布式多處理器并行系統上實時實現是一個很有潛力的研究領域,特別在地基和天基雷達信號處理系統中有廣闊的應用前景。分布式多處理器并行系統的連接方式有線形、樹形、星形、網孔和超立方體結構等。樹形和星形網絡的優點是網絡管理容易、數據通信進尋徑簡單;缺點是樹形網絡的根節點處理器和星形網絡的中央節點處理器的輸入/輸出吞吐量大,易造成通信瓶頸。所以樹形和星形網絡不適合ATR算法各個任務數據通信量較大的應用場合。

在分布式多處理器并行系統中并行實現ATR算法目前還處于研究的初始階段,在編寫并行算法程序應當重點考慮兩個方面: (1)各處理器任務的均衡分配 在分布式多處理器并行系統中處理器的數目通常較多,只有合理地對眾多的處理器均衡地分配任務,才能最大地發揮并行系統的總體性能,提高并行系統的加速比。 (2)處理器節點間的高效通信 在分布式多處理器并行系統中數據通信都是點對點通信。即兩個相鄰的處理器之間通過通信口通信。因此需要合理安排各個處理器節點在網絡結構中的位置,盡可能地縮短處理器節點間的通信路徑長度,從而實現處理器節點間的高效數據通信。

3 在指令級并行DSP處理器上實現ATR算法

在單片DSP處理器內通過多個功能單元的指令級并行(ILP)實現ATR算法的并行化處理,目前適合ATR算法實時處理的指令級并行芯片是TI公司的TMS320C6x系列DSP。TMS320C6x系列DSP處理器是第一個使用超長指令字(VLIW)體系結構的數字信號處理芯片。下面以TMS320C62x定點系列DSP為例說明指令級并行的原理和ATR并行算法軟件開發方法。內核中的8個功能單元可以完全并行運行,功能單元執行邏輯、位移、乘法、加法和數據尋址等操作。內核采用VLIW體系結構,單指令字長32位,取指令、指令分配和指令譯碼單元每周期可以從程序存儲器傳遞8條指令到功能單元。這8條指令組成一個指令包,總字長為256位。芯片內部設置了專門的指令分配模塊,可以將每個256位的指令分配到8個功能單元中,并由8個功能單元并行運行。TMS320C62x芯片的最高時鐘頻率可以達到200MHz。當8個功能單元同時運行時,該芯片的處理能力高達1600MIPS。

審核編輯 黃昊宇

-

處理器

+關注

關注

68文章

20255瀏覽量

252306 -

dsp

+關注

關注

561文章

8244瀏覽量

366655 -

atr

+關注

關注

0文章

2瀏覽量

1390

發布評論請先 登錄

SMJ320C80數字信號處理器:架構、特性與應用全解析

HXS320F280049C數字信號處理器(DSP)芯片

Ceva在恩智浦的軟件定義車輛處理器上實現 實時人工智能加速

利用Verdi調試協處理器的實現步驟

MD5信息摘要算法實現二(基于蜂鳥E203協處理器)

Camellia算法的實現(基于開源蜂鳥E203協處理器)

Camellia算法的實現二(基于開源蜂鳥E203協處理器)

AES加解密算法邏輯實現及其在蜂鳥E203SoC上的應用介紹

基于E203 RISC-V的音頻信號處理系統 -協處理器的乘累加過程

Analog Devices Inc. ADSP1802 SHARC?處理器數據手冊

HXS320F28027數字信號處理器(32位RISC-V DSP)

ADAU1463/ADAU1467 具有擴展內部存儲器和 I/O功能的Sigma DSP數字音頻處理器技術手冊

ADSP1802 SHARC處理器技術手冊

異形拼接處理器支持哪些顯示技術?

異形拼接處理器可以實現的效果

DSP處理器上并行實現ATR算法

DSP處理器上并行實現ATR算法

評論