典型的時序模型由發(fā)起寄存器、組合邏輯和捕獲寄存器3部分組成,如圖1所示形成了三條時鐘路徑:原時鐘路徑(Source Clock path)、數(shù)據(jù)時鐘路徑(Data path)、目的時鐘路徑(Destination Clock path)。

1、建立時間(setup)和保持時間(hold)

如圖1所示,時鐘上升邊沿(Capture Edge 、Next Launch Edge)會將數(shù)據(jù)保存下來,但是必須要滿足一定的條件:

A,建立時間Tsu:在時鐘有效沿之前,數(shù)據(jù)必須保持穩(wěn)定的最小時間;

B,保持時間Th:在時鐘有效沿之后,數(shù)據(jù)必須保持穩(wěn)定的最小時間;

這就相當(dāng)于一個窗口時間,在有效邊沿的窗口時間內(nèi),數(shù)據(jù)必須保持穩(wěn)定;這里的時鐘信號時序和數(shù)據(jù)信號時序,都是寄存器實際感受到的時序。

2、發(fā)起沿和捕獲沿

如圖1所示,發(fā)起沿和捕獲沿通常相差一個時鐘周期同時捕獲沿也是下一個發(fā)起沿。

發(fā)起沿(LaunchEdge):數(shù)據(jù)被launch的時鐘邊沿;也就是說,每一個啟動沿,一般都會產(chǎn)生一個新的數(shù)據(jù)!

捕獲沿(CaptureEdge):數(shù)據(jù)被latch的時鐘邊沿;也就是說,每一個鎖存沿,都會有一個新的數(shù)據(jù)被保存!

3、時序模型2

如圖2所示:

Clk--時鐘源

Rega--發(fā)起寄存器

Regb--捕獲寄存器

Tclka--原時鐘延時

Tclkb--目的時鐘延時

Tco--發(fā)起沿有效到數(shù)據(jù)出現(xiàn)在發(fā)起寄存器Q端口所需時間

Tdata--數(shù)據(jù)延時(組合邏輯和走線延時)

Tsu--捕獲寄存器建立時間

Th--捕獲寄存器保持時間

4、數(shù)據(jù)到達時間(Data Arrival Time)

數(shù)據(jù)到達時間(Data Arrival Time)=Launch Edge +Tclka+Tco+Tdata

已發(fā)起沿為時間參考點,LaunchEdge 通常為0。

5、數(shù)據(jù)建立需求時間(setup)

數(shù)據(jù)建立需求時間(DataRequired Time(setup)) = Tclkb-Tsu-Clock Uncertainty

表明數(shù)據(jù)必須提前Tsu穩(wěn)定存在于捕獲寄存器的輸入端口。

6、數(shù)據(jù)保持需求時間(hold)

數(shù)據(jù)保持需求時間(DataRequired Time(hold))=Tclkb +Th-Clock Uncertainty

表明數(shù)據(jù)必須在時鐘捕獲沿(regb/clk)之后穩(wěn)定存在一段時間Th。

7、建立時間裕量(Setup Slack)

建立時間裕量(SetupSlack)= Data Required Time(setup)-Data Arrival Time(setup)

如果SetupSlack為正,則說明數(shù)據(jù)在規(guī)定的時間內(nèi)達到了目標(biāo)。反之,則認為數(shù)據(jù)并沒有在規(guī)定的時間達到目標(biāo),此時REG2鎖存的數(shù)據(jù)很有可能存在亞穩(wěn)態(tài)。

8、保持時間裕量(Hold Slack)

保持時間裕量(holdSlack)=DataRequired Time(hold)-Data Arrival Time(hold)

如果為正,則認為數(shù)據(jù)在被鎖存的時候有足夠多的穩(wěn)定時間,是有效的。反之則認為數(shù)據(jù)有誤或者數(shù)據(jù)可能存在亞穩(wěn)態(tài)。

編輯:hfy

-

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

130012 -

數(shù)據(jù)信號

+關(guān)注

關(guān)注

0文章

61瀏覽量

12297 -

Vivado

+關(guān)注

關(guān)注

19文章

857瀏覽量

71136

發(fā)布評論請先 登錄

Vivado時序約束中invert參數(shù)的作用和應(yīng)用場景

RGB時序燈條的工作原理講解

輸入引腳時鐘約束_Xilinx FPGA編程技巧-常用時序約束詳解

eVTOL動力系統(tǒng)的多元化技術(shù)路徑分析:純電、燃油與增程式的性能邊界、適用場景與綜合成本模型構(gòu)建

數(shù)字IC/FPGA設(shè)計中的時序優(yōu)化方法

vivado時序分析相關(guān)經(jīng)驗

移植E203到Genesys2開發(fā)板時遇到時序問題的常見原因

E203內(nèi)核移植到FPGA開發(fā)板時出現(xiàn)時序違例的解決方式

時序約束問題的解決辦法

E203分享之DDR擴展方案實施流程(下)

京東:調(diào)用用戶行為API分析購買路徑,優(yōu)化頁面跳轉(zhuǎn)邏輯

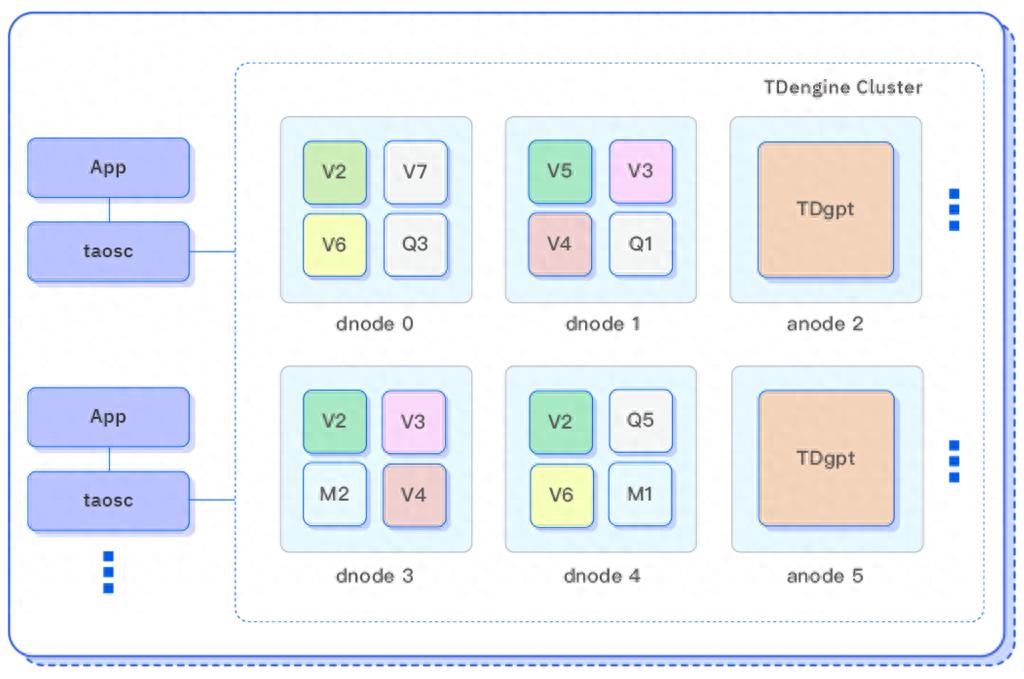

TDengine 發(fā)布時序數(shù)據(jù)分析 AI 智能體 TDgpt,核心代碼開源

一文詳解Vivado時序約束

【vivado學(xué)習(xí)】典型時序模型的三條時鐘路徑分析

【vivado學(xué)習(xí)】典型時序模型的三條時鐘路徑分析

評論