賽靈思致力于為所有開發人員開啟一種新的設計體驗!

Vitis統一軟件平臺可以在包括FPGA、SoC和Versal ACAP在內的異構Xilinx平臺上開發嵌入式軟件和加速應用程序。它為加速邊緣計算、云計算和混合計算應用程序提供了統一的編程模型。

利用與高級框架的集成,使用加速庫用C、C++或Python開發,或使用基于RTL- accelerators &低級別運行時APIs進行更細粒度的實現控制。總之,可以選擇您需要的多種抽象級別。

圍繞賽靈思自適應計算挑戰賽我們已經推出了一系列Vitis深入教程,不僅面向參賽用戶,更適合廣大開發者細致學習。該教程重點介紹了在所有Xilinx平臺上部署加速應用程序的設計方法和編程模型,并不斷更新。

本次視頻,由Xilinx技術專家原鋼為大家帶來一個非常棒的全系統RTL內核集成教程,展示了如何將自由運行的RTL內核、Vitis庫和基于hls的數據遷移器組合在一起。

本教程演示如何使用Vitis core開發工具包將RTL內核編程到FPGA中,并使用公共開發流程構建硬件仿真。

Adaptive Computing Challenge 2020

賽靈思近期推出專屬挑戰賽技術論壇,在開發與啟動競賽的開發階段,討論與Xilinx產品和解決方案相關的技術問題。

https://forums.xilinx.com/t5/Adaptive-Computing-Challenge/bd-p/ACC_2020

其他技術支持 可訪問:

Vitis Forum -

https://forums.xilinx.com/t5/Vitis-Acceleration-SDAccel-SDSoC/bd-p/tools_v

Vitis AI Forum -

https://forums.xilinx.com/t5/AI-and-Vitis-AI/bd-p/AI

Alveo Forum -

https://forums.xilinx.com/t5/Alveo-Accelerator-Cards/bd-p/alveo

HLS Forum -

https://forums.xilinx.com/t5/High-Level-Synthesis-HLS/bd-p/hls

有關挑戰賽的問題都可在私信Xilinx技術社區或者郵件至contest2020@xilinx.com

原文標題:滴!Vitis RTL內核集成教程更新

文章出處:【微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

-

嵌入式

+關注

關注

5198文章

20449瀏覽量

334012 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133427 -

編程

+關注

關注

90文章

3716瀏覽量

97185

原文標題:滴!Vitis RTL內核集成教程更新

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

阿里狗16.6,層疊表能打開,但是打開后內容縮在一起,調整間距之后,關閉在打開還是縮在一起,怎么處理呢

XINGLIGHT成興光 2026光耦產品手冊

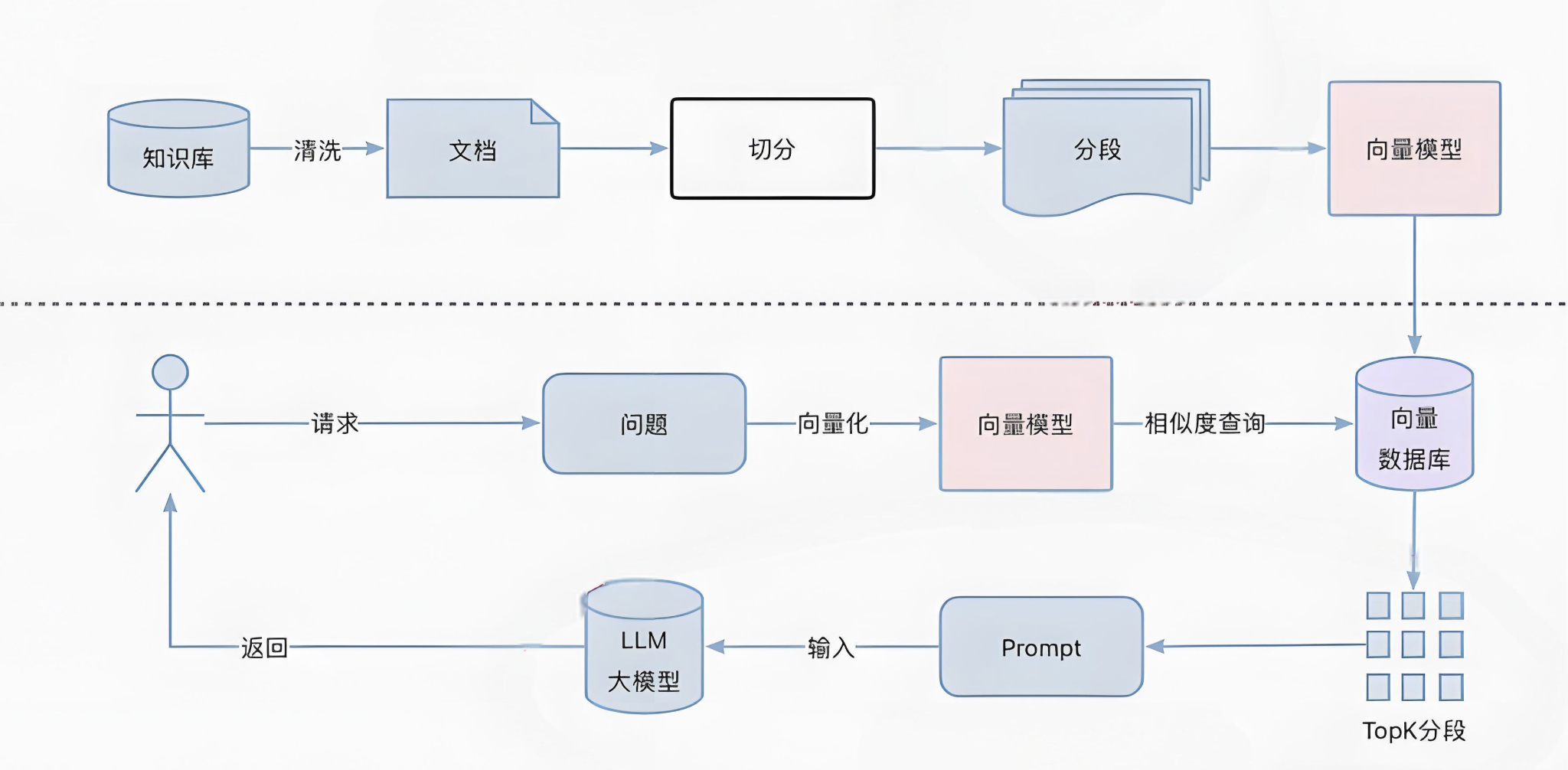

RAG實踐:一文掌握大模型RAG過程

無法將Jlink調試器與CYBT263065EVAL COOLDIM_PRG_BOARD連接在一起怎么解決?

如何在Unified IDE中創建視覺庫HLS組件

使用AMD Vitis Unified IDE創建HLS組件

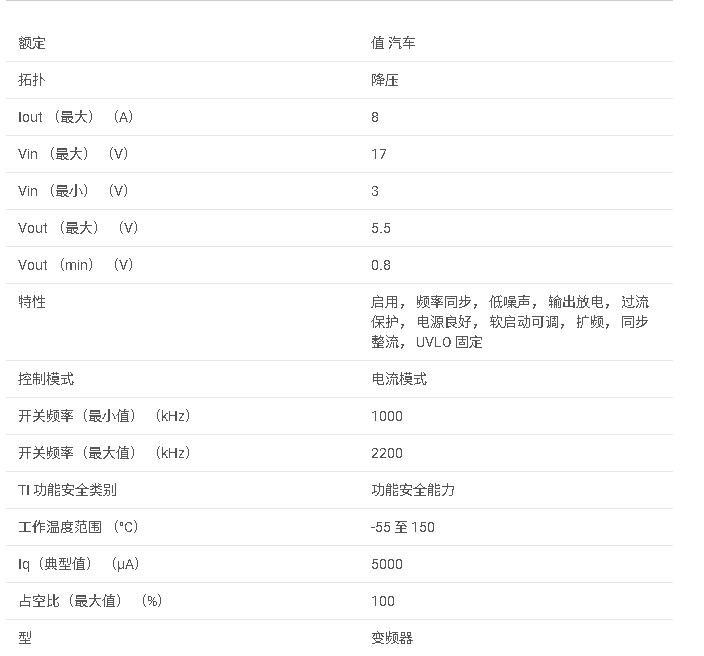

TPS62918-Q1 汽車級、3V 至 17V 輸入、8A 低噪聲降壓轉換器,集成鐵氧體磁珠濾波器數據手冊

fx3 uvc uart組合代碼在usb 2.0中不起作用怎么解決?

如何將FX3與WSL(Linux 的 Windows 子系統)一起使用?

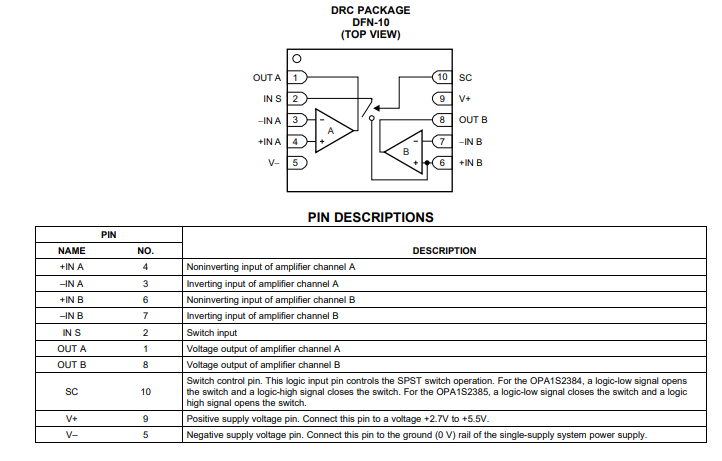

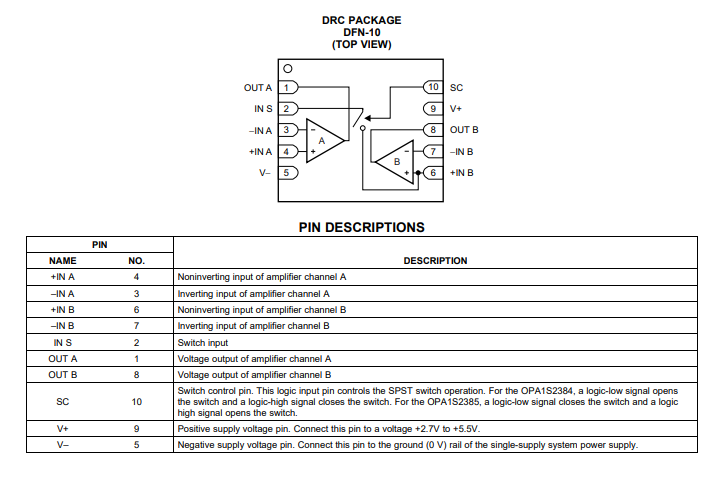

OPA1S2385 具有集成低電平有效開關和緩沖器的、250MHz、CMOS跨阻放大器技術手冊

OPA1S2384 具有集成開關和緩沖器的 250MHz、CMOS跨阻放大器 (TIA)技術手冊

如何將自由運行的RTL內核、Vitis庫和基于hls的數據遷移器組合在一起

如何將自由運行的RTL內核、Vitis庫和基于hls的數據遷移器組合在一起

評論