在本文中,我們將講解如何在 Vivado Design Suite 中完成平臺準備工作,以便將其用作為 Vitis 中的加速平臺。 您既可以采用已確認的成熟設計作為平臺,這樣只需稍作增強便可靈活運用于加速軟件功能,或者也可以采用僅含加速所需拓撲結構的簡單基礎平臺。重點在于,此平臺并沒有必要采用一次性設計,而應采用可有機變化的設計,這樣即可隨您的設計需求而變。

01 引言

加速軟件組件就意味著將其從 CPU 卸載至可編程邏輯中的加速 IP。Vitis 工具將負責處理在加速 IP 與 CPU 之間添加數據移動程序的操作。 但它確實需要用戶提供輸入信息。它需要了解從 SoC 和加速 IP 連接到哪個接口。它還需要了解有哪些時鐘/復位可供使用。

并且由于我們在 CPU 與加速 IP 之間發送數據塊,因此需要中斷信號。基本上就這些……好吧,其實還要向 Vitis 工具提供一些其它信息,這個我們稍后再聊。

先繼續往下看。啟動 Vivado 并創建工程。我使用的是 ZCU104 評估板。但以下步驟對于所有 Zynq UltraScale 開發板都是通用的,無論是開發板還是定制板都一樣。

02 創建硬件設計

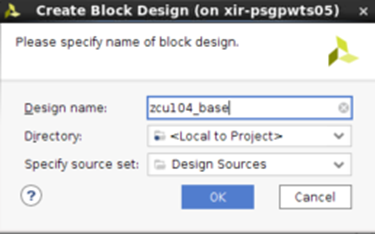

創建塊設計 (BD)。此處名稱與用于命名平臺的名稱相同。

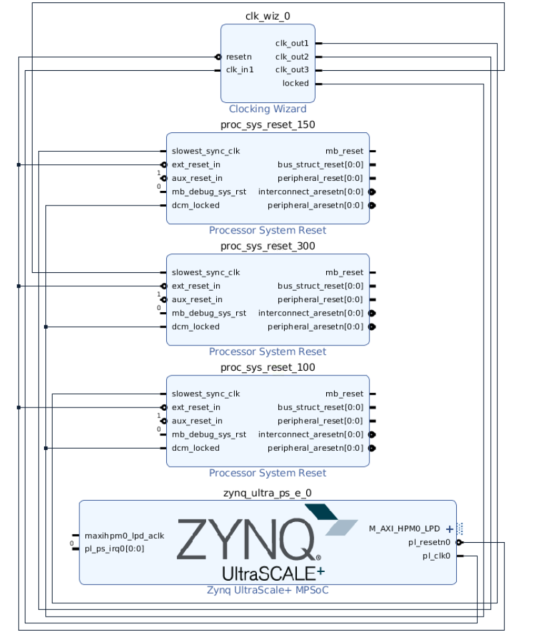

從 IP 目錄添加 Zynq UltraScale 處理器子系統 IP 塊。如果使用的是開發板,那么應啟用“塊自動化設置 (Block Automation)”功能。

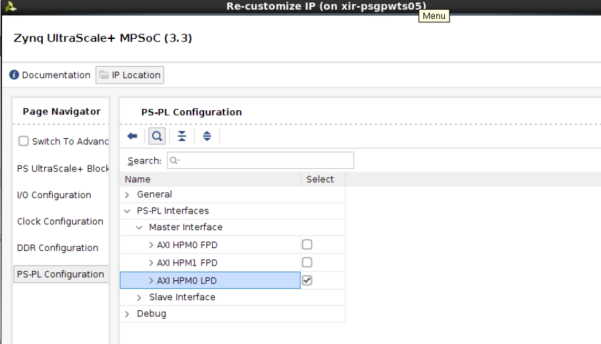

我把默認接口更改為僅包含 LPD:

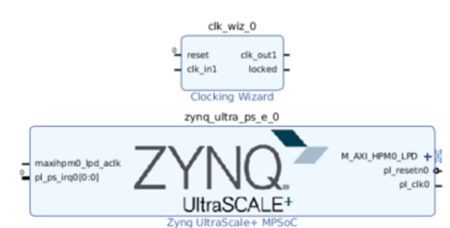

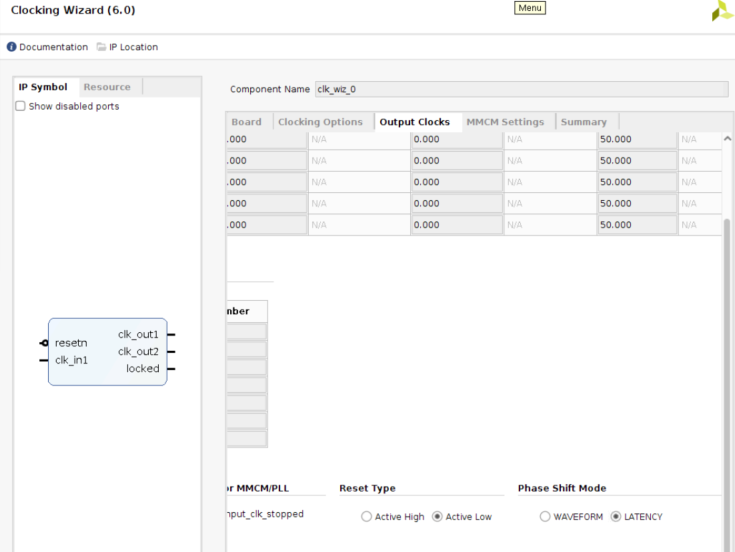

在我們的簡單平臺中,可以只創建 2 個時鐘。這些時鐘將在 Vitis 中使用。 我們可從 IP 目錄添加 Clocking Wizard:

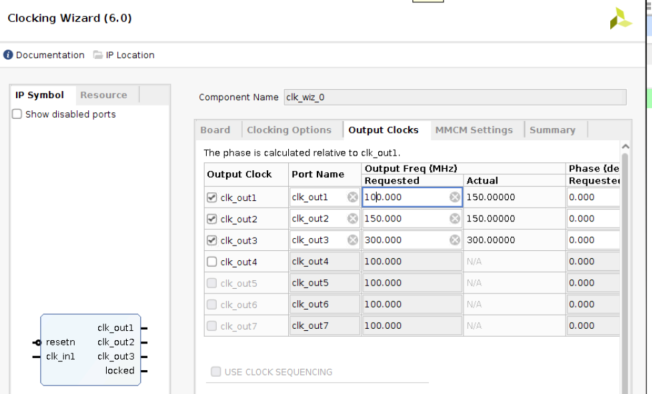

默認情況下,復位處于高電平有效狀態,而復位源(位于 Zynq UltraScale 器件上)則處于低電平有效狀態。因此,在進行時鐘設置配置時需牢記此信息。 我添加了 3 個輸出時鐘:100Mhz、150Mhz 和 300Mhz:

并將復位極性設置為低電平有效(Active Low):

針對每個時鐘都需要提供同步復位。我們有 3 個時鐘,因此需要從 IP 目錄添加 3 個 Processor System Reset IP 核:

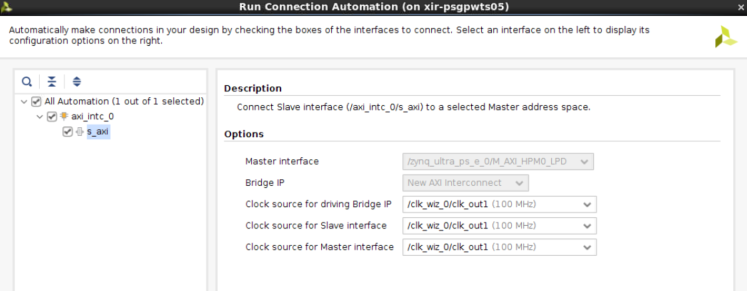

下一步,需要添加中斷信號。這里我們從 IP 目錄添加 AXI Interrupt Controller。用戶可以使用 IP integrator 中的“運行自動連接(Run Connection Automation)”功能來處理 AXI 連接。

使用 100Mhz 時鐘

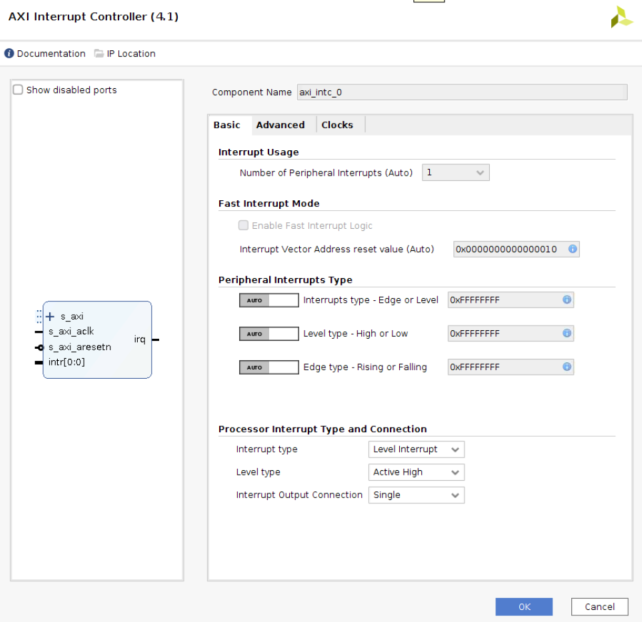

在 AXI Interrupt Controller 中,將“中斷輸出連接(Interrupt Output Connection)”設置為“單連接 (Single)”,并將其連接到 Zynq UltraScale IP 上的 pl_ps_irq:

對于基本硬件平臺,這樣設置就可以了。 現在,我們只需設置元數據,以便通過 Platform (PFM) 屬性將硬件信息告知 Vitis 即可。

03 添加 PFM 屬性

PFM 屬性是將元數據傳遞給 Vitis 所必需的。 Vitis 會提取這些數據以判定哪些接口、時鐘和中斷信號可用于在現有平臺中添加加速部分。

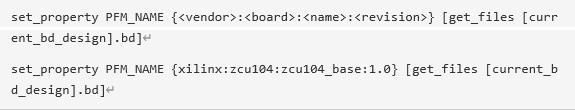

平臺名稱

首先,對平臺命名:

完成命名后,您將看到一個新的“平臺 (Platform)”選項卡。其中將顯示整個設計中的所有時鐘、接口和中斷信號。 我們需要篩選可用于 Vitis 的資源。

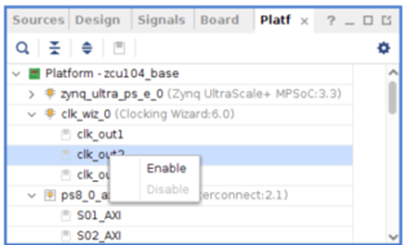

啟用時鐘

右鍵單擊時鐘,然后單擊“啟用 (Enable)”:

針對 clk_out3 重復此操作。

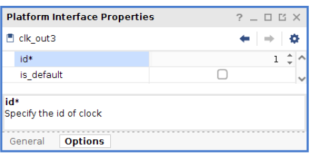

時鐘屬性

選中“選項 (Options)”選項卡:

注:時鐘 ID 必須以 0 開頭并遞增,因此,請更改此處設置。我們還必須指定默認值。 此處默認值即 Vitis 中使用的默認時鐘:

設置 clk_out3 的索引:

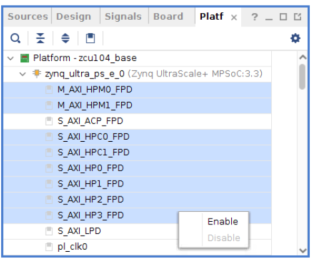

啟用接口

可采用塊設計中可用的任意接口,例如,Zynq UltraScale 器件上的接口或 AXI Interconnect 上的接口。 在此例中,我只添加 Zynq UltraScale 器件上的接口。

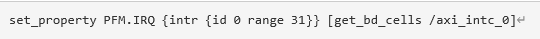

啟用中斷

04 工程屬性

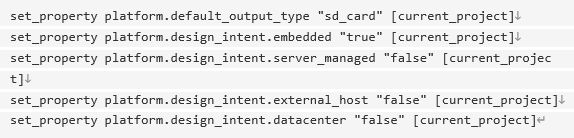

Vitis IDE 是支持眾多不同流程(例如,數據中心、加速或嵌入式流程等)的統一工具。我們需要將此用途傳遞給 Vitis 工具。 如果要創建嵌入式設計,就需要指定該用途。在此示例中,我們將把 Vitis 用于加速。此用途必須明確指定,因為 Vitis 需要告知下游工具如何處理該平臺。 此處可看到下列屬性:

05 創建 XSA

完成以下任務以創建 XSA

?生成塊設計 ?創建 HDL 封裝 ?生成比特流 ?依次單擊“File -> Export -> Export Hardware” o 依次單擊“Expandable -> Pre Synthesis”,然后選中“Bitstream”

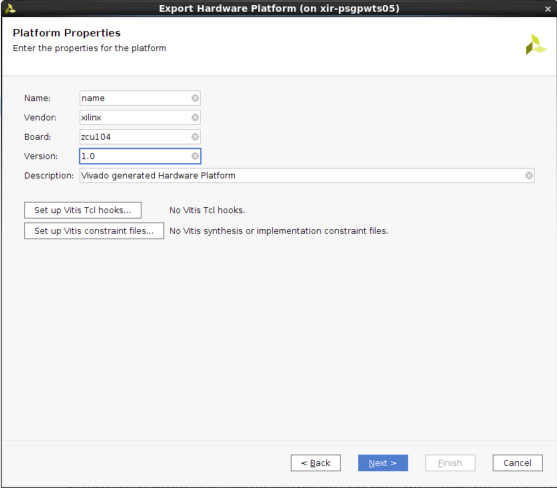

用戶可在此處輸入詳細信息:

至此大功告成。

-

cpu

+關注

關注

68文章

11279瀏覽量

224987 -

可編程邏輯

+關注

關注

7文章

526瀏覽量

45402 -

Vivado

+關注

關注

19文章

857瀏覽量

71112

原文標題:如何在 Vivado 中為加速平臺創建硬件工程

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

獲取Ozon商品詳情數據的API接口技術指南

調用樂天平臺API獲取商品詳情數據

應用開發準備工作

AMD Vivado Design Suite 2025.2版本現已發布

Windows系統下用vivado將電路燒寫到MCU200T板載FLASH的方法

如何在Vivado上仿真蜂鳥SOC,仿真NucleiStudio編譯好的程序

元服務發布準備工作

亞馬遜云科技推出Amazon Quick Suite,引領Agentic AI驅動的工作新范式

土壓力計在使用前需要進行哪些準備工作?

Vivado無法選中開發板的常見原因及解決方法

想做好PCBA貼片加工?這些前期準備工作要做好!

AMD Vivado Design Suite 2025.1現已推出

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

Vivado 2018.3軟件的使用教程

如何在Vivado Design Suite中完成平臺準備工作

如何在Vivado Design Suite中完成平臺準備工作

評論