概述

Zynq UltraScale+ MPSoC 系列基于 Xilinx UltraScale MPSoC 架構,在單個器件中集成了功能豐富的、基于 ARM 的 64 位四核或雙核處理系統 (PS) 和 Xilinx 可編程邏輯 (PL) UltraScale 架構。此外,還包括片上存儲器、多端口外部存儲器接口以及豐富的外設接口,尤其是 16.3 Gbps GTH 收發器,該收發器支持與像 NVMe SSD 驅動器這樣的 PCI Express Gen3 存儲設備接口。本文展示了通過使用 Design Gateway 的 NVMeG3-IP 內核在 Xilinx 的 ZCU102 評估套件上實現 NVMe 固態硬盤 (SSD) 接口的解決方案,該方案可實現驚人的快速性能:寫入速度達 2,319 MB/s,讀取速度達 3,347 MB/s。

Zynq UltraScale+ MPSoC ZCU102 評估套件簡介

ZCU102 是用于快速原型開發的通用評估板,基于 XCZU9EG-2FFVB1156E MPSoC 器件。該評估板包含高速 DDR4 SODIMM 和組件內存接口、FMC 擴展端口、每秒數千兆位的串行收發器、各種外設接口以及用于用戶定制設計的 FPGA 邏輯器件,藉此提供一個靈活的原型開發平臺。

圖 1:ZCU102 評估套件。(圖片來源:Xilinx Inc.)

ZCU102 提供可編程邏輯功能,可用于 5G 無線網絡、下一代高級駕駛輔助系統 (ADAS) 和工業物聯網 (IIoT) 解決方案等最先進的應用。

總之,對于需要像 NVMe SSD 驅動器這樣的高性能、高可靠性外部數據存儲的應用來說,都有必要采用合適的解決方案,以充分利用支持 PCI Express Gen3 接口的 GTH 收發器。

NVMe SSD 存儲簡介

NVM Express (NVMe) 定義了主機控制器通過 PCI Express 訪問 SSD 的接口。NVM Express 僅使用兩個寄存器(命令發出和命令完成),從而優化了命令發出和完成過程。除此以外,NVMe 支持并行操作,在單個隊列中支持多達 64K 的命令。64K 命令條目提高了順序訪問和隨機訪問兩方面的傳輸性能。

NVMe 驅動器為高速數據存儲和計算鋪平了道路。借助 PCIe Express Gen3 技術,新型 NVMe SSD 驅動器即可實現高達 40 Gbps 的峰值性能。

此處展示了 NVMe 存儲設備示例。

在 ZCU102 上 NVMe 主機控制器的實現

圖 2:NVMe 實現。(圖片來源:Design Gateway)

按照慣例,NVMe 主機是通過將主機處理器與 PCIe 控制器配合使用來實現的,從而實現與 NVMe SSD 的數據傳入與傳出。實現 NVMe 協議的目的是,為了與通過較高速總線連接的 PCIe 控制器硬件 CPU 外設進行設備驅動器通信。而數據緩沖和命令隊列都需要外部 DDR 內存,以便在 PCIe 控制器與 SSD 之間傳輸數據。

由于 ZCU102 上的 XCZU9EG-2FFVB1156E FPGA 器件上不含 PCIe Gen3 集成塊,因此無法采用傳統實現方法。

于是,Design Gateway 提出了一種解決方案,即利用 NVMeG3-IP 內核(如圖 2 所示)來實現 Zynq UltraScale+ MPSoC 器件(不含 PCIe 集成塊)的 NVMe SSD 接口。通過 NVMe 接口,ZCU102 即可構建具有較高性能的多通道 RAID 系統,同時最大限度地降低 FPGA 資源消耗。NVMeG3-IP 內核許可中包含參考設計示例,可幫助設計人員縮短開發時間并降低成本。

Design Gateway 的 NVMeG3-IP 概述

在不具備 PCIe 集成塊、CPU 和外部存儲器的情況下,具有 PCIe Gen3 IP 軟核 (NVMeG3-IP) 的 NVMe IP 內核是訪問 NVMe SSD 的理想之選。NVMeG3-IP 包含 PCIe Gen3 IP 軟核和 256 KB 存儲器。如果您的應用需要具有較高速性能的 NVMe SSD 存儲,卻又使用了不包含 PCIe 集成塊的低成本 FPGA,那么建議您使用該解決方案。

圖 3:NVMeG3-IP 框圖。(圖片來源:Design Gateway)

NVMeG3-IP 特性

NVMeG3-IP 具有許多特性,以下列出了其中一部分特性:

1.實現應用層、事務層、數據鏈路層以及物理層的某些部分以訪問 NVMe SSD,而無需占用 CPU

2. 與配置為 4 通道 PCIe Gen3(128 位總線接口)的 Xilinx PCIe PHY IP 配合操作

3. 包含 256 KB 的 RAM 數據緩沖區

4. 經由 dgIF typeS 的簡單用戶接口

5. 支持六個命令,即“識別”、“關閉”、“寫入”、“讀取”、"SMART" 和“刷新”(支持其他命令作為可選項)

6. 支持的 NVMe 器件:

基類代碼:01h(大容量存儲),子類代碼:08h(非易失性),編程接口:02h (NVMHCI)

最小存儲器頁大小 (MPSMIN):0 (4 KB)

最大數據傳輸大小 (MDTS):至少 5 (128 KB) 或 0(無限制)

LBA 單元:512 字節 或 4096 字節

7. 用戶時鐘頻率必須大于或等于 PCIe 時鐘(Gen3 為 250 MHz)

8. 可用參考設計:

帶有 AB17-M2FMC 適配器板的 ZCU102

帶有 AB18-PCIeX16/AB16-PCIeXOVR 適配器板的 KCU105

帶有 AB18-PCIeX16 適配器板的 VCU118

Design Gateway 將 NVMeG3-IP 開發成可以作為 NVMe 主機控制器運行,以訪問 NVMe SSD。用戶接口和標準特性旨在實現易用性,無需了解 NVMe 協議的相關知識。NVMeG3-IP 的附加特性是內置的 PCIe IP 軟核,它能通過純邏輯實現 PCIe 協議的數據鏈路層和物理層的某些部分。因此,借助內置的 PCIe IP 軟核和 Xilinx PCIe PHY IP 內核,NVMeG3-IP 即可在不帶 PCIe 集成塊的 FPGA 上運行。Xilinx 的 PCIe PHY IP 是一款可用的免費 IP 內核,包含收發器和邏輯均衡器。

NVMeG3-IP 支持六個 NVMe 命令,即識別、關閉、寫入、讀取、SMART 和刷新。NVMeG3-IP 中集成了 256 KB 的 BlockRAM,可用作數據緩沖區。該系統無需 CPU 和外部存儲器。如需更多詳細信息,請查閱 NVMeG3-IP 規格書,可從我們的網站下載此規格書。

XCZU9EG-2FFVB1156E FPGA 器件的 FPGA 資源使用情況,如下表 1 所示。

表 1:Ultrascale/Ultrascale+ 器件的示例實現統計數據

ZCU102 的實現和性能結果

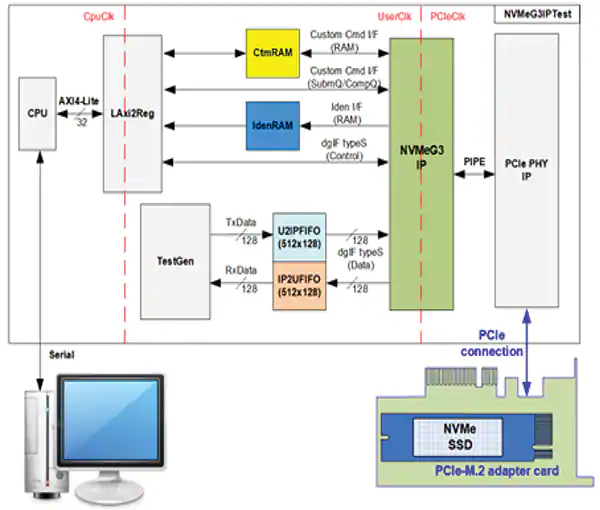

圖 4 展示了基于 ZCU102 的參考設計概覽,以演示 NVMeG3-IP 的操作。該演示系統中的 NVMeG3IPTest 模塊包括以下模塊:TestGen、LAxi2Reg、CtmRAM、IdenRAM 和 FIFO。

有關 NVMeG3-IP 參考設計的更多詳細信息,請參考 Design Gateway 網站上提供的 NVMeG3-IP 參考設計文檔。

圖 4:NVMeG3-IP 參考設計概覽。(圖片來源:Design Gateway)

該演示系統旨在對 ZCU102 上的 NVMe SSD 進行數據寫入/驗證。用戶可通過串行控制臺控制測試操作。要連接 NVMe SSD 與 ZCU102,就需要使用 AB17-M2FMC 適配器板,如圖 5 所示。

圖 5:安裝在 ZCU102 上的 NVMeG3-IP 演示環境。(圖片來源:Design Gateway)

使用 512 GB 的 Samsung 970 Pro 時,在 ZCU102 上運行演示系統的示例測試結果如圖 6 所示。

圖 6:使用 Samsung 970 PRO S 時,ZCU102 上 NVMe SSD 的讀/寫性能。(圖片來源:Design Gateway)

總結

NVMeG3-IP 內核提供了一個在 ZCU102 評估套件上實現 NVMe SSD 接口的解決方案;同時也為不含 PCIe 集成塊的 Xilinx Zynq UltraScale+ MPSoC 器件系列提供了解決方案。NVMeG3-IP 的設計目標是在不使用 CPU 的情況下,以最低的 FPGA 資源使用量實現 NVMe SSD 訪問的最高性能。它非常適合不使用 CPU 的高性能 NVMe 存儲,能夠利用 GTH 收發器實現多個 NVMe SSD 接口,而不受 FPGA 器件上包含的 PCIe 集成模塊數量限制。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636320 -

存儲器

+關注

關注

39文章

7739瀏覽量

171675 -

SSD

+關注

關注

21文章

3111瀏覽量

122232

原文標題:在 Xilinx ZCU102 評估套件上實現 NVMe SSD 接口

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

在Xilinx ZCU102評估套件上實現NVMe SSD接口

在Xilinx ZCU102評估套件上實現NVMe SSD接口

評論