芯片封裝,簡單點(diǎn)來講就是把制造廠生產(chǎn)出來的集成電路裸片放到一塊起承載作用的基板上,再把管腳引出來,然后固定包裝成為一個(gè)整體。它可以起到保護(hù)芯片的作用,相當(dāng)于是芯片的外殼,不僅能固定、密封芯片,還能增強(qiáng)其電熱性能。所以,封裝對(duì) CPU 和其他大規(guī)模集成電路起著非常重要的作用。

介紹一下幾種常見的芯片封裝類型。

DIP 雙列直插式

DIP 是指采用雙列直插形式封裝的集成電路芯片,絕大多數(shù)中小規(guī)模集成電路均采用這種封裝形式,其引腳數(shù)一般不超過 100 個(gè)。采用 DIP 封裝的 CPU 芯片有兩排引腳,需要插入到具有 DIP 結(jié)構(gòu)的芯片插座上。當(dāng)然,也可以直接插在有相同焊孔數(shù)和幾何排列的電路板上進(jìn)行焊接。DIP 封裝的芯片在從芯片插座上插拔時(shí)應(yīng)特別小心,以免損壞引腳。

DIP 封裝結(jié)構(gòu)形式有多層陶瓷雙列直插式 DIP,單層陶瓷雙列直插式 DIP,引線框架式 DIP(含玻璃陶瓷封接式,塑料包封結(jié)構(gòu)式,陶瓷低熔玻璃封裝式)等。

DIP 是最普及的插裝型封裝,應(yīng)用范圍包括標(biāo)準(zhǔn)邏輯 IC,存儲(chǔ)器和微機(jī)電路等。

特點(diǎn):

適合在 PCB(印刷電路板)上穿孔焊接,操作方便。

芯片面積與封裝面積之間的比值較大,故體積也較大。

最早的 4004、8008、8086、8088 等 CPU 都采用了 DIP 封裝,通過其上的兩排引腳可插到主板上的插槽或焊接在主板上。

在內(nèi)存顆粒直接插在主板上的時(shí)代,DIP 封裝形式曾經(jīng)十分流行。DIP 還有一種派生方式 SDIP(Shrink DIP,緊縮雙入線封裝),它比 DIP 的針腳密度要高六倍。

現(xiàn)狀:

但是由于其封裝面積和厚度都比較大,而且引腳在插拔過程中很容易被損壞,可靠性較差。同時(shí)這種封裝方式由于受工藝的影響,引腳一般都不超過 100 個(gè)。隨著 CPU 內(nèi)部的高度集成化,DIP 封裝很快退出了歷史舞臺(tái)。只有在老的 VGA/SVGA 顯卡或 BIOS 芯片上可以看到它們的“足跡”。

PQFP/PFP 封裝

PQFP 封裝的芯片四周均有引腳,引腳之間距離很小,管腳很細(xì),一般大規(guī)模或超大型集成電路都采用這種封裝形式,其引腳數(shù)一般在 100 個(gè)以上。

用這種形式封裝的芯片必須采用 SMT(表面組裝技術(shù))將芯片與主板焊接起來。采用 SMT 安裝的芯片不必在主板上打孔,一般在主板表面上有設(shè)計(jì)好的相應(yīng)管腳的焊點(diǎn)。將芯片各腳對(duì)準(zhǔn)相應(yīng)的焊點(diǎn),即可實(shí)現(xiàn)與主板的焊接。

PFP 方式封裝的芯片與 PQFP 方式基本相同。唯一的區(qū)別是 PQFP 一般為正方形,而 PFP 既可以是正方形,也可以是長方形。

特點(diǎn):

PQFP 封裝適用于 SMT 表面安裝技術(shù)在 PCB 上安裝布線,適合高頻使用,它具有操作方便、可靠性高、工藝成熟、價(jià)格低廉等優(yōu)點(diǎn)。

現(xiàn)狀:

PQFP 封裝的缺點(diǎn)也很明顯,由于芯片邊長有限,使得 PQFP 封裝方式的引腳數(shù)量無法增加,從而限制了圖形加速芯片的發(fā)展。平行針腳也是阻礙 PQFP 封裝繼續(xù)發(fā)展的絆腳石,由于平行針腳在傳輸高頻信號(hào)時(shí)會(huì)產(chǎn)生一定的電容,進(jìn)而產(chǎn)生高頻的噪聲信號(hào),再加上長長的針腳很容易吸收這種干擾噪音,就如同收音機(jī)的天線一樣,幾百根“天線”之間互相干擾,使得 PQFP 封裝的芯片很難工作在較高頻率下。

此外,PQFP 封裝的芯片面積 / 封裝面積比過小,也限制了 PQFP 封裝的發(fā)展。90 年代后期,隨著 BGA 技術(shù)的不斷成熟,PQFP 終于被市場淘汰。

PGA(插針網(wǎng)格陣列)封裝

PGA 封裝的芯片內(nèi)外有多個(gè)方陣形的插針,每個(gè)方陣形插針沿芯片的四周間隔一定距離排列,根據(jù)管腳數(shù)目的多少,可以圍成 2~5 圈。安裝時(shí),將芯片插入專門的 PGA 插座。為了使得 CPU 能夠更方便的安裝和拆卸,從 486 芯片開始,出現(xiàn)了一種 ZIF CPU 插座,專門用來滿足 PGA 封裝的 CPU 在安裝和拆卸上的要求。該技術(shù)一般用于插拔操作比較頻繁的場合之下。

特點(diǎn):

⒈插拔操作更方便,可靠性高。

⒉可適應(yīng)更高的頻率。

BGA(球柵陣列)封裝

隨著集成技術(shù)的進(jìn)步、設(shè)備的改進(jìn)和深亞微米技術(shù)的使用,LSI、VLSI、ULSI 相繼出現(xiàn),硅單芯片集成度不斷提高,對(duì)集成電路封裝要求更加嚴(yán)格,I/O 引腳數(shù)急劇增加,功耗也隨之增大,當(dāng) IC 的頻率超過 100MHZ 時(shí),傳統(tǒng)封裝方式可能會(huì)產(chǎn)生所謂的“CrossTalk”現(xiàn)象,而且當(dāng) IC 的管腳數(shù)大于 208 Pin 時(shí),傳統(tǒng)的封裝方式有其困難度。為滿足發(fā)展的需要,在原有封裝品種基礎(chǔ)上,又增添了新的品種——球柵陣列封裝,簡稱 BGA。

BGA 封裝的 I/O 端子以圓形或柱狀焊點(diǎn)按陣列形式分布在封裝下面。

特點(diǎn):

1.I/O 引腳數(shù)雖然增多,但引腳間距遠(yuǎn)大于 QFP,從而提高了組裝成品率。

2. 雖然它的功耗增加,但 BGA 能用可控塌陷芯片法焊接,簡稱 C4 焊接,從而可以改善它的電熱性能。

3. 厚度比 QFP 減少 1/2 以上,重量減輕 3/4 以上。

4. 寄生參數(shù)減小,信號(hào)傳輸延遲小,使用頻率大大提高。

5. 組裝可用共面焊接,可靠性高。

6.BGA 封裝仍與 QFP、PGA 一樣,占用基板面積過大。

QFP(方型扁平式)封裝

該技術(shù)實(shí)現(xiàn)的 CPU 芯片引腳之間距離很小,管腳很細(xì),一般大規(guī)模或超大規(guī)模集成電路采用這種封裝形式,其引腳數(shù)一般都在 100 以上。

特點(diǎn):

1. 適用于 SMD 表面安裝技術(shù)在 PCB 電路板上安裝布線。

2. 適合高頻使用。

3. 操作方便,可靠性高。

4. 芯片面積與封裝面積之間的比值較小。

QFN 封裝類型

QFN 是一種無引線四方扁平封裝,是具有外設(shè)終端墊以及一個(gè)用于機(jī)械和熱量完整性暴露的芯片墊的無鉛封裝。

該封裝可為正方形或長方形。封裝四側(cè)配置有電極觸點(diǎn),由于無引腳,貼裝占有面積比 QFP 小,高度 比 QFP 低。

特點(diǎn):

1. 表面貼裝封裝,無引腳設(shè)計(jì)。

2. 無引腳焊盤設(shè)計(jì)占有更小的 PCB 面積。

3. 組件非常薄(《1mm),可滿足對(duì)空間有嚴(yán)格要求的應(yīng)用。

4. 非常低的阻抗、自感,可滿足高速或者微波的應(yīng)用。

5. 具有優(yōu)異的熱性能,主要是因?yàn)榈撞坑写竺娣e散熱焊盤。

6. 重量輕,適合便攜式應(yīng)用。

QFN 封裝的小外形特點(diǎn),可用于筆記本電腦、數(shù)碼相機(jī)、個(gè)人數(shù)字助理(PDA)、移動(dòng)電話和 MP3 等便攜式消費(fèi)電子產(chǎn)品。從市場的角度而言,QFN 封裝越來越多地受到用戶的關(guān)注,考慮到成本、體積各方面的因素,QFN 封裝將會(huì)是未來幾年的一個(gè)增長點(diǎn),發(fā)展前景極為樂觀。

LCC 封裝

LCC 封裝的形式是為了針對(duì)無針腳芯片封裝設(shè)計(jì)的,這種封裝采用貼片式封裝,它的引腳在芯片邊緣地步向內(nèi)彎曲,緊貼芯片,減小了安裝體積。但是這種芯片的缺點(diǎn)是使用時(shí)調(diào)試和焊接都非常麻煩,一般設(shè)計(jì)時(shí)都不直接焊接到印制線路板上,而是使用 PGA 封裝的結(jié)構(gòu)的引腳轉(zhuǎn)換座焊接到印制線路板上,再將 LCC 封裝的芯片安裝到引腳轉(zhuǎn)換座的 LCC 結(jié)構(gòu)形式的安裝槽中,這樣的芯片就可隨時(shí)拆卸,便于調(diào)試。

COB 封裝

COB 封裝全稱板上芯片封裝,是為了解決 LED 散熱問題的一種技術(shù)。相比直插式和 SMT 其特點(diǎn)是節(jié)約空間、簡化封裝作業(yè),具有高效的熱管理方式。

COB 封裝是將裸芯片用導(dǎo)電或非導(dǎo)電膠粘附在互連基板上,然后進(jìn)行引線鍵合實(shí)現(xiàn)其電氣連接。如果裸芯片直接暴露在空氣中,易受污染或人為損壞,影響或破壞芯片功能,于是就用膠把芯片和鍵合引線包封起來。

SO 類型封裝

SO 類型封裝包含有:SOP(小外形封裝)、TOSP(薄小外形封裝)、SSOP (縮小型 SOP)、VSOP(甚小外形封裝)、SOIC(小外形集成電路封裝)等類似于 QFP 形式的封裝,只是只有兩邊有管腳的芯片封裝形式,該類型的封裝是表面貼裝型封裝之一,引腳從封裝兩側(cè)引出呈“ L” 字形。

該類型的封裝的典型特點(diǎn)就是在封裝芯片的周圍做出很多引腳,封裝操作方便,可靠性比較高,是目前的主流封裝方式之一,目前比較常見的是應(yīng)用于一些存儲(chǔ)器類型的 IC。

SIP 封裝

SIP 封裝是將多種功能芯片,包括處理器、存儲(chǔ)器等功能芯片集成在一個(gè)封裝內(nèi),從而實(shí)現(xiàn)一個(gè)基本完整的功能。與 SOC 相對(duì)應(yīng)。不同的是系統(tǒng)級(jí)封裝是采用不同芯片進(jìn)行并排或疊加的封裝方式,而 SOC 則是高度集成的芯片產(chǎn)品。從封裝發(fā)展的角度來看,SIP 是 SOC 封裝實(shí)現(xiàn)的基礎(chǔ)。

SiP 的應(yīng)用非常廣泛,主要包括:無線通訊、汽車電子、醫(yī)療電子、計(jì)算機(jī)、軍用電子等。

3D 封裝

3D 晶圓級(jí)封裝,包括 CIS 發(fā)射器、MEMS 封裝、標(biāo)準(zhǔn)器件封裝。是指在不改變封裝體尺寸的前提下,在同一個(gè)封裝體內(nèi)于垂直方向疊放兩個(gè)以上芯片的封裝技術(shù),它起源于快閃存儲(chǔ)器(NOR/NAND)及 SDRAM 的疊層封裝。

3D 封裝主要特點(diǎn)包括:多功能、高效能;大容量高密度,單位體積上的功能及應(yīng)用成倍提升以及低成本。

分類:

一:封裝趨勢是疊層封(PoP);低產(chǎn)率芯片似乎傾向于 PoP。

二:多芯片封裝(MCP)方法,而高密度和高性能的芯片則傾向于 MCP。

三:以系統(tǒng)級(jí)封裝(SiP)技術(shù)為主,其中邏輯器件和存儲(chǔ)器件都以各自的工藝制造,然后在一個(gè) SiP 封裝內(nèi)結(jié)合在一起。

目前的大多數(shù)閃存都采用多芯片封裝(MCP,Multichip Package),這種封裝,通常把 ROM 和 RAM 封裝在一塊兒。多芯封裝(MCP)技術(shù)是在高密度多層互連基板上,采用微焊接、封裝工藝將構(gòu)成電子電路的各種微型元器件(裸芯片及片式元器件)組裝起來,形成高密度、高性能、高可靠性的微電子產(chǎn)品(包括組件、部件、子系統(tǒng)、系統(tǒng))。

責(zé)任編輯:tzh

-

芯片

+關(guān)注

關(guān)注

463文章

54017瀏覽量

466330 -

cpu

+關(guān)注

關(guān)注

68文章

11281瀏覽量

225095 -

DIP

+關(guān)注

關(guān)注

0文章

255瀏覽量

31979

發(fā)布評(píng)論請先 登錄

芯片封裝選真空共晶爐,選對(duì)廠家超關(guān)鍵!近 70%的封裝良率問題源于設(shè)備選型不當(dāng)。那咋選呢?

不同類型功放芯片對(duì)音箱音質(zhì)的核心影響

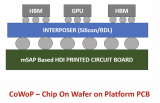

簡單認(rèn)識(shí)CoWoP封裝技術(shù)

集成電路封裝類型介紹

詳解CSP封裝的類型與工藝

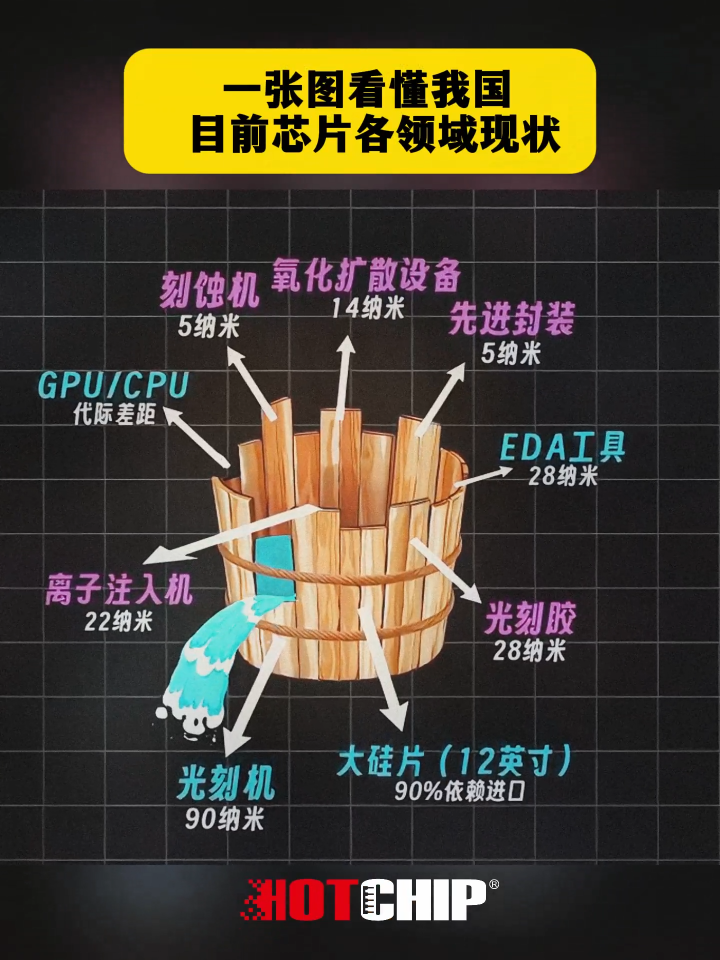

AI芯片封裝,選擇什么錫膏比較好?

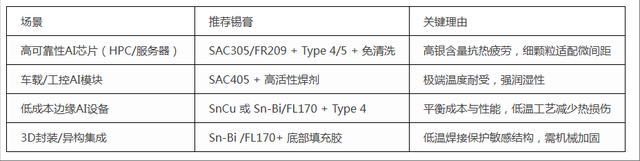

華芯邦教你一圖看懂中國半導(dǎo)體的長板與短板 #華芯邦 #半導(dǎo)體 #芯片現(xiàn)狀 #集成電路 #芯片封裝 #

芯片背后的無名英雄:半導(dǎo)體晶圓的真、假、測試片三重身份大揭秘!#華芯邦 #半導(dǎo)體 #芯片封裝 #晶圓

尹志堯坦言:"光刻機(jī)的作用正在不斷減少!",芯片制造從追求更小制程到更重視先進(jìn)封裝 #芯片封裝 #華芯邦

如何判斷ADC芯片的類型?

如何通俗理解芯片封裝設(shè)計(jì)

對(duì)芯片封裝類型的認(rèn)識(shí)

對(duì)芯片封裝類型的認(rèn)識(shí)

評(píng)論