近年來,電子信息產業迅猛發展,為了追求電子產品的高性能及便捷性,集成電路規模不斷擴大,特征線寬不斷縮小,當前國際上的工藝已經進展 10 納米以下,7 納米已經量產,5 納米也已經試產,將于 2020 年正式量產。

成品率下滑已成為納米集成電路面臨的最大挑戰之一。而且,隨著集成電路產品的快速升級,特別是對人工智能、5G 移動通訊、物聯網、汽車電子方向應用需求的高性能、低功耗、高密度、可靠性及高度功能集成需求,促使各種新材料、新工藝、新器件的引進,為集成電路產品的設計制造帶來了前所未有的挑戰。這些因素大大增加了集成電路制造過程中的不確定性,使得集成電路產品的成品率更加難以控制。由于成品率問題的重要性,在當前的集成電路研發中,對成品率問題的考慮已滲透到集成電路設計、晶圓制造的各個階段。如何在研發高性能集成電路的同時,保證較高的成品率,一直是學術界及工業界關注的熱點問題。

首先,集成電路生產工藝十分復雜,一個芯片的產生往往要經過上百道甚至上千道工藝步驟,生產周期較長,在整個制造過程中任何一個工藝步驟上的偏差,都將會對產品成品率造成影響。尤其在 20 納米節點以后,采用多次曝光的浸入式光刻,大幅度增加了光刻和刻蝕的次數,對芯片成品率的影響劇增。目前采用非 EUV 光刻制作的 10 納米和 7 納米的工藝,刻蝕步數已經超過 100 次,一個偏差,成品率將有可能下降到 10%。

其次,集成電路生產線的投資巨大,先進生產線的造價更是驚人。現在 14 納米采用非 EUV 光刻,每萬片產能的投資高達 25 億美元。如果芯片成品率過低,難以付諸批量生產,投資成本將打水漂。

據晶圓代工廠的工程師表示,影響芯片成品率的因素有很多,但主要來自兩個大的方面:

第一是來自設計方面的影響,包括芯片設計參數和結構設計不合理,與相應的制造工藝特性不吻合,則會導致芯片性能上出現缺失,造成成品率過低。

第二是制造工藝缺陷或擾動對成品率的影響,包括金屬條變形、粉塵顆粒與冗余物的出現,或是工藝控制無法保證工藝窗口,都會對芯片成品率造成不可估量的影響。

對于如何提升芯片成品率,晶圓代工廠的工程師表示,提升芯片成品率的關鍵,是根據工藝及設計的具體情況,利用 EDA 工具通過對缺陷的統計分布情況進行分析和優化。而且根據工藝節點的不斷更迭,越先進的工藝其成品率越難以控制,成品率的重要性也越明顯。

成品率提升(Integrated yield ramp)EDA 軟件雖然是一個小眾市場,但是卻非常關鍵。隨著芯片研發及制造企業的競爭日趨激烈,成品率問題作為影響企業經濟效益的關鍵因素,已成為芯片設計及晶圓制造企業提高產品市場競爭力的重要砝碼。

事實上,進入 2000 年后,國內在成品率提升軟件方面開展了相當多的研究,如西安電子科技大學在缺陷導致的集成電路功能成品率問題方面的研究、浙江大學在利用光學校正技術(OPC)改善集成電路成品率的研究等都取得較好的成果。但始終沒有市場化。

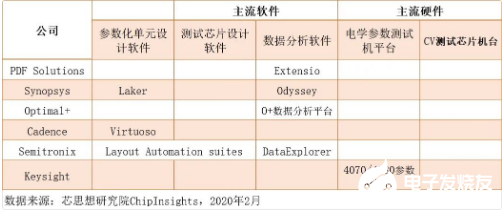

芯思想研究院在調研中發現,業界大廠除臺積電、英特爾各擁有一支強大的成品率團隊可以自主進行先進成品率管理以外,其他的晶圓制造廠的成品率提升和管理都需要較多借助外力。目前主流國際市場上,集成電路產業界較普遍采用的和成品率提升相關的關鍵軟件、硬件提供商有 PDF Solutions、Semitronix、Synopsys、Cadence、Optimal+、Keysight 等。

以下是國際主流晶圓制造廠使用的一些主流軟硬件。

Synopsys、Cadence 是全球知名的 EDA 工具提供商,其參數化單元設計軟件廣泛應用于集成電路設計領域,這其中也包括成品率提升方面。Keysight 是德科技是全球領先的測量儀器公司,為電子設計、電動汽車、網絡監控、物聯網、智能互聯汽車等提供測試解決方案。在這里就不多做介紹。

下面我們簡單介紹下 PDF Solutions 和 Optimal+。

PDF Solutions

PDF Solutions, Inc. 成立于 1991 年,總部在美國硅谷,是一家具有 30 年行業經驗的半導體產業跨界整合技術服務公司,致力于為 IC 設計公司驗證及改善設計,順利完成流片、生產到產品上市;以及為晶圓代工廠定位工藝問題,提升新技術開發能力,完善工藝流程控制。PDF Solutions 的技術服務包括集成電路前沿工藝的開發,包括基于客戶定制測試芯片(Characterization Vehicle)的良率改良咨詢,可制造性設計優化(Design for Manufacturability),以及半導體大數據平臺 Exensio Platform 等工具。其中 Exensio 平臺包含用于半導體設備生產的故障檢測與分類(Fault Detection and Classification, Exensio-Control)模塊,產品測試優化模塊(Exensio-Test),半導體良率管理系統模塊(Exensio-Yield)等等。

PDF Solutions 提供從技術研發到產品設計,從工藝制造到封裝測試,從試驗流片到成熟量產,的整套成熟技術服務,有效幫助廠商降低 IC 設計和制造成本,顯著提高產品質量和生產效率,進而加快產品上市速度和提升利潤空間。

Optimal+

Optimal+是以色列一家大數據分析服務商,成立于 2005 年,為半導體和電子產業提供可操作性的制造和測試數據分析,其成品率業務僅涵蓋數據分析這一塊內容。但是其營收主要來自于電子行業,半導體產業為其貢獻的營收僅約占其總營收入 20%,且占比呈現逐年下滑狀態。公司未來在半導體產業的機會不大,原因在于公司僅僅只提供軟件,沒有硬件支持。

芯思想研究院在調研中還發現,杭州廣立微電子有限公司(Semitronix)是國內一家以集成電路成品率為主營業務的企業,已經開發成功成品率提升相關軟硬件工具。

隨著近年來中國半導體行業發展環境的持續利好以及國內半導體企業的成長,大家對于技術、質量、效率的要求越來越高,很多國內領先的集成電路設計公司和晶圓生產廠商已經和國際接軌。

成品率提升軟件市場規模

據中芯國際、華虹集團、三星電子的工程師表示,從 2017 年就開始采用廣立微提供的新工藝制程研發提供整合性服務,包括早期工藝開發、產品設計流程確立、中后期產品量產時的可尋址測試結構,直到 yield ramp 階段基于產品版圖的測試芯片。

韓國頂級半導體公司代工部門的技術人員表示,廣立微提供的基于測試芯片的軟、硬件系統產品以及整體解決方案用于高效測試芯片自動設計、高速電學測試和智能數據分析的全流程平臺,利用特有的流程平臺與技術方法可以提高集成電路性能、良率、穩定性和產品上市速度的定制服務。公司代工部門的技術人員表示,基于廣立微的軟硬件的實用性和成本效益,向公司存儲業務部門進行了推薦,現在公司存儲業務也已經開始采購廣立微的產品。該公司代工部門的技術人員還表示,由于之前歐美國家成品率方案供應商的市場壟斷性,業界一直不太歡迎其商業模式。這一說法得到臺積電、聯電、中芯國際等多家晶圓代工廠的認可。

根據 WSTS 的數據,2019 年全球半導體芯片產業的營收超過 4000 億美元。而根據三大 EDA 廠商的營收數據,預估 2019 年全球 EDA 市場約為 96 億美元。

芯思想研究院根據調研數據發現,全球各大晶圓制造廠每家每年在成品率提升軟件方面的投入約在 50 萬美元。而晶圓代工公司的投入規模要大一些,一般在 200-300 萬美元,高的在 700 萬美元。

根據不完全統計,全球成品率提升 EDA 軟件規模整體在 8000 萬美元到 9000 萬美元之間。按照地域來看,2019 年美洲約 1800 萬美元至 2000 萬美元、歐洲約 400 萬美元至 500 萬美元、亞洲(不含中國)約 2500 萬元至 3000 萬美元、中國(包括臺灣)約 3300 萬美元至 3500 美元。

預估未來幾年的全球市場成長有限,預計到 2025 年市場規模望達 1.0-1.1 億美元。但得益于國內晶圓制造業的成長,加上未來國內興建的多座 FAB,國內的市場是有增無減,預計 2025 年中國(包括臺灣)的市場將接近 6000 萬美元,這將為國產成品率提升軟件拓展國內的市場提供機會。

注:這是芯思想研究院第二次針對 EDA 軟件細分市場進行調研,第一次是 2019 年推出的制造專用軟件調研,由于經驗不足,數據僅供參考!

-

芯片

+關注

關注

463文章

54010瀏覽量

466068 -

集成電路

+關注

關注

5452文章

12572瀏覽量

374548 -

eda

+關注

關注

72文章

3113瀏覽量

182912

發布評論請先 登錄

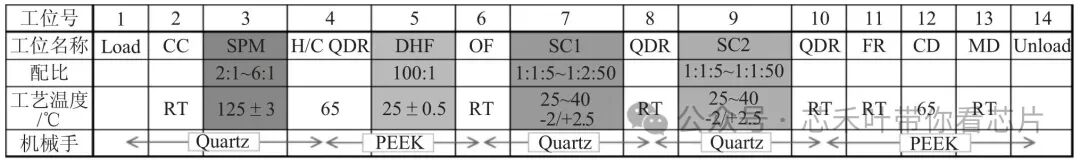

集成電路制造中常用濕法清洗和腐蝕工藝介紹

國內首條碳基集成電路生產線正式投產運營

混合集成電路(HIC)芯片封裝中真空回流爐的選型指南

電機控制專用集成電路PDF版

中國集成電路大全 接口集成電路

探秘 12 寸集成電路制造潔凈室的防震 “魔法”

大規模硬件仿真系統的編譯挑戰

集成電路芯片切割新趨勢:精密劃片機成行業首選

集成電路規模不斷擴大 影響芯片成品率的因素有很多

集成電路規模不斷擴大 影響芯片成品率的因素有很多

評論