模擬信號(hào)隔離是電動(dòng)汽車、工業(yè)控制、PLC、電機(jī)驅(qū)動(dòng)、電源、逆變器等領(lǐng)域的常用技術(shù),常規(guī)的解決方案有線性光耦、隔離運(yùn)放等,不過價(jià)格上略偏高昂、電路也較為復(fù)雜,有些精度也不夠,總體來說,應(yīng)用中不算太友好。

為了獲得更低成本的解決方案,大多數(shù)工程師會(huì)選擇PWM來實(shí)現(xiàn)模擬信號(hào)的隔離傳輸。比如下圖:

這種解決方案分為三步:

第一、將PWM信號(hào)經(jīng)過光耦隔離后輸出PWM_ISO信號(hào)。其中PWM_ISO信號(hào)的高電平為基準(zhǔn)電壓VREF。第二步用二階RC濾波電路過濾PWM_ISO信號(hào)輸出電壓信號(hào)VLPF。第三步,VLPF信號(hào)經(jīng)過經(jīng)過運(yùn)放放大后輸出目標(biāo)電壓VOUT。這是一個(gè)非常容理解和實(shí)現(xiàn)的方案,也被廣泛的使用,不過此電路也有其短板。

缺點(diǎn)一,光耦傳輸PWM信號(hào)會(huì)引入失真,尤其光耦對(duì)溫度敏感,對(duì)策有兩個(gè),使用高速光耦或者將輸入PWM的頻率盡可能的變低,前者價(jià)格較高而后者會(huì)極大的增加傳輸時(shí)延。

缺點(diǎn)二,第二步中為了獲得干凈的VLPF電壓,需要較大的RC值來進(jìn)行濾波,PWM頻率越低,需要的RC越大,信號(hào)的傳輸速度也就越慢。

缺點(diǎn)三,假設(shè)PWM的占空比為Duty,則最終輸出的VOUT=VREF*Duty*(R1+R2)/R2,上式可以得出VOUT的精度決定于VREF、(R1+R2)/R2、Duty三者,假設(shè)Duty精度可以通過高速光耦來實(shí)現(xiàn),那么高精度的輸出還需要高精度的VREF和電阻才能實(shí)現(xiàn),所以當(dāng)用這個(gè)電路實(shí)現(xiàn)高精度的PWM轉(zhuǎn)電壓時(shí),對(duì)各個(gè)器件的要求較高,成本也較高。

客益電子推出的模擬信號(hào)隔離方案是基于APC芯片和PAC芯片技術(shù)。所謂APC芯片是將模擬信號(hào)線性轉(zhuǎn)換成PWM信號(hào),相對(duì)的,所謂PAC芯片是將PWM信號(hào)轉(zhuǎn)換成模擬信號(hào)。

下圖為APC芯片GP9303:

APC芯片GP9303的輸入端VIN的電壓范圍是0-5V,其輸出的PWM信號(hào)的占空比為Duty=VIN/5V。將0-5V的輸入電壓轉(zhuǎn)換為0%-100%的PWM信號(hào)輸出。

下圖為PAC芯片GP8101:

PAC芯片GP8101的輸入端PWM信號(hào)的占空比范圍為0%-100%,其輸出電壓信號(hào)VOUT=Duty*5V。將0%-100%的PWM輸入信號(hào)轉(zhuǎn)換為0-5V電壓輸出。

通過APC和PAC芯片的組合可以非常容易的實(shí)現(xiàn)模擬信號(hào)隔離,包括PWM與模擬信號(hào)隔隔離轉(zhuǎn)換。通常工程師經(jīng)常會(huì)遇到三類功能需求:

隔離ADC功能

隔離DAC功能

模擬信號(hào)隔離功能

第一種隔離ADC功能可以通過下圖方式實(shí)現(xiàn),通過APC芯片GP9303將模擬信號(hào)0-5V轉(zhuǎn)換成0%-100%的PWM信號(hào),輸出的PWM信號(hào)經(jīng)過光耦隔離后被MCU采集,從而實(shí)現(xiàn)隔離ADC的作用。

第二種隔離DAC的功能可以通過下圖方式實(shí)現(xiàn),MCU輸出PWM信號(hào),經(jīng)過光耦隔離后輸出給PAC芯片GP8101或者GP8102等,PAC芯片直接輸出0-10V、4-20mA等模擬量,其中輸出值與PWM占空比呈線性關(guān)系。

第三種模擬信號(hào)隔離功能有兩種方法實(shí)現(xiàn),一種使用光耦作為隔離媒介,APC芯片GP9303將模擬信號(hào)轉(zhuǎn)換成PWM,PAC芯片GP8101將PWM信號(hào)轉(zhuǎn)換成模擬信號(hào),中間通過光耦隔離。另一種方法是APC芯片GP9303M將模擬信號(hào)轉(zhuǎn)換成PWM高頻調(diào)制信號(hào),PAC芯片GP8101M將高頻調(diào)制PWM信號(hào)解調(diào)后還原成模擬信號(hào)輸出,中間用電容來隔離。

下圖為光耦隔離方案

下圖為電容隔離方案,電容隔離方案電路簡(jiǎn)單,成本低廉,是非常有競(jìng)爭(zhēng)力的解決方案。

發(fā)布評(píng)論請(qǐng)先 登錄

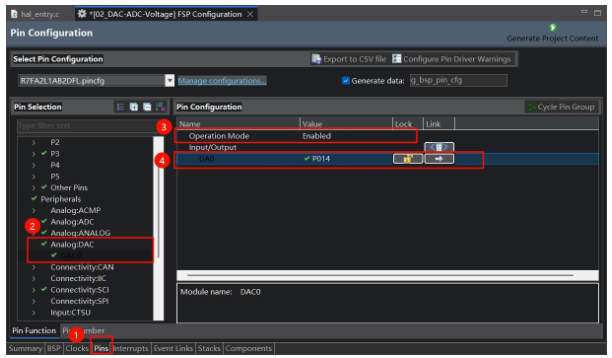

RA MCU眾測(cè)寶典 | ADC/DAC之【RA2L1】DAC電壓輸出及ADC電壓采集實(shí)驗(yàn)

【瑞薩FPB-RA6E2試用】【FPB-RA6E2】 DAC-ADC 回環(huán)測(cè)試:基于 Zephyr RTOS 的模擬信號(hào)通路驗(yàn)證

【瑞薩FPB-RA6E2試用】【瑞薩RA × Zephyr開發(fā)板評(píng)測(cè)】ADC、DAC、SPI、I2C 測(cè)試

【瑞薩RA6E2地奇星開發(fā)板試用】DAC 輸出指定電壓、ADC 電壓檢測(cè)

高端APx555B——ADC/DAC芯片測(cè)試的極佳選擇

ADC/DAC工作原理與常見應(yīng)用解析

【瑞薩RA6E2】ADC、DAC 電壓輸入輸出

【RA4M2-SENSOR】ADC、DAC 電壓輸入輸出

廣州唯創(chuàng)WT2003H錄音芯片-高精度ADC/DAC+64mA驅(qū)動(dòng)MP3音頻芯片

【RA4E2開發(fā)板評(píng)測(cè)】ADC、DAC 電壓輸入輸出

如何減小DAC電路的耦合影響?

【RA-Eco-RA6M4開發(fā)板評(píng)測(cè)】ADC、DAC 電壓輸入輸出

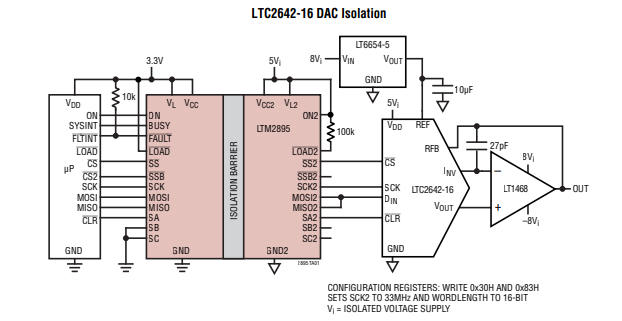

LTM2895 100MHz隔離型DAC SPI串行接口技術(shù)手冊(cè)

如何為ADC增加隔離而不損害其性能呢?

如何使用FPGA驅(qū)動(dòng)并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時(shí)的注意事項(xiàng)

隔離DAC/ADC有哪些選擇? APC&PAC芯片

隔離DAC/ADC有哪些選擇? APC&PAC芯片

評(píng)論