在近期舉行的中國開源峰會OSC源創會·年終盛典上,華為方舟編譯器獲得“最有價值開源項目”稱號。

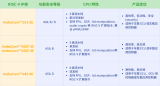

據介紹,方舟編譯器從根源上改變了執行模式,Java程序通過語言前端解析處理,生成Maple IR,經過語言特性實現,進入優化中端,生成后端代碼。憑借多語言聯合優化、輕量運行時,高效內存回收機制、多硬件平臺支持、軟硬件聯合優化協同四大技術亮點,方舟編譯器自上線后很快創造了「碼云中國開源史上最快達到5K Star 」記錄。

中科院軟件所智能軟件中心程序語言與編譯技術實驗室開發了方舟編譯器Runtime開源參考實現——Toy Runtime。并表示方舟編譯器有望實現RISC-V芯片支持 。

責任編輯:gt

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

華為

+關注

關注

218文章

36005瀏覽量

262106 -

JAVA

+關注

關注

20文章

3001瀏覽量

116434 -

編譯器

+關注

關注

1文章

1672瀏覽量

51612 -

RISC-V

+關注

關注

48文章

2886瀏覽量

53012 -

方舟編譯器

+關注

關注

0文章

63瀏覽量

767

發布評論請先 登錄

相關推薦

熱點推薦

OrangePi RV2 深度技術評測:RISC-V AI融合架構的先行者

3.2 開發工具與庫

編譯器 :支持GCC、LLVM(RISC-V 后端)

AI 框架 :官方宣稱適配DeepSeek、TensorFlow Lite、PyTorch,但需驗證模型轉換與算子

發表于 03-03 20:19

RISC-V不支持 Nx嗎?

RISC-V architecture! · nrwl/nx · Discussion #27915

如果能夠支持 RISC-V,那就太好了。目前我無法在我的 VisionFive2 板上

發表于 02-04 06:27

重磅合作!Quintauris 聯手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

之后,要打造的是高可靠性、高能效還支持可擴展的 RISC-V 設計方案。而且合作的核心目標特別明確:

讓 RISC-V 處理器在嵌入式、物聯網、AI 系統里更快普及;

用集成式 IP

發表于 12-18 12:01

探索RISC-V在機器人領域的潛力

的硬件配置給人留下了深刻的第一印象:

? 核心處理器: 搭載了進迭時空的K1系列高性能RISC-V處理器,具備強大的通用計算能力和AI加速特性。

? 內存與存儲: 板載LPDDR4

發表于 12-03 14:40

RISC-V 蜂鳥E203中PC指針起始地址設置搭建

具體方法

這篇分享中RISC-V 蜂鳥E203平臺是在Arty A7 100T上進行的搭建,ddr 200t的板子上是有2塊qspi flash的,所有FPGA的bitstream燒錄在了

發表于 10-28 07:47

提高RISC-V在Drystone測試中得分的方法

性能:內存的讀寫速度、延遲和帶寬等都會影響到 Drystone 的性能。

指令集優化:對RISC-V指令集的優化也會影響性能。例如,對于特定的應用或計算任務,可以通過定制指令集來提高性能。

編

發表于 10-21 13:58

全球首款RiSC-V企業級模擬平臺,躍昉科技LeapEMU正式亮相

9月19日,廣東躍昉科技在珠海舉辦的“RISC-V軟件生態研討會上”,公司正式發布了全球首款支持超128核RiSC-V RVA23企業級模擬平臺LeapEMU。躍昉科技創始人兼CEO江

兆松科技ZCC-FuSa編譯器全面支持晶心科技車規級RISC-V處理器IP核

2025 年 8 月 26 日,兆松科技宣布其車規編譯器 ZCC-FuSa 全面支持 Andes 晶心科技各系列車規級的 AndesCore RISC-V CPU IP (D23-SE

RISC-V 發展態勢與紅帽系統適配進展

,硬件情況有了改善,紅帽也成為最早支持 RISC-V 系統的企業之一,當時已能搭建支持桌面的系統,這在當時是很大的突

發表于 07-18 10:55

?4071次閱讀

RISC-V 的平臺思維和生態思維

RISC-V 的平臺思維時指出,平臺思維指的是硬件(CPU、加速器、總線等)、固件和軟件的整體集成。標準化 ISA 配置文件是必要的

發表于 07-17 14:04

?4186次閱讀

兆松科技發布高性能RISC-V編譯器ZCC 4.0.0版本

近日,兆松科技(武漢)有限公司(以下簡稱“兆松科技”)宣布正式發布高性能 RISC-V 編譯器 ZCC 4.0.0 版本。新版本在性能優化、廠商自定義指令支持和軟件庫等方面實現全面升級,并同步推出

兆松科技ZCC編譯器全面支持芯來科技NA系列處理器

近日,兆松科技(武漢)有限公司(以下簡稱“兆松科技”)宣布正式發布高性能RISC-V編譯器ZCC 4.0.0版本。

RISC-V架構下的編譯器自動向量化

高性能算力生態的建設,正投入編譯器自動向量化優化等多項關鍵技術,全面助力RISC-V的高性能發展。RISC-V向量設計SpacemiT在現代CPU中,向量支持是算力的

大象機器人攜手進迭時空推出 RISC-V 全棧開源六軸機械臂產品

末端執行器。

全棧開源

從RISC-V指令集、芯片SDK到機器人控制代碼100%開放,開發者可自由定制算法與控制邏輯。

官方apt倉庫提供deepseek-r1-distill-qwen-1.5b

發表于 04-25 17:59

RISC-V的未來應走向何方

半導體行業正孜孜不倦地推動創新,在這個過程中,做出正確選擇,正成為芯片成功的關鍵因素。在眾多操作系統、編譯器、調試器和其他工具的選項中,開放的RISC-V指令集架構(ISA)正在加速普

華為方舟編譯器獲多硬件平臺支持,未來RISC-V芯片或也支持

華為方舟編譯器獲多硬件平臺支持,未來RISC-V芯片或也支持

評論