據(jù)消息,目前臺積電正在積極備戰(zhàn)5nm,華為已經(jīng)在考慮將5nm工藝用在其下一代旗艦芯片——麒麟1020上,預計明年第三季度上市。

報道中稱,華為麒麟1020將采用ARM Cortex-A78架構,得益于5nm工藝,麒麟1020每平方毫米可容納1.713億個晶體管,其性能較麒麟990提升50%,而高通驍龍865較前代驍龍855性能只提升了25%。

此外,蘋果A14處理器和麒麟1020處理器將是首批使用5nm工藝的旗艦芯片,而高通系的5nm芯片則要到2021年才能量產(chǎn)。

責任編輯:gt

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

臺積電

+關注

關注

44文章

5803瀏覽量

176328 -

華為

+關注

關注

218文章

36005瀏覽量

262106 -

晶體管

+關注

關注

78文章

10396瀏覽量

147762

發(fā)布評論請先 登錄

相關推薦

熱點推薦

LCD液晶面板激光修復工藝助力制程良率提升

一、引言 LCD液晶面板作為顯示產(chǎn)業(yè)的核心組件,其制程涵蓋陣列、成盒、模組組裝等多個復雜環(huán)節(jié),任一環(huán)節(jié)的微小缺陷都可能導致面板失效。當前,線路短路/開路、壞點、暗帶等制程缺陷是制約LCD面板良率

晶圓工藝制程清洗方法

晶圓工藝制程清洗是半導體制造的核心環(huán)節(jié),直接決定芯片良率與器件性能,需針對不同污染物(顆粒、有機物、金屬離子、氧化物)和制程需求,采用物理、化學、干法、復合等多類技術,適配從成熟

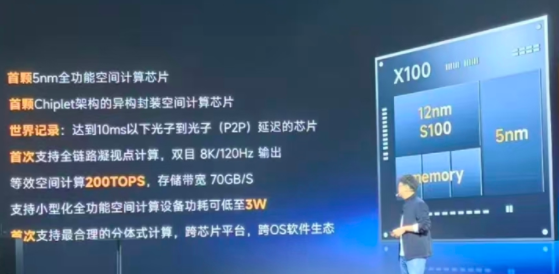

如何突破AI存儲墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構

6.0)支撐高性能 PCIe 5.0 SSD 存取

工藝覆蓋全制程 (包含 5nm, 8nm, 12

發(fā)表于 01-29 17:32

三星2nm良率提升至50%,2027年前實現(xiàn)晶圓代工業(yè)務盈利可期

據(jù)報道,三星電子第一代2nm GAA制程(SF2)良率已穩(wěn)定在50%,該數(shù)據(jù)也通過其量產(chǎn)的Exynos 2600處理器得到印證。

1.4nm制程工藝!臺積電公布量產(chǎn)時間表

供應一度面臨緊張局面。為應對市場激增的訂單,臺積電已啟動新建三座工廠的擴產(chǎn)計劃,旨在進一步提升產(chǎn)能,保障客戶供應鏈的穩(wěn)定交付。 ? 與此同時,臺積電在更尖端的1.4nm工藝研發(fā)上同樣進展迅猛。公司正全力加速推進1.4

三星發(fā)布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

)技術。相較于傳統(tǒng)的3nm FinFET工藝,GAA架構提供了更出色的靜電控制和更高的電流密度,使芯片性能提升12%,功

國產(chǎn)芯片真的 “穩(wěn)” 了?這家企業(yè)的 14nm 制程,已經(jīng)悄悄滲透到這些行業(yè)…

最近扒了扒國產(chǎn)芯片的進展,發(fā)現(xiàn)中芯國際(官網(wǎng)鏈接:https://www.smics.com)的 14nm FinFET 制程已經(jīng)不是 “實驗室技術” 了 —— 從消費電子的中端處理器,到汽車電子

發(fā)表于 11-25 21:03

三星公布首批2納米芯片性能數(shù)據(jù)

三星公布了即將推出的首代2nm芯片性能數(shù)據(jù);據(jù)悉,2nm工藝采用的是全柵極環(huán)繞(GAA)晶體管技術,相比第二代3nm

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創(chuàng)新將繼續(xù)維持著摩爾神話

個先例,其變化形式如圖6所示。

晶背供電技術已被證明,它可以很好地解決5nm以下芯片的電源完整性問題,同樣也證明

它是優(yōu)化特定版圖設計任務的用力工具。

圖6 功能性晶

隨著工藝創(chuàng)新的層出不窮,相信摩爾神話還能持續(xù),AI芯片也將為

發(fā)表于 09-06 10:37

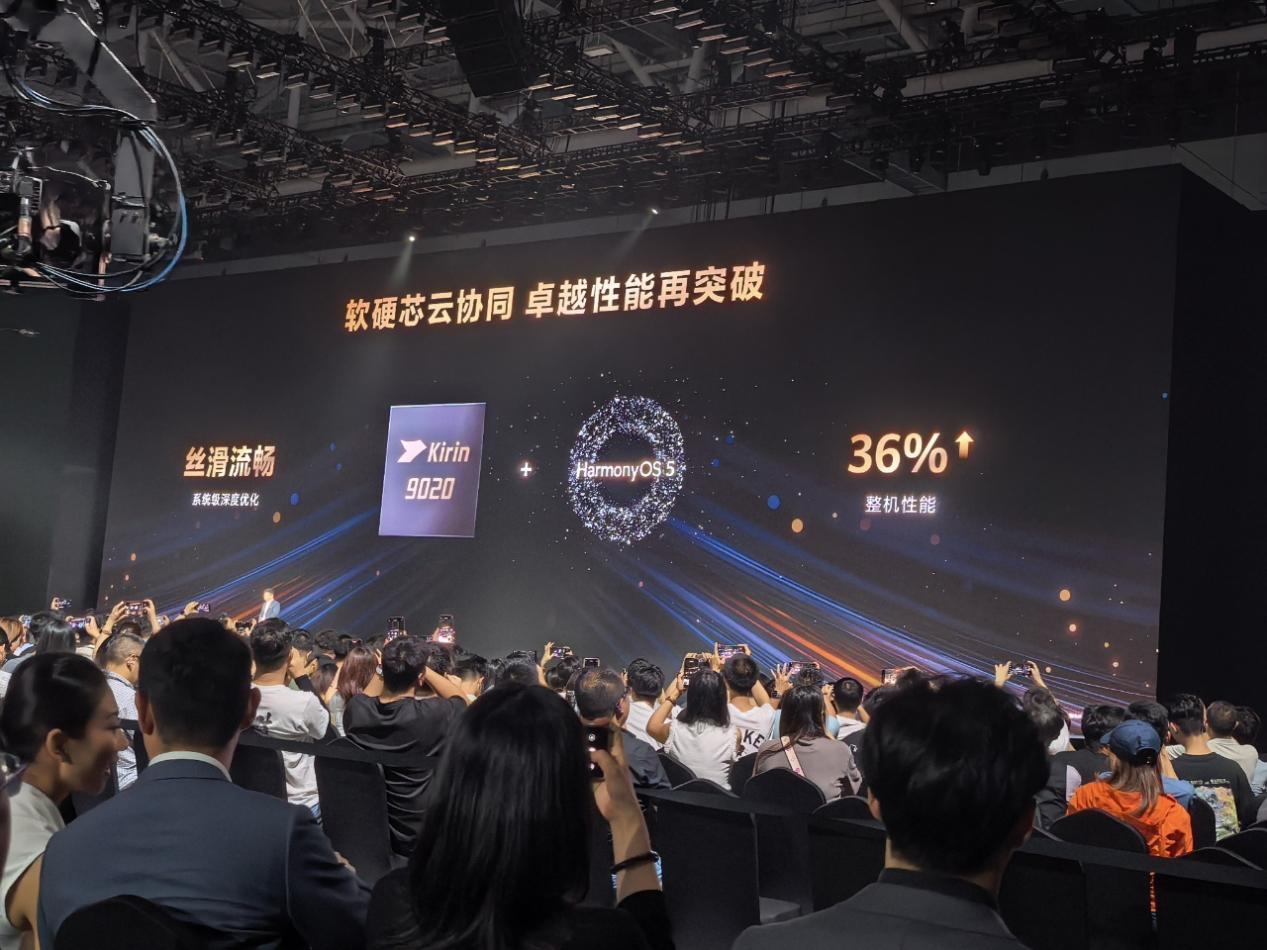

麒麟9020芯片!重磅官宣!

時隔四年重現(xiàn)華為發(fā)布會。 ? 華為Mate XTs 非凡大師搭載麒麟9020芯片,運行華為自研的HarmonyOS 5,軟硬芯云協(xié)同,系統(tǒng)級

從Ascend 910D看芯粒創(chuàng)新,半導體行業(yè)將迎重大變局

電子發(fā)燒友網(wǎng)報道(文/黃山明) 隨著芯片制程工藝向更先進節(jié)點推進,如從7nm邁向5nm,再到3nm,物理層面的技術瓶頸愈發(fā)凸顯,這使得行業(yè)在

快手上線鴻蒙應用高性能解決方案:數(shù)據(jù)反序列化性能提升90%

近日,快手在Gitee平臺上線了鴻蒙應用性能優(yōu)化解決方案“QuickTransformer”,該方案針對鴻蒙應用開發(fā)中廣泛使用的三方庫“class-transformer”進行了深度優(yōu)化,有效提升

發(fā)表于 05-15 10:01

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現(xiàn)流片成功

我們很高興能在此宣布,Cadence 基于 UCIe 標準封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實現(xiàn)首次流片成功。這一里程碑彰顯了我們持續(xù)提供高性能車規(guī)級 IP 解決方案?的承諾,可滿足新一代汽

臺積電2nm制程良率已超60%

,較三個月前技術驗證階段實現(xiàn)顯著提升(此前驗證階段的良率已經(jīng)可以到60%),預計年內即可達成量產(chǎn)準備。 值得關注的是,蘋果作為臺積電戰(zhàn)略合作伙伴,或將率先采用這一尖端制程。盡管廣發(fā)證券分析師Jeff Pu曾預測iPhone 18系列搭載的A20處理器仍將延續(xù)3

華為麒麟1020加入5nm工藝制程,其性能將提升50%

華為麒麟1020加入5nm工藝制程,其性能將提升50%

評論