基于LUT的FPGA具有很高的集成度,其器件密度從數萬門到數千萬門不等,可以完成極其復雜的時序與邏輯組合的邏輯電路功能,因此其適用于高速、高密度的高端數字邏輯電路設計領域。其組成部分主要有可編程輸入/輸出單元、基本可編程邏輯單元、內嵌SRAM、豐富的布線資源、底層嵌入功能單元、內嵌專用單元等。FPGA的主要設計和生產廠家有賽靈思、Altera、Lattice、Actel、Atmel和QuickLogic等,其中最大的是美國賽靈思公司,在可編程市場中占有50%以上的份額,比其他所有競爭對手市場份額的總和還多。

FPGA是由存放在片內RAM中的程序來設置其工作狀態的,因此,工作時需要對片內的RAM進行編程。用戶可以根據不同的配置模式,采用不同的編程方式。

目前,FPGA市場占有率最高的兩大公司——賽靈思公司和Altera生產的FPGA都是基于SRAM工藝的,需要在使用時外接一個片外存儲器以保存程序。上電時,FPGA將外部存儲器中的數據讀入片內RAM,完成配置后,進入工作狀態;掉電后SRAM存儲的數據丟失,內部邏輯消失。這樣,FPGA能反復使用,且無須專門的FPGA編程器,只需配備一片存儲代碼的FLASH存儲器即可。

Actel、QuickLogic等公司還提供反熔絲技術的FPGA,它具有抗輻射、耐高低溫、低功耗和速度快等優點,在軍品和航空航天領域中應用較多,但這種FPGA不能重復擦寫,開發初期比較麻煩,費用也比較昂貴。Lattice是ISP技術的發明者,在小規模PLD應用上有一定的特色。賽靈思公司的早期產品一般不涉及軍品和宇航級市場,但目前已經有多款產品進入該領域。

目前主流的FPGA仍是基于查找表技術的,已經遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、時鐘管理和DSP)的硬核(ASIC型)模塊。

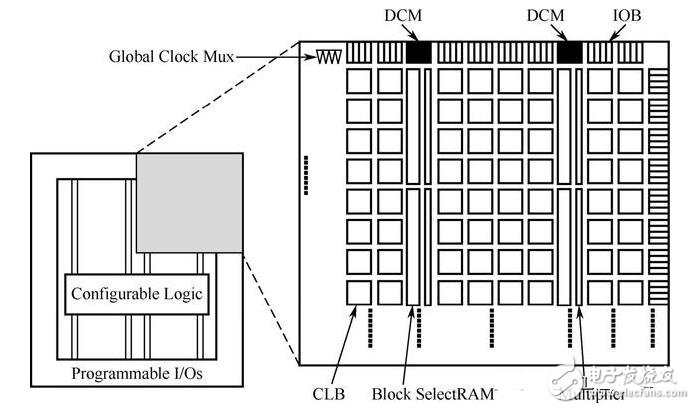

此處,我們以XC2V3000為例,介紹典型的FPGA結構圖。XC2V3000擁有300萬門的超大系統容量,采用0.15μm/0.12μmCMOS8層金屬混合工藝設計,內核電壓為1.5V,根據輸入/輸出參考電壓的不同設計可支持多種接口標準,內部時鐘頻率可達420MHz。XC2V3000的內部結構如圖1-1所示,它主要由可配置邏輯(CLB)、用戶可編程I/O(IOB)、BlockSelectRAM、數字時鐘管理模塊(DCM)、數字阻抗匹配模塊(DCI)和硬件乘法器等組成。其中CLB用于實現FPGA的絕大部分邏輯功能;IOB用于提供封裝引腳與內部邏輯之間的接口;BlockRAM用于實現FPGA內部的隨機存取,它可配置RAM、雙口RAM、FIFO等隨機存儲器;DCM用于提供靈活的時鐘管理功能;硬件乘法器用于提高FPGA的數字信號處理能力。

1、可配置邏輯塊(CLB)

如圖1-2所示,XC2V3000的CLB模塊由4個相同的Slice和附加邏輯構成,用于實現組合邏輯和時序邏輯。

每個Slice由2個4輸入函數發生器、進位邏輯、算術邏輯、存儲邏輯和函數復用器組成。算術邏輯包括1個異或門(XORG)與1個專用與門(MULTAND),1個異或門可以使1個Slice實現2位全加操作,專用與門用于提高乘法器的效率。進位邏輯由專用進位信號和函數復用器(MUXC)組成,共同實現快速的算術加減法操作。具體結構詳見圖1-3和圖1-4。

2、可編程輸入/輸出單元(IOB)

可編程輸入/輸出單元簡稱IOB,提供FPGA內部邏輯與外部封裝引腳之間的接口,用于完成不同電氣特性下對輸入/輸出信號的驅動和匹配。根據當前使用的I/O接口標準的不同,需要設置不同的接口電壓Vcco和參考電壓VREF。XC2V3000的I/O引腳分布在8個Bank中,同一個Bank的接口電壓Vcco必須保持一致,不同Bank的接口電壓Vcco允許不同。

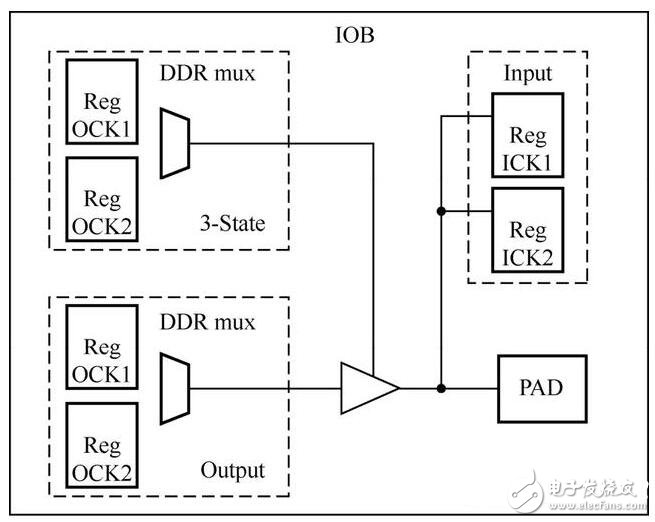

如圖1-5所示,XC2V3000的IOB模塊含有6個存儲單元,可以單獨配置為邊沿D觸發器或鎖存器,也可以成對實現DDR(Double-Data-Rate)輸入和DDR輸出。

DDR寄存器的結構見圖1-6。

3、嵌入式塊RAM(BRAM)

XC2V3000的BlockSelectRAM資源豐富,其單位容量為18Kb雙端口RAM,可以自由設定數據寬度和深度縱橫比,并支持三種并發讀/寫(Read-During-Write)模式。

4、豐富的布線資源

布線資源連通FPGA內部所有的單元,IOB、CLB、BRAM、DCM等都使用相同的內連陣列。XC2V3000內部共有16條全局時鐘線,用于芯片內部全局時鐘和全局復位/置位的布線。24條縱橫交錯的長線資源實現了芯片Bank間的高速通信和第二全局時鐘信號的布線。

5、底層內嵌功能單元

XC2V3000集成了豐富的內嵌功能模塊,如DCM(數字時鐘管理器)、DCI(數字控制阻抗)、MicroBlaze軟處理器核等,使其具有軟、硬件聯合設計的能力,可以用有限的資源完成系統級的設計任務。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636346 -

可編程

+關注

關注

2文章

1325瀏覽量

41489

發布評論請先 登錄

FPGA典型結構圖介紹

FPGA典型結構圖介紹

評論