1. 片上多核系統(tǒng)與片上網(wǎng)絡(luò)的發(fā)展中的

1.1 片上多核系統(tǒng)發(fā)展的兩條演進(jìn)路線(xiàn)

系統(tǒng)級(jí)芯片也被稱(chēng)為片上系統(tǒng),是指在單個(gè)芯片內(nèi)部實(shí)現(xiàn)大部分甚至完整的電子系統(tǒng)功能的一種芯片。這種芯片是高端電子系統(tǒng)的核心,隨著集成電路工藝技術(shù)的發(fā)展也逐步向中低端電子系統(tǒng)發(fā)展。如今,很多諸如腕表、手環(huán)之類(lèi)的可穿戴設(shè)備以及智能玩具等低端嵌入式設(shè)備也都以系統(tǒng)級(jí)芯片為核心來(lái)開(kāi)展設(shè)計(jì)。可以說(shuō)片上系統(tǒng)已經(jīng)成為集成電路,尤其是數(shù)字集成電路的主要實(shí)現(xiàn)形式。

由于集成電路工藝在摩爾定律的驅(qū)使下飛速發(fā)展,單位面積上的晶體管數(shù)量不斷增加。根據(jù)登納德縮放比例(晶體管面積的縮小使得其所消耗的電壓以及電流會(huì)以差不多相同的比例縮小。也就是說(shuō),如果晶體管的大小減半而時(shí)鐘頻率不變,該晶體管的功耗將會(huì)降至四分之一)。,使用新的集成電路工藝可以讓設(shè)計(jì)者可以大大地提高芯片的時(shí)鐘頻率,因?yàn)樘岣哳l率所帶來(lái)的更多的功耗會(huì)與晶體管縮放減少的功耗抵消,芯片的性能可以依靠不斷的提升時(shí)鐘頻率來(lái)獲得提高(當(dāng)然,也要配合架構(gòu)設(shè)計(jì)的改進(jìn),例如利用增加的晶體管設(shè)計(jì)更多而且更為合理的高速緩存)。這樣在芯片內(nèi)部集成更多的晶體管的時(shí)候,提高芯片時(shí)鐘頻率成為了一個(gè)“免費(fèi)的午餐”。

而2005年前后,晶體管微縮到一定程度以后量子隧穿效應(yīng)(指像電子等微觀粒子能夠穿入或穿越位勢(shì)壘的量子行為)開(kāi)始慢慢介入,使得晶體管漏電現(xiàn)象開(kāi)始嚴(yán)重。漏電現(xiàn)象的出現(xiàn)打破了原先登納德所提出的定律。單純提高時(shí)鐘頻率將造成芯片功耗難以控制。功耗增大除了更費(fèi)電不環(huán)保之外,帶來(lái)的最大問(wèn)題是增加的功耗會(huì)轉(zhuǎn)化為熱量。在微小的芯片面積上大量功耗密集堆積會(huì)導(dǎo)致溫度急劇增加。如果散熱做的不好,芯片的壽命將大大減少甚至變得不穩(wěn)定。在這種情況下,提高芯片的時(shí)鐘頻率不再是免費(fèi)的午餐。在沒(méi)有解決晶體管漏電的問(wèn)題之前,單純的增加芯片的時(shí)鐘頻率因?yàn)殡S之而來(lái)的散熱問(wèn)題而變得不再現(xiàn)實(shí)。于是芯片研究商們開(kāi)始紛紛停止高頻芯片的研發(fā),轉(zhuǎn)而向低頻多核的架構(gòu)開(kāi)始研究,用更多但頻率更低的核心來(lái)替代一個(gè)高頻率的核心。這種具備多個(gè)運(yùn)算核心的片上系統(tǒng)就是片上多核系統(tǒng)。

近10年來(lái)片上多核系統(tǒng)一直是數(shù)字集成電路領(lǐng)域的熱點(diǎn),經(jīng)過(guò)眾多研究者的不斷努力誕生了大量很有意義的研究成果。片上網(wǎng)絡(luò),本質(zhì)上是為了解決片上多核系統(tǒng)中不同的核心之間,核心與非核心(Un-Core)硬件單元之間數(shù)據(jù)傳輸問(wèn)題的一種“片上通信”方案。因此要理解清楚片上系統(tǒng)的發(fā)展脈絡(luò),必須要先從片上多核系統(tǒng)的發(fā)展入手。否則就會(huì)出現(xiàn)“無(wú)的放矢”和“盲人摸象”的問(wèn)題。但由于片上多核系統(tǒng)的研究者背景和應(yīng)用領(lǐng)域不同導(dǎo)致發(fā)展演進(jìn)過(guò)程較為復(fù)雜而難以理解。2012年本人及所在研究小組開(kāi)始切入片上網(wǎng)絡(luò)相關(guān)時(shí),由于對(duì)于片上多核系統(tǒng)的理解不深,導(dǎo)致研究出現(xiàn)了諸多波折與困擾,導(dǎo)致在一年多的時(shí)間中整體研究徘徊不前。

為減少這一問(wèn)題對(duì)于大家理解片上網(wǎng)絡(luò)的影響,作為我們系列文章的開(kāi)頭,本文將首先總結(jié)片上多核系統(tǒng)的演進(jìn)歷史與現(xiàn)狀。從而讓大家理解出現(xiàn)片上網(wǎng)絡(luò)這一技術(shù)背后的推動(dòng)力,也可以看出片上網(wǎng)絡(luò)多年來(lái)一直徘徊不前的原因。

下面就開(kāi)始進(jìn)入我們的正題:

第一款被大眾所熟知的商用化片上多核系統(tǒng)是著名處理器芯片提供商之一的AMD公司面向個(gè)人電腦推出的ATHLON X2雙核中央處理器Central Processing Unit (CPU),該款CPU在商業(yè)上大獲成功。此后商用化片上多核系統(tǒng)的研制開(kāi)始進(jìn)入高潮。2005 年Intel發(fā)布了64位雙核處理器Montecito[1],而IBM公司則發(fā)布了具有9個(gè)核心的Cell處理器[2]。此后的10年間,片上多核系統(tǒng)開(kāi)始大量的被應(yīng)用于各種信息基礎(chǔ)設(shè)備,成為高性能電子設(shè)備的核心器件。

但實(shí)際上片上多核系統(tǒng)的研究開(kāi)始于上個(gè)世紀(jì)90年代中期,在過(guò)去的20多年中片上多核系統(tǒng)架構(gòu)一直處于不斷發(fā)展和演進(jìn)中。由于應(yīng)用領(lǐng)域和研究人員的學(xué)術(shù)背景不同,片上多核系統(tǒng)的研究從一開(kāi)始就有著明顯的“流派”之分。隨著研究的持續(xù)深入,片上多核系統(tǒng)出現(xiàn)了越來(lái)越多的技術(shù)分支。這不但讓廣大吃瓜群眾難以辨識(shí),對(duì)于很多剛接觸片上多核系統(tǒng)研究的碩士生和低年級(jí)博士生而言,搞清楚這些技術(shù)分支的區(qū)別與聯(lián)系也并不是一件輕松的工作。

簡(jiǎn)單來(lái)說(shuō),片上多核系統(tǒng)由于起源不同、應(yīng)用領(lǐng)域不同以及研究者的學(xué)術(shù)背景不同等原因,發(fā)展出了不同的技術(shù)路線(xiàn)。上文提到的Intel公司發(fā)布的Montecito處理器[1]和IBM公司發(fā)布的Cell處理器[2]就代表了兩種最主要的技術(shù)路線(xiàn)。

Montecito處理器這一類(lèi)片上多核系統(tǒng)源于Symmetric Multi-Processing System (SMP)系統(tǒng),被稱(chēng)之為Chip Multiprocessors (CMP)(國(guó)內(nèi)一般翻譯為單芯片多處理器),主要用于高性能通用計(jì)算領(lǐng)域。Cell處理器這一類(lèi)片上多核系統(tǒng)則由片上系統(tǒng)Systemon-Chip (SoC)演進(jìn)而來(lái),被稱(chēng)為Multi-Processors System-on-Chip (MPSoC)。這類(lèi)片上多核系統(tǒng)主要作為一種高端的嵌入式處理器被應(yīng)用于通信、信號(hào)處理、多媒體處理等領(lǐng)域。為方便行文,后文中直接使用CMP和MPSoC來(lái)指代這兩類(lèi)處理器。

采用CMP架構(gòu)的片上多核系統(tǒng)通常被應(yīng)用于工作站、服務(wù)器、云計(jì)算平臺(tái)等通用計(jì)算設(shè)備,所運(yùn)行的主要應(yīng)用通常是以科學(xué)計(jì)算、仿真模擬為代表的大數(shù)據(jù)量通用計(jì)算。這類(lèi)片上多核系統(tǒng)大多采用數(shù)據(jù)并行的并行程序開(kāi)發(fā)模式,以共享存儲(chǔ)器的方式來(lái)交換數(shù)據(jù)。這樣的好處在于開(kāi)發(fā)難度較低、程序的通用性較好,可以借用類(lèi)似于OpenMP[3]這樣已經(jīng)較為成熟的并行編程模型加以開(kāi)發(fā)。又由于科學(xué)計(jì)算、仿真模擬這類(lèi)應(yīng)用的特點(diǎn)通常是數(shù)據(jù)量超大,但不同處理器上所運(yùn)行的核心程序往往是相同的。因此采用共享存儲(chǔ)的方式可以使得多個(gè)處理器核心可以很容易共享同一塊虛擬地址空間,這使得同一程序可以很方便的同時(shí)運(yùn)行在不同的核心上,也可以很方便的共享同一個(gè)操作系統(tǒng)或管理程序。

Hydra處理器是1996年美國(guó)斯坦福大學(xué)研制集成了4個(gè)核心的處理器[4],它被認(rèn)為是首款具備CMP性質(zhì)的片上多核系統(tǒng)。

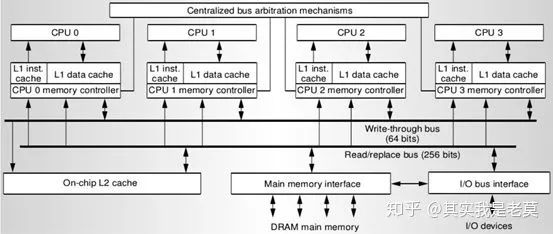

圖1 Hydra處理器架構(gòu)圖,它被認(rèn)為是首款具備CMP性質(zhì)的片上多核系統(tǒng)

Hydra處理器采用了四個(gè)MIPS 處理核心,每個(gè)核心擁有私有的指令緩存(I-Cache)和數(shù)據(jù)緩存(D-Cache)。二級(jí)緩存為四個(gè)核心共享,通過(guò)核心自身的存儲(chǔ)控制器(Memory Controller, MC)及一組總線(xiàn)與二級(jí)緩存(L2 Cache)、主存儲(chǔ)器接口(Main Memory Interface)和輸入輸出總線(xiàn)接口(I/O Bus Interface)互連。由于片上的二級(jí)緩存為四個(gè)核心所共享,因此四個(gè)核心實(shí)質(zhì)上在邏輯上具備單一的內(nèi)存地址空間。這也使得共享同一個(gè)操作系統(tǒng)或管理程序成為可能。Hydra處理器為后續(xù)CMP架構(gòu)片上多核系統(tǒng)的發(fā)展奠定了基礎(chǔ),這一架構(gòu)的片上多核系統(tǒng)在后續(xù)的演進(jìn)過(guò)程中始終被Hydra處理器的初始設(shè)計(jì)所影響。

而MPSoC誕生初期的主要代表是一些集成了多個(gè)數(shù)字信號(hào)處理器(Digital Signal Processor DSP)和微處理器(Microprocessor Unit MPU)的專(zhuān)用芯片。這些芯片主要被應(yīng)用于數(shù)字電視、多媒體播放器等信號(hào)處理設(shè)備。與追求高性能的通用計(jì)算不同,MPSoC 主要應(yīng)用領(lǐng)域所面臨的主要問(wèn)題是計(jì)算的實(shí)時(shí)性。由于計(jì)算任務(wù)的確定性更強(qiáng),使得MPSoC的設(shè)計(jì)者和使用者能夠也必須要精確的劃分任務(wù)并合理的分配任務(wù)以應(yīng)對(duì)各種挑戰(zhàn)。

圖2所示的Viper處理器[5],即為最早的一批MPSoC之一。

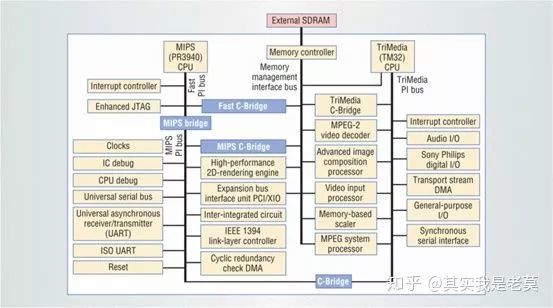

圖2 Viper處理器架構(gòu)示意圖,它是早期MPSoC的代表之一

從圖2中可以看出,整個(gè)芯片可以被劃分為兩個(gè)相對(duì)獨(dú)立的子系統(tǒng)。分別以MIPS(PR3940)CPU和TriMedia(TM32)CPU為核心。圖左側(cè)為以MIPS(PR3940)CPU為核心的子系統(tǒng),這部分子系統(tǒng)的架構(gòu)類(lèi)似于一個(gè)通用的嵌入式SoC芯片,集成了如UART、IEEE 1394協(xié)議控制器之類(lèi)的接口模塊。圖右側(cè)為以TriMedia(TM32)CPU為核心,在這一子系統(tǒng)中集成了如MPEG-2視頻解碼器、視頻輸入處理器等多媒體處理單元,實(shí)質(zhì)上構(gòu)成了一個(gè)專(zhuān)用的多媒體處理器。因此可以很清楚的判斷Viper處理器中以MIPS(PR3940)CPU為核心的子系統(tǒng)主要負(fù)責(zé)通用處理器控制和數(shù)據(jù)傳輸方面的功能,而以MIPS(PR3940)CPU為核心的子系統(tǒng)則主要負(fù)責(zé)多媒體信號(hào)處理。兩個(gè)子系統(tǒng)相對(duì)獨(dú)立,通過(guò)Fast C-Bridge、MIPS C-Bridge以及C-Bridge三個(gè)總線(xiàn)橋相互連接。

Viper處理器的架構(gòu)很清晰的體現(xiàn)了MPSoC的一些典型特點(diǎn):按任務(wù)需求劃分為若干獨(dú)立的子系統(tǒng),每個(gè)子系統(tǒng)完成一個(gè)專(zhuān)門(mén)的功能,子系統(tǒng)之間相對(duì)獨(dú)立等。這種架構(gòu)設(shè)計(jì)方法充分體現(xiàn)了嵌入式系統(tǒng)的特性,因而被后來(lái)的研究者所繼承和發(fā)揚(yáng)。

RAW[6]是一代具有劃時(shí)代意義的片上多核系統(tǒng)。雖然它被發(fā)表于1997年,但它卻奠定了今后20年采用片上網(wǎng)絡(luò)互聯(lián)的CMP的基本架構(gòu)。

圖3 首次采用Tile結(jié)構(gòu)和網(wǎng)絡(luò)化互聯(lián)的CMP架構(gòu)芯片:RAW

RAW是由美國(guó)麻省理工學(xué)院于1997年提出并流片驗(yàn)證(從這里也可以看出美國(guó)在于高端系統(tǒng)芯片領(lǐng)域的積累深厚,回想我們1997年的芯片設(shè)計(jì)水平也才剛剛進(jìn)入到能把EDA工具流程用起來(lái),開(kāi)始做ASIC的水平。龍芯等一大批處理器芯片設(shè)計(jì)都要等到2000以后)。

RAW微處理器架構(gòu)采用了一種被稱(chēng)為T(mén)ile(國(guó)內(nèi)有國(guó)內(nèi)文獻(xiàn)有直譯為瓦片,為避免歧義本文中均使用英文原文指代)的模塊劃分方式。這種劃分方法把CPU、私有Cache(L1 Cache)、共享Cache(L2 Cache)的一個(gè)Bank(一直不知道這個(gè)該怎么翻譯……)、網(wǎng)絡(luò)接口(Network Interface NI)等硬件資源構(gòu)建為一個(gè)獨(dú)立的Tile。在不同的Tile在芯片規(guī)劃的平面內(nèi)按一定的規(guī)律整齊排列,Tile和Tile之間通過(guò)NoC加以互聯(lián)。這種采用Tile來(lái)劃分和組織片上多核系統(tǒng)的方式優(yōu)勢(shì)在于每個(gè)核心比較規(guī)整,有利于芯片后端設(shè)計(jì)并具備較好的可擴(kuò)展性。此后雖然有一些其它形式的核心劃分與組織方式的論文發(fā)表,但基于Tile的劃分與組織方式始終被絕對(duì)部分研究者(灌水者)所繼承。

接下來(lái)看一看比較近的一點(diǎn)的CMP架構(gòu)的片上多核系統(tǒng),32核心SPARC M7處理器[7]。發(fā)布于2015年的ISSCC上。

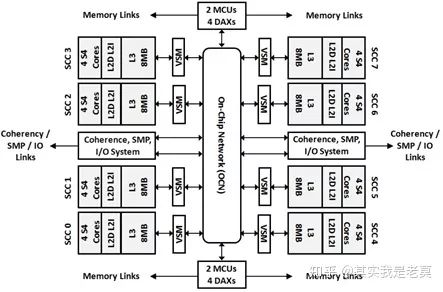

圖4 32核心SPARC M7處理器邏輯結(jié)構(gòu)圖

該款處理器共有32個(gè)核心,每4個(gè)核心構(gòu)成一個(gè)組(文章中稱(chēng)其為SCC),總共8個(gè)組。每個(gè)組內(nèi)部共享L2 Cache,但其它組不能訪問(wèn)。L3 Cache為全局共享Cache,可以被所有的所有核心訪問(wèn)。L3 Cache同樣被劃分為8個(gè)獨(dú)立的bank,和對(duì)應(yīng)的每個(gè)組一起組成了一個(gè)完整的Tile。

為了更有效的互聯(lián)各個(gè)不同的Tile,研究者為SPARC M7處理器設(shè)計(jì)了三套不同的片上網(wǎng)絡(luò)。分別是采用環(huán)網(wǎng)(Ring)結(jié)構(gòu)的請(qǐng)求網(wǎng)絡(luò)(Request Network),采用廣播(Broadcasting)結(jié)構(gòu)的響應(yīng)網(wǎng)絡(luò)(Responses Network)以及采用網(wǎng)格(Mesh)結(jié)構(gòu)的數(shù)據(jù)網(wǎng)絡(luò)(Data Network)。不同的片上網(wǎng)絡(luò)分別傳送不同的控制信息和數(shù)據(jù),從而使得訪問(wèn)Cache的效率能最大限度的提高。

片上網(wǎng)絡(luò)成為CMP架構(gòu)的片上多核系統(tǒng)內(nèi)部互聯(lián)的主流方式之后,片上緩存的組織方式也相應(yīng)的發(fā)生了改變。在使用總線(xiàn)或交換結(jié)構(gòu)的時(shí)代,CPU訪問(wèn)不同Cache Bank的時(shí)間是基本保持一致的。但在使用片上網(wǎng)絡(luò)作為內(nèi)部互聯(lián)以后,CPU訪問(wèn)不同的Cache Bank的時(shí)間已經(jīng)不可能保持一致了。因此一種被稱(chēng)為非均勻高速緩存體系結(jié)構(gòu)(Non-uniform Cache Architecture, NUCA)的概念被提出。NUCA是基于片上網(wǎng)絡(luò)的CMP片上多核系統(tǒng)所必然要面臨的問(wèn)題,但對(duì)NUMA的研究也推動(dòng)了基于片上網(wǎng)絡(luò)的CMP片上多核系統(tǒng)向前持續(xù)演進(jìn)。改進(jìn)NUMA條件下CMP架構(gòu)片上多核系統(tǒng)的訪存效率,也成為提升CMP架構(gòu)片上多核系統(tǒng)性能的主要途徑。由于這部分內(nèi)容涉及到較多存儲(chǔ)體系結(jié)構(gòu)方面的研究,在計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)的研究中屬于另外一個(gè)領(lǐng)域。超出了本文甚至本系列文章所討論的范圍,因而在此不再進(jìn)一步展開(kāi)討論。

當(dāng)然,也不是所有的CMP架構(gòu)的片上多核系統(tǒng)從此就走上了依靠NoC互聯(lián)的道路。當(dāng)核心數(shù)量不多的時(shí)候確實(shí)沒(méi)有必要考慮使用NoC。例如AMD的Zen就是沒(méi)有依靠NoC而采用了一種叫Core Complex (CCX)的方式互聯(lián)[8]。

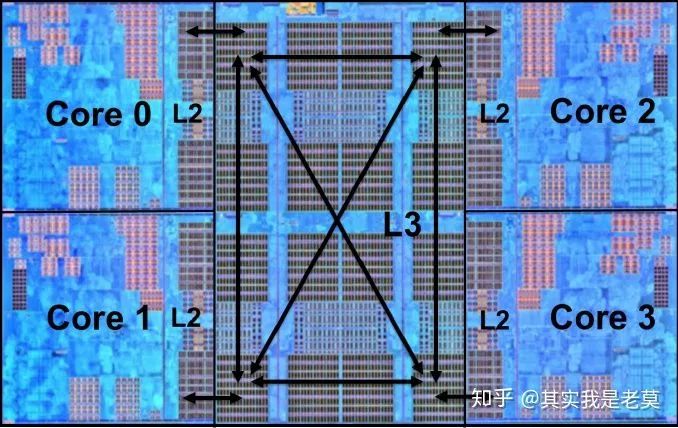

圖5 采用CCX互聯(lián)的Zen,依然具備CMP架構(gòu)的基本特征

從圖5可以看出,Zen雖然核心比較少,但仍然是典型的CMP架構(gòu)。

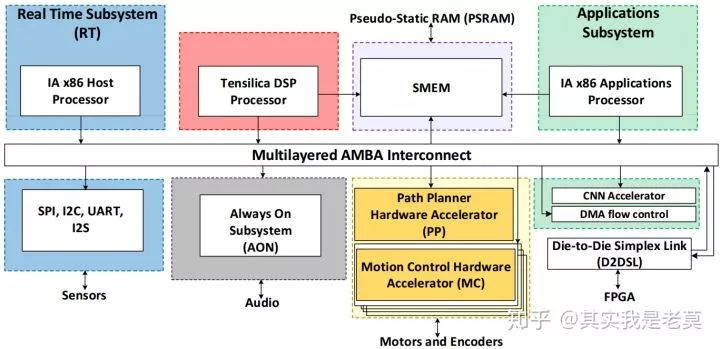

談了很久的CMP,我們回頭再來(lái)看一看MPSoC。相比于CMP的規(guī)整、對(duì)稱(chēng)的架構(gòu),MPSoC是由若干個(gè)獨(dú)立的子系統(tǒng)構(gòu)成的。圖6是Intel在今年ISSCC上發(fā)布的面向機(jī)器人的Robot SoC[9]。

圖6 面向機(jī)器人的Robot SoC,典型的MPSoC架構(gòu)

圖6中有若干個(gè)子系統(tǒng)。左邊第一個(gè)是以X86處理器為核心的實(shí)時(shí)子系統(tǒng),主要負(fù)責(zé)對(duì)外接口通信與控制,所以和SPI、I2C等外設(shè)接口劃分到一起了。Tensilica DSP則是負(fù)責(zé)信號(hào)處理運(yùn)算的一個(gè)子系統(tǒng)。有一個(gè)Always on子系統(tǒng)是常開(kāi)的,主要負(fù)責(zé)音頻方面的處理,應(yīng)該是用于芯片的喚醒。還有路徑規(guī)劃硬件加速器、運(yùn)動(dòng)控制硬件加速器等一系列加速器以及由X86處理器配合CNN加速的應(yīng)用子系統(tǒng),用于實(shí)現(xiàn)人工智能算法。

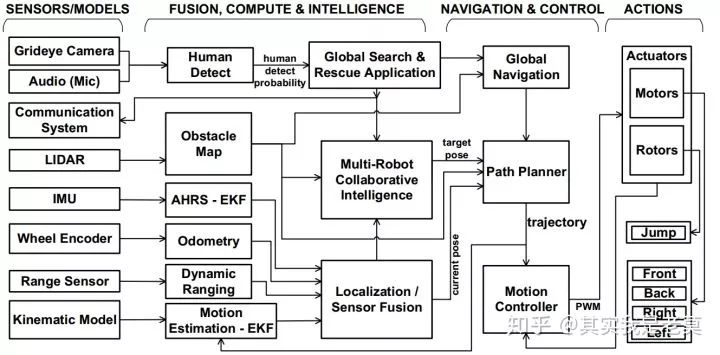

圖7是Robot SoC[9]所實(shí)現(xiàn)的算法,可以看出是由多個(gè)獨(dú)立任務(wù)構(gòu)成的。這種形式的應(yīng)用比較容易被劃分為若干個(gè)獨(dú)立子系統(tǒng)來(lái)實(shí)現(xiàn)。這也是MPSoC主要應(yīng)用領(lǐng)域里的各種算法 的基本特征。

圖7 Robot SoC所需要實(shí)現(xiàn)的算法

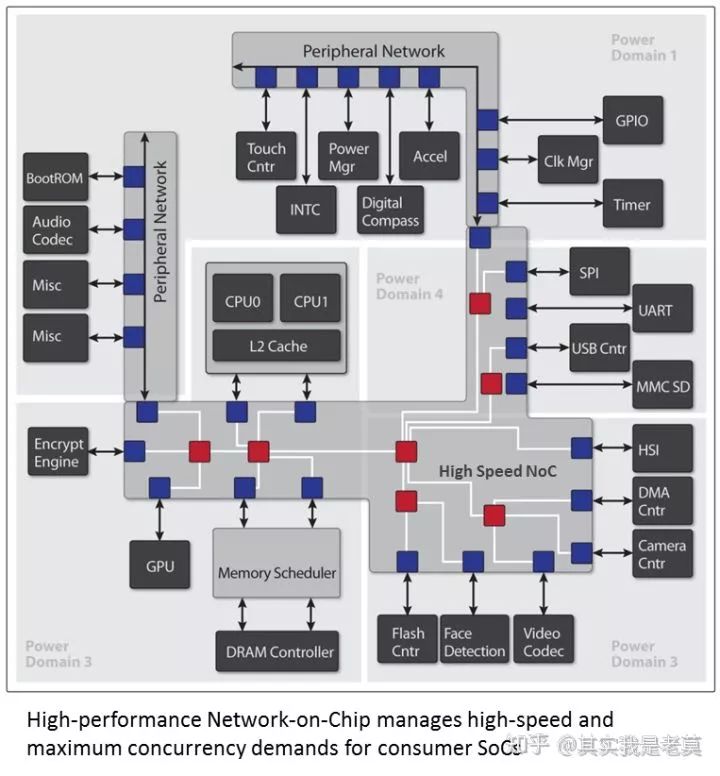

如果芯片內(nèi)部的子系統(tǒng)較多,關(guān)系復(fù)雜,當(dāng)然也可以依靠NoC來(lái)互聯(lián)。比如剛剛被收購(gòu)的sonics公司就給了這么一個(gè)例子[10]。

圖8 Sonics公司給出的高性能片上網(wǎng)絡(luò)在SoC中的應(yīng)用

可以看出,在MPSoC中有多個(gè)獨(dú)立的子系統(tǒng)時(shí),使用片上網(wǎng)絡(luò)是一種必要的片上通信方式。

最后,我們稍作總結(jié):

1.片上多核系統(tǒng)是現(xiàn)在系統(tǒng)級(jí)集成電路的主要實(shí)現(xiàn)形式;

2.片上多核系統(tǒng)分為CMP和MPSoC兩種架構(gòu);

3.CMP主要用于通用計(jì)算,大多采用數(shù)據(jù)并行的并行程序開(kāi)發(fā)模式,以共享存儲(chǔ)器的方式來(lái)交換數(shù)據(jù),通常以對(duì)稱(chēng)的Tile形式來(lái)組織芯片硬件結(jié)構(gòu);

4.MPSoC主要用于嵌入式設(shè)備,大多是由多個(gè)相對(duì)獨(dú)立的子系統(tǒng)構(gòu)成,一般“按需設(shè)計(jì)”,結(jié)構(gòu)極不對(duì)稱(chēng)。

本次先談到這里,下回來(lái)談一下不同片上多核系統(tǒng)的互聯(lián)需求。也講一下片上多核系統(tǒng)的發(fā)展如何引導(dǎo)片上網(wǎng)絡(luò)的發(fā)展的。

參考文獻(xiàn):

[1] C. Mcnairy, R. Bhatia. Montecito: A Dual-Core, Dual-Thread Itanium Processor[J]. IEEE Micro, 2005, 25(2):10–20

[2] J. Kahle. The cell processor architecture[C]. 38th annual IEEE/ACM International Symposium on Microarchitecture, Washington, DC, 2005, 49–56

[3] Dagum L, Menon R. OpenMP: an industry standard API for shared-memory programming[J]. IEEE computational science and engineering, 1998, 5(1): 46-55.

[4]K. Olukotun, B. A. Nayfeh, L. Hammond, et al. The case for a single-chip multiprocessor[C]. Seventh international conference on Architectural support for programming languages and operating systems, New York, 1996, 2–11

[5]S. Dutta, R. Jensen, A. Rieckmann. Viper: A multiprocessor SOC for advanced set-top box and digital TV systems[J]. IEEE Design Test of Computers, 2001, 18(5):21–31

[6]J. Babb, M. Frank, V. Lee, et al. The RAW benchmark suite: computation structures for general purpose computing[C]. The 5th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, Vancouver, 1997, 134 – 143

[7] Oracle, Redwood Shores, CA:A 20nm 32-Core 64MB L3 Cache SPARC M7 Processor 2015 IEEE International Solid-State Circuits Conference

[8] Singh, Teja, et al. "3.2 Zen: A next-generation high-performance× 86 core." 2017 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2017.

[9] Honkote, Vinayak, et al. "2.4 A Distributed Autonomous and Collaborative Multi-Robot System Featuring a Low-Power Robot SoC in 22nm CMOS for Integrated Battery-Powered Minibots." 2019 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2019.

[10]NoC | The Traffic Cop

-

集成電路

+關(guān)注

關(guān)注

5452文章

12572瀏覽量

374541 -

多核系統(tǒng)

+關(guān)注

關(guān)注

0文章

11瀏覽量

7639 -

處理器芯片

+關(guān)注

關(guān)注

0文章

123瀏覽量

20352

原文標(biāo)題:【博文連載】詳說(shuō)片上網(wǎng)絡(luò)之一:片上多核系統(tǒng)與片上網(wǎng)絡(luò)的發(fā)展

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Zynq全可編程片上系統(tǒng)詳解

CC2530:2.4GHz IEEE 802.15.4和ZigBee應(yīng)用的片上系統(tǒng)解決方案

CC2544:2.4GHz USB應(yīng)用的片上系統(tǒng)解決方案

深入解析CC2545:2.4GHz RF應(yīng)用的理想片上系統(tǒng)解決方案

TDK IBQ系列磁性片:RFID應(yīng)用的理想之選

瑞蘇盈科亮相第四屆歐洲核子研究組織(CERN)片上系統(tǒng)研討會(huì)

PI加熱片知識(shí)FAQ

新思科技UCIe IP解決方案實(shí)現(xiàn)片上網(wǎng)絡(luò)互連

上海光機(jī)所在片上穩(wěn)頻激光器研究方面取得重要進(jìn)展

人工合成石墨片與天然石墨片的差別

分享兩種前沿片上互連技術(shù)

片上多核系統(tǒng)與片上網(wǎng)絡(luò)的發(fā)展

片上多核系統(tǒng)與片上網(wǎng)絡(luò)的發(fā)展

評(píng)論