CPU的生產是需要經過硅提純、切割晶圓、影印、蝕刻、分層、封裝、測試7個工序,這個過程中要進行加工各種電路和電子元件,制造導線連接各個元器件。其工藝的先進與否關系到CPU內能塞進多少個晶體管,還有CPU所能達到的頻率還有它的功耗。1978年Intel推出了第一顆CPU--8086,它采用3μm(3000nm)工藝生產,只有29000個晶體管,工作頻率也只有5MHz,而現在晶體管數量最多的單芯片CPU應該是Intel的28核Skylake-SP Xeon處理器,它擁有超過80億個晶體管,而頻率最高的則是Core i9-9900K,最大睿頻能到5GHz,它們都是用Intel的14nm工藝生產的。

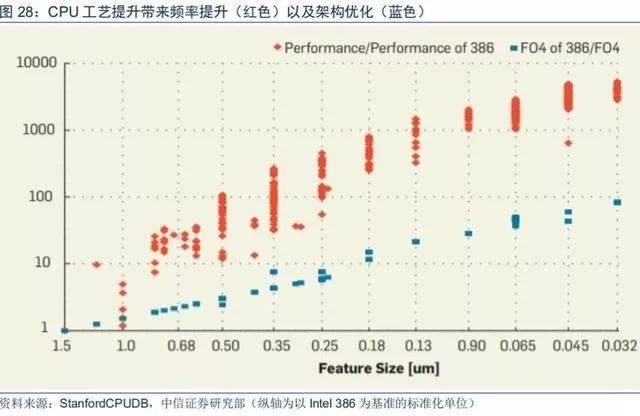

先進的制程工藝提升對于 CPU 性能提升影響明顯。工藝提升帶來的作用有頻率提升以及架構優化兩個方面。一方面,工藝的提升與頻率緊密相連,使得芯片主頻得以提升;另一方面工藝提升帶來晶體管規模的提升,從而支持更加復雜的微架構或核心,帶來架構的提升。根據 CPUDB 的數據,可以看出在芯片發展歷史上,工藝提升顯著帶來了頻率提升和架構提升的作用。隨著制程節點進步,可以發現頻率隨工藝增長的斜率已經減緩,由于登德爾縮放定律的失效以及隨之而來的散熱問題,單純持續提高 CPU 時鐘頻率變得不再現實,廠商也逐漸轉而向低頻多核架構的研究。

AMD 先前代工廠商 GlobalFoundries14nmLPP 技術授權自三星,工藝水平低于 Intel 14nm,但同價位產品多線程性能更高。以 AMD 目前最新的 Ryzen 系列處理器為例,Ryzen系列于 2017 年 3 月上市,采用 ZEN 架構,制作工藝采用 GlobalFoundries 14nmLPP,事實上 GlobalFoundries 14nmFinFET 技術于 2014 年購買自三星,在柵極間距(Gatelength)/CPP(ContactedPolyPitch)、鰭片間距(FinPitch)、第一層金屬間距(MetalPitch)等參數上 AMD 14nm 處理器均弱于 Intel 14nm 處理器。根據 Anandtech 性能測試結果,AMDRyzen 系列 CPU 在單線程性能方面弱于同價位 IntelCPU,但由于采用了堆積更多核心的設計,實際多線程性能強于同價位 IntelCPU,因而 AMD RyzenCPU 實際擁有更高性價比。

目前服務器市場英特爾占據約 99%市場、AMD 約 1%;桌面級市場英特爾約占 91%、AMD 約 9%。AMD 在 CPU 市場長期位于市場第二,近幾年來市場份額有顯著下降。但自2017 年 AMD 發布 Ryzen 新系列之后,新品獲得較好反響,市場份額開始好轉。2018 年AMD 服務器 CPU 市場份額已回升超過 1%,個人電腦 CPU 市場份額亦回升至 10%左右。

AMD轉投臺積電后,工藝水平趕超英特爾,有望持續擴張市場份額。近期 AMD 宣布在 7nm 節點采用臺積電工藝,其長期合作的代工廠 GlobalFoundries 放棄 7nm 研發。一方面,由此可見賽道壁壘持續提高,GlobalFoundries 7nm 技術進展已無法滿足 AMD 需求,臺積電在有限的未來先進工藝代工中難以看到對手。另一方面,CPU 已經進入 Fabless + Foundry 階段,英特爾與 AMD 之間的競爭實質上變為英特爾作為 IDM 與臺積電代工工藝的競爭。由于臺積電 2018 年 Q2 已量產 7nm 工藝,AMD 有望從 2019 年上半年逐漸出貨7nmCPU 產品,而英特爾 10nm 預計 2019 下半年量產,實際出貨恐延后至 2020 年。AMD有望工藝領先 Intel 一年左右,未來一年內在服務器端和個人電腦端 AMD 有望持續擴張市場份額,預計 AMD 與臺積電雙雙獲益。

-

amd

+關注

關注

25文章

5684瀏覽量

139968 -

cpu

+關注

關注

68文章

11279瀏覽量

224984 -

先進制程

+關注

關注

0文章

92瀏覽量

9008

原文標題:【AET原創】先進制程競爭已成為影響CPU的決定因素

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

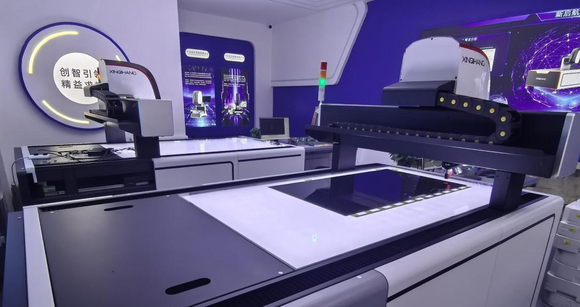

LCD液晶面板激光修復工藝助力制程良率提升

如何確保CAT.1模組的高性能與低功耗?

晶圓工藝制程清洗方法

濕法清洗和干法清洗,哪種工藝更適合先進制程的硅片

國產高性能ONFI IP解決方案全解析

n型TOPCon電池中通過氘化/氫化混合策略提升鈍化性能

那么龍芯CPU性能如何呢?

一個提升蜂鳥E203性能的方法:乘除法器優化

目前最先進的半導體工藝水平介紹

樹莓派5超頻指南:安全高效地提升性能!

Arm KleidiAI與XNNPack集成實現AI性能提升

基于納米流體強化的切割液性能提升與晶圓 TTV 均勻性控制

淺切多道切割工藝對晶圓 TTV 厚度均勻性的提升機制與參數優化

先進的制程工藝提升對于CPU性能提升影響明顯

先進的制程工藝提升對于CPU性能提升影響明顯

評論