這個夏天,一個很奇妙的機會,突然觸碰到一個全新的東西,那就是Chisel。首先感謝 _iChthyosaur的博客 https://blog.csdn.net/qq_34291505/article/details/86744581給予的平臺讓我第一次接觸到這個新鮮的東西,我決定繼續開始自己的學習之旅,這個系列的博客也不會是簡單的轉述,還是有自己的思考,初次接觸一定還是會有很多理解上的問題,希望大家共同討論共同進步。

初次接觸Chisel,自然先去了解一下這個東西是什么東西

Chisel是什么?

Chisel(讀作[?t?i:z??l]),全名ConstructingHardwarein aScalaEmbeddedLanguage,是由伯克利開發的硬件構建語言,開源。

官網:https://chisel.eecs.berkeley.edu/index.html

下面是官網上列出的一些特性:

硬件構造語言(非HLS)

嵌入在Scala編程語言中

抽象的數據類型和接口

層次化+面向對象+功能化構造

用Scala中的標記來高度參數化

多時鐘域

大量的標準庫,包括浮點單元

github開源,BSD License

什么叫硬件構建語言?是來代替Verilog/SystemVerilog的嗎?

Chisel可以簡單的理解成高度抽象的、高度參數化的Verilog生成器,利用Scala語言的語法糖,來快速高效的開發硬件設計。設計完成后,自動生成Verilog,再經由傳統的數字IC設計方法(邏輯綜合、APR)變成芯片。

我們注意幾點:

Chisel是基于Scala,也可以說Chisel是用Scala語言寫的針對硬件開發的庫。用Chisel語言做設計就是在寫Scala語言的程序。有點類似UVM是SystemVerilog語言的驗證框架庫。

Chisel的應用專注在前端設計,提高設計的效率。

生成的Verilog是低層次的,也就是類似門級的。

目前仍然通過DC或者Genus來綜合。

與HLS有明顯區別,不能直接變成工藝相關的門級電路。也許以后會增加這種功能,得看相關EDA的發展。

那Chisel相比Verilog有什么優勢?

抽象程度高、高度參數化

前端設計周期縮短

可以走敏捷開發流程

除了可以生成Verilog,還可以生成C/CPP。

都說Chisel開發快,那具體有哪些語法特性?

各種變量類型可以轉換

位寬可以自動推斷

與Verilog一樣可以方便的取位和拼接

加減法可以防溢出

可以檢查敏感信號列表,防止生成latch

可以以黑盒子的方式調用Verilog,或者以in-line的方式嵌入Verilog

靈活高效的接口定義,再也不需要AUTOARG

可以定義多套不同的實現,比如FPGA和ASIC定義不同的RAM

可以處理多時鐘域,處理異步信號的同步

而這樣介紹Chisel:

Chisel (Constructing Hardware In a Scala Embedded Language) is a hardware construction language embedded in the high-level programming language Scala. At some point we will provide a proper reference manual, in addition to more tutorial examples. In the meantime, this document along with a lot of trial and error should set you on your way to using Chisel. Chisel is really only a set of special class definitions, predefined objects, and usage conventions within Scala, so when you write Chisel you are actually writing a Scala program that constructs a hardware graph. However, for the tutorial we don't presume that you understand how to program in Scala. We will point out necessary Scala features through the Chisel examples we give, and significant hardware designs can be completed using only the material contained herein. But as you gain experience and want to make your code simpler or more reusable, you will find it important to leverage the underlying power of the Scala language. We recommend you consult one of the excellent Scala books to become more expert in Scala programming.

首先Chisel是含于高級語言Scala之中,而且 Chisel實際上只是Scala中的一組特殊類定義,預定義對象和使用約定,因此當您編寫Chisel時,您實際上正在編寫構建硬件圖的Scala程序

Through the tutorial, we format commentary on our design choices as in this paragraph. You should be able to skip the commentary sections and still fully understand how to use Chisel, but we hope you'll find them interesting.

We were motivated to develop a new hardware language by years of struggle with existing hardware description languages in our research projects and hardware design courses. Verilog and VHDL were developed as hardware simulation languages, and only later did they become a basis for hardware synthesis. Much of the semantics of these languages are not appropriate for hardware synthesis and, in fact, many constructs are simply not synthesizable. Other constructs are non-intuitive in how they map to hardware implementations, or their use can accidently lead to highly inefficient hardware structures. While it is possible to use a subset of these languages and still get acceptable results, they nonetheless present a cluttered and confusing specification model, particularly in an instructional setting.

However, our strongest motivation for developing a new hardware language is our desire to change the way that electronic system design takes place. We believe that it is important to not only teach students how to design circuits, but also to teach them how to design circuit generators ---programs that automatically generate designs from a high-level set of design parameters and constraints. Through circuit generators, we hope to leverage the hard work of design experts and raise the level of design abstraction for everyone. To express flexible and scalable circuit construction, circuit generators must employ sophisticated programming techniques to make decisions concerning how to best customize their output circuits according to high-level parameter values and constraints. While Verilog and VHDL include some primitive constructs for programmatic circuit generation, they lack the powerful facilities present in modern programming languages, such as object-oriented programming, type inference, support for functional programming, and reflection.

Instead of building a new hardware design language from scratch, we chose to embed hardware construction primitives within an existing language. We picked Scala not only because it includes the programming features we feel are important for building circuit generators, but because it was specifically developed as a base for domain-specific languages.

對于如何使用Chisel表達

While Chisel focuses on binary logic, Chisel can support analog and tri-state wires with the Analog type - see Datatypes in Chisel.

We focus on binary logic designs as they constitute the vast majority of designs in practice. Tri-state logic are poorly supported standard industry flows and require special/controlled hard macros in order to be done.

在說Chisel之前首先說Scala語言,Scala是一門基于JVM運行的語言,他與JAVA語言相互兼容,Scala也是一門面向對象的函數式語言。

而現在對于主流的硬件描述語言還是Verilog,而Verilog一直以來也是有開發效率低下的弊病。后來對于這個的問題的討論結果是對Verilog進行改良,也就出現了Verilog的后續標準——SystemVerilog,但是由于它只是用于驗證。但是當時除了改良還有一部分人主張把語言轉移到軟件語言,(C++、Java),支持C++的誕生了SystemC,而對于Chisel就是支持Java的那部分人創造出的

是由加州大學伯克利分校的研究團隊發布的一種新型硬件語言。據團隊成員之一Krste Asanovic教授介紹,早在30多年前還沒有硬件描述語言的時候,他們就已經開始構想這樣一種語言了。最開始Chisel是基于Ruby的,但是后來發現Scala更適合構建Chisel。因為Scala有諸多特性適合描述電路,比如它是靜態語言,以編譯期為主,適合轉換成Verilog/VHDL。再比如它的操作符即方法、柯里化、純粹的面向對象、強大的模式匹配、便捷的泛型編寫、特質混入、函數式編程等特性,使得用Scala開發DSL語言很方便。通過firrtl編譯器可以把Chisel文件轉換成firrtl文件,這是一種標準的中間交換格式,也就是讓各種高級語言方便地轉換到Verilog/VHDL的媒介,但它其實和verilog/VHDL屬于同一層次。在這里,Chisel選擇了妥協,沒有直接生成電路,而是借助Verilog,主要是因為沒有EDA工具支持,因此,它并不等同于HLS(High Level Synthesis)。將來也許會有EDA工具直接支持Chisel。

-

Chisel

+關注

關注

0文章

7瀏覽量

587

發布評論請先 登錄

初識馬達基本原理及組成部分

【瑞薩RA6E2地奇星開發板試用】初識開發板+環境配置

LuatOS下GNSS定位開發實戰:初識定位、NMEA解碼與位置追蹤上報

RISC-V工具鏈搭建

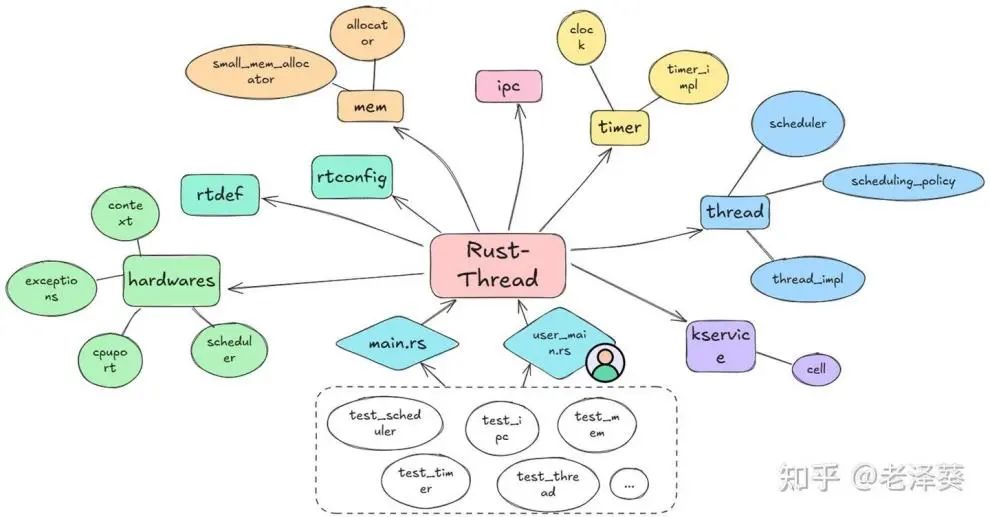

RT-Thread 遇上 Rust:安全內核 RusT-Thread 的誕生

【Milk-V Duo S 開發板免費體驗】Milk-V Duo S 開發板試用報告(1)開箱

零死角玩轉STM32——初級篇

【米爾-全志T536開發板試用體驗】 試用測評報-初識T536

chisel(一)初識

chisel(一)初識

評論