互連設(shè)計技術(shù)包括測試、仿真以及各種相關(guān)標準,其中測試是驗證各種仿真分析結(jié)果的方法和手段。優(yōu)秀的測試方法和手段是保證互連設(shè)計分析的必要條件,對于傳統(tǒng)的信號波形測試,主要應(yīng)當關(guān)注的是探頭引線的長度,避免Pigtail引入不必要的噪聲。本文主要討論互連測試技術(shù)的新應(yīng)用及其發(fā)展。

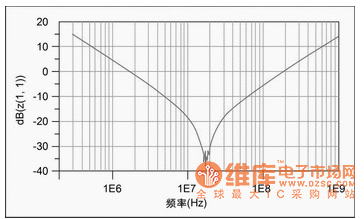

圖1:0.1uF電容阻抗曲線。

近些年,隨著信號速率的不斷提升,測試對象出現(xiàn)了顯著的變化,不再僅僅局限于傳統(tǒng)的利用示波器測試信號波形,電源地噪聲、同步開關(guān)噪聲(SSN)、抖動(Jitter)逐漸成為互連設(shè)計工程師的關(guān)注重點,一些射頻領(lǐng)域的儀器已被應(yīng)用于互連設(shè)計。互連設(shè)計中常用的測試儀器包括頻譜分析儀、網(wǎng)絡(luò)分析儀、示波器以及這些儀器所使用的各種探頭和夾具,為了適應(yīng)不斷提高的信號速率,這些測試儀器的使用方法發(fā)生了顯著的變化。本文以這些測試儀器為工具,主要從以下幾個方面介紹近年來互連設(shè)計測試技術(shù)的發(fā)展。

1. 測試的校準方法

2. 無源器件的建模方法

3. 電源完整性測試

4. 時鐘信號抖動的測試方法

在文章的最后,還將結(jié)合剛剛結(jié)束的DesignCon2005大會對未來測試技術(shù)的發(fā)展作簡要介紹。

校準方法

在三種常用的測試儀器中,網(wǎng)絡(luò)分析儀的校準方法最為嚴謹,頻譜分析儀次之,示波器的校準方法最為簡單。因此,我們這里主要討論網(wǎng)絡(luò)分析儀的校準方法。網(wǎng)絡(luò)分析儀常用的校準方法有三種,Thru、TRL和SOLT。三種方法的特性如表1所示。

表1:網(wǎng)絡(luò)分析儀常用的校準

方法有三種,Thru、TRL和SOLT

Thru的實質(zhì)是歸一化,校準時網(wǎng)絡(luò)分析儀記錄夾具的測試結(jié)果(S21_C),在實際測試中,直接將測試結(jié)果(S21_M)與S21_C相除,即得到待測件的測試結(jié)果(S21_A)。Thru校準忽略了測試夾具中的不匹配造成的反射以及空間中的電磁耦合,因此,它的校準精度最低。在僅測試S21,而且測試精度要求不高的情況下可以使用該校準方式。

在PCB等非Coaxial結(jié)構(gòu)中,有時需要對走線、過孔、連接器等的特性做測試。在這種情況下,測試儀器供應(yīng)商沒有提供標準校準件,而且測試人員也很難在測試校準端口做出良好的開路、短路、匹配負載等校準件,因此,不能做傳統(tǒng)的SOLT校準。利用TRL校準的優(yōu)點是不需要標準校準件,可以將測試校準端口延伸至所需要的位置。目前TRL校準在PCB結(jié)構(gòu)測試中的使用已經(jīng)比較廣泛。

SOLT通常被認為是標準的校準方法,校準模型中共有12個校準誤差參數(shù),通過使用短路、開路、負載和直通對各種誤差做校準計算。由于測試儀器供應(yīng)商通常僅提供Coaxial校準件,所以在非Coaxial結(jié)構(gòu),無法使用SOLT校準方法。

以上三種校準方法都可以利用信號流圖的方式做詳細的分析,其中各個誤差參數(shù)在信號流圖中均有對應(yīng)參數(shù)。通過信號流圖,可以很清楚的了解各種校準方法的誤差敏感度,從而了解實際測試的誤差范圍。這里需要提出的一點是,即使是標準的SOLT校準方法,在校準模型中也忽略了五個誤差參數(shù)。通常情況下,這五個誤差參數(shù)不會影響校準精度。但在使用時如果不注意校準夾具的設(shè)計,會出現(xiàn)無法校不準的現(xiàn)象。

頻譜分析儀內(nèi)部提供一個標準源供校準使用,校準時只需要將內(nèi)部標準源通過測試夾具與輸入端口相連即可,校準所需時間約為10分鐘。示波器的校準則更為簡單,將探頭連接至內(nèi)部標準源,確認即可,校準所需時間約為1分鐘。

無源器件的測試和建模

隨著信號速率的不斷升高,無源器件在信號鏈路中的作用越來越重要,系統(tǒng)性能仿真分析準確與否,往往決定于無源器件的模型精度。因此,無源器件的測試和建模逐漸成為各個設(shè)備供應(yīng)商的互連設(shè)計中的重要組成部分。常用的無源器件有以下幾種:

1. 連接器

2. PCB走線及過孔

3. 電容

4. 電感(磁珠)

在高速信號完整性設(shè)計中,連接器對信號鏈路的影響最大。對于經(jīng)常使用的高速連接器,通常的做法是按照TRL校準方法做校準夾具,對連接器進行測試建模,供仿真分析使用。PCB走線及過孔的測試建模方法與連接器相類似,也使用TRL校準將測試端口移至所需位置,然后測試建模。

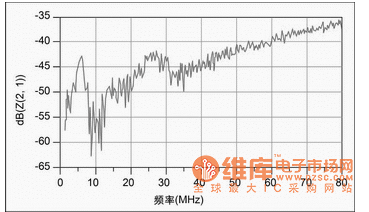

圖2:某單板電源阻抗特性

電容模型在信號完整性分析中有應(yīng)用,更主要的應(yīng)用在電源完整性分析中。業(yè)界常用的電容建模儀器是阻抗分析儀和網(wǎng)絡(luò)分析儀,分別適用于不同頻段,阻抗分析儀適用于低頻段,網(wǎng)絡(luò)分析儀適用于高頻段。如果具體實際測試中使用網(wǎng)絡(luò)分析儀做電源完整性測試,建議在電容建模的全頻段均使用網(wǎng)絡(luò)分析儀,以保證建模和應(yīng)用的一致性。由于電容的阻抗較小,在使用網(wǎng)絡(luò)分析儀建模時,通常使用并聯(lián)方式。目前業(yè)界在電容建模中沒有解決的問題是如何消除夾具與電容之間的互耦,以減小夾具對建模結(jié)果的影響。

在傳統(tǒng)的電源設(shè)計中,經(jīng)常會使用電感(磁珠)對電源做隔離,以減小噪聲干擾。而實際設(shè)計中,經(jīng)常會出現(xiàn)去除隔離電感(磁珠),電源地噪聲反而減小。這是由于電感(磁珠)與其它濾波器件產(chǎn)生諧振。為了避免這種情況的發(fā)生,有必要對電感(磁珠)建模并仿真以避免諧振。業(yè)界常用的電感(磁珠)建模方式也是采用網(wǎng)絡(luò)分析儀,具體方法與電容建模相類似,不同之處在于電感(磁珠)建模時采用串聯(lián)方式,電容建模時采用并聯(lián)方式。

上面的幾種無源器件的建模主要應(yīng)用在信號完整性和電源完整性方面,近些年EMI的仿真分析正逐步發(fā)展,關(guān)于EMI無源器件的測試建模也逐漸成為互連設(shè)計的重點。如圖1所示為電容的阻抗曲線。

電源完整性測試

隨著芯片功率不斷升高,工作電壓不斷降低,電源地噪聲逐漸成為互連設(shè)計中關(guān)注的對象。從測試對象的角度,電源完整性測試可分為兩步分,電源系統(tǒng)特性測試和電源地噪聲測試。前者是對系統(tǒng)供電部分性能的測試(無源測試),后者是直接測試系統(tǒng)工作時的電源地噪聲(有源測試),同步開關(guān)噪聲也可歸類為電源地噪聲。

測試電源系統(tǒng)性能時,通常使用網(wǎng)絡(luò)分析儀,測試對象是電源系統(tǒng)的Self-Impedance和Transfer-Impedance。一般情況下,電源系統(tǒng)的阻抗均遠小于網(wǎng)絡(luò)分析儀系統(tǒng)阻抗(50歐姆),所以測試時只要做直通校準就可以了,利用公式S21=Z/25就可以得到電源系統(tǒng)的阻抗。圖2所示為某單板電源阻抗特性。

測試電源地噪聲可以使用頻譜分析儀和示波器,頻譜分析儀的輸入端口不能接入直流分量,因此在測試電源地噪聲時,必須在測試夾具中串連DC-Blocking。頻譜分析儀的輸入阻抗為50歐姆,電源地網(wǎng)絡(luò)的阻抗一般為毫歐姆級,所以,測試夾具不會對待測系統(tǒng)產(chǎn)生影響。示波器的輸入阻抗隨設(shè)置的不同而改變,以泰克公司的TDS784為例,其低頻截至頻率隨耦合方式和系統(tǒng)阻抗變化而變化,如表2所示。

上面所描述的方法都是測試單板上的電源地噪聲,而真正影響芯片工作的是芯片內(nèi)的電源地噪聲,這時需要借助同步開關(guān)噪聲測試來確定芯片內(nèi)的電源地噪聲。設(shè)芯片有N個IO端口,令其中一個保持靜止,另外N-1個同時翻轉(zhuǎn),測試靜止網(wǎng)絡(luò)上的信號波形,即同步開關(guān)噪聲。同步開關(guān)噪聲中既包括電源地噪聲,也包括封裝內(nèi)不同信號之間的串擾,目前沒有辦法將二者完全區(qū)分開。

表2:示波器輸入阻抗隨設(shè)置而改變

時鐘信號抖動的測試

在一些高端產(chǎn)品中,抖動逐漸成為影響產(chǎn)品性能的重要指標,這里僅對如何利用頻譜分析儀測試時鐘信號抖動及問題定位做簡單介紹,關(guān)于數(shù)據(jù)信號的抖動測試暫不涉及。

在大多數(shù)系統(tǒng)中,時鐘都是由晶振或鎖相環(huán)產(chǎn)生。時鐘信號的抖動測試比較簡單,不需要高端的測試儀器,使用常用的頻譜分析儀就可以做問題定位。理想的時鐘信號的頻譜是干凈的離散頻譜,僅在時鐘頻率的倍頻上有分量。如果時鐘信號出現(xiàn)抖動,在這些倍頻的附近會出現(xiàn)旁瓣,抖動大小與這些旁瓣的功率大小成正比。

利用頻譜分析儀測試時鐘抖動的具體方法是在時鐘信號鏈路上任意找一個可測試點,將該點信號通過DC-Blocking連接至頻譜分析儀,觀察測試結(jié)果。由于測試夾具是線性系統(tǒng),因此,不必擔心產(chǎn)生新的頻譜分量。前面提到時鐘都是由晶振或鎖相環(huán)產(chǎn)生,在這種情況下,引入時鐘抖動的重要原因是晶振或鎖相環(huán)的電源噪聲。利用前面介紹的方法測試所得的晶振或鎖相環(huán)的電源噪聲,與時鐘頻譜中的旁瓣做對比,基本可以確定出導致時鐘抖動的原因。問題的解決辦法是根據(jù)時鐘頻譜旁瓣,重新設(shè)計晶振或鎖相環(huán)的濾波電路,在一般情況下,這些問題可以通過合理選擇濾波電容解決。

DesignCon2005的技術(shù)方向

DesignCon是每年互連技術(shù)領(lǐng)域的第一次大會,每年的大會上在今年DesignCon2005中,主要有以下一些技術(shù)發(fā)展趨勢:

1. 單純的電源完整性的仿真與測試在業(yè)界已經(jīng)有很多應(yīng)用,不再是分析工作中的難點。

2. 電容和電感(磁珠)的建模已經(jīng)在業(yè)界推廣,其方法已經(jīng)較為完善。

3. 互連設(shè)計的重點向封裝移動,板級分析已經(jīng)較為成熟,同步開關(guān)噪聲的仿真與測試逐漸成為業(yè)界關(guān)注的問題。

4. 抖動(Jitter)的測試方法及標準逐漸成為業(yè)界關(guān)注的問題,大會上有多家測試設(shè)備供應(yīng)商推出自己的抖動分析儀。

總結(jié)

本文簡要的對目前互連設(shè)計領(lǐng)域的測試對象和測試方法做了簡要的介紹。隨著信號速率的不斷提高,逐漸出現(xiàn)一些新的測試內(nèi)容,其中包括電源地噪聲、無源器件建模、抖動等內(nèi)容。作者根據(jù)自己的工作經(jīng)驗,提出了對于這些新的測試內(nèi)容的測試方法。在傳統(tǒng)的信號波形測試中,主要應(yīng)考慮減小地線長度,以避免Pigtail耦合入噪聲,降低測試精度。在未來的互連設(shè)計中,由于信號工作頻率提升,工作重點將向芯片封裝轉(zhuǎn)移,相關(guān)的測試和建模技術(shù)將成為工作重點。

來源:維庫電子市場網(wǎng)

-

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424272 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44638

發(fā)布評論請先 登錄

PCB阻抗測試設(shè)備怎么選?

從內(nèi)存接口到PCIe/CXL、以太網(wǎng)及光互連,高速互連芯片市場分析

立訊精密在高速互連領(lǐng)域取得里程碑式突破

高速PCB打樣必知:細節(jié)決定成敗,這些點你不能忽視!

如何選擇合適的高頻PCB電路板制造商?

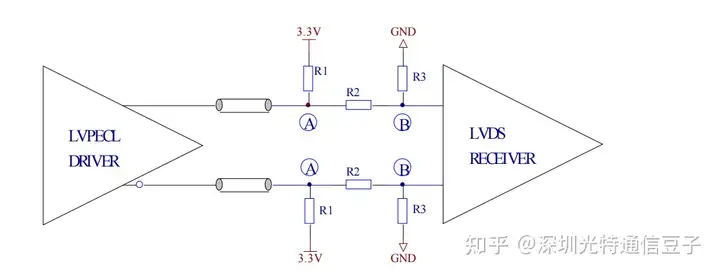

LVPECL 與 LVDS 及 PECL 與 LVDS 的互連技術(shù)解析

立訊技術(shù)高速裸線技術(shù)如何搶占高速互連賽道

GT-BGA-2000高速BGA測試插座

如何選擇合適的物聯(lián)網(wǎng)藍牙模塊?

高頻高速PCB測試解決方案

USB示波器的高速接口測試需要哪些參數(shù)?

光纖VS 同軸互連:如何選擇正確的高速測試方案?

PCB互連應(yīng)力測試與溫度沖擊測試的區(qū)別

高速PCB互連怎樣選擇合適的測試技術(shù)

高速PCB互連怎樣選擇合適的測試技術(shù)

評論