互連設(shè)計(jì)技術(shù)包括測(cè)試、仿真以及各種相關(guān)標(biāo)準(zhǔn),其中測(cè)試是驗(yàn)證各種仿真分析結(jié)果的方法和手段。優(yōu)秀的測(cè)試方法和手段是保證互連設(shè)計(jì)分析的必要條件,對(duì)于傳統(tǒng)的信號(hào)波形測(cè)試,主要應(yīng)當(dāng)關(guān)注的是探頭引線(xiàn)的長(zhǎng)度,避免Pigtail引入不必要的噪聲。本文主要討論互連測(cè)試技術(shù)的新應(yīng)用及其發(fā)展。

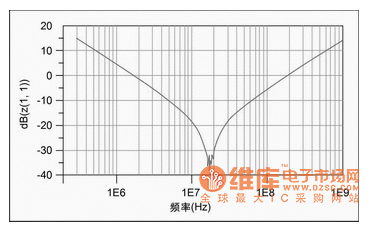

圖1:0.1uF電容阻抗曲線(xiàn)。

近些年,隨著信號(hào)速率的不斷提升,測(cè)試對(duì)象出現(xiàn)了顯著的變化,不再僅僅局限于傳統(tǒng)的利用示波器測(cè)試信號(hào)波形,電源地噪聲、同步開(kāi)關(guān)噪聲(SSN)、抖動(dòng)(Jitter)逐漸成為互連設(shè)計(jì)工程師的關(guān)注重點(diǎn),一些射頻領(lǐng)域的儀器已被應(yīng)用于互連設(shè)計(jì)。互連設(shè)計(jì)中常用的測(cè)試儀器包括頻譜分析儀、網(wǎng)絡(luò)分析儀、示波器以及這些儀器所使用的各種探頭和夾具,為了適應(yīng)不斷提高的信號(hào)速率,這些測(cè)試儀器的使用方法發(fā)生了顯著的變化。本文以這些測(cè)試儀器為工具,主要從以下幾個(gè)方面介紹近年來(lái)互連設(shè)計(jì)測(cè)試技術(shù)的發(fā)展。

1. 測(cè)試的校準(zhǔn)方法

2. 無(wú)源器件的建模方法

3. 電源完整性測(cè)試

4. 時(shí)鐘信號(hào)抖動(dòng)的測(cè)試方法

在文章的最后,還將結(jié)合剛剛結(jié)束的DesignCon2005大會(huì)對(duì)未來(lái)測(cè)試技術(shù)的發(fā)展作簡(jiǎn)要介紹。

校準(zhǔn)方法

在三種常用的測(cè)試儀器中,網(wǎng)絡(luò)分析儀的校準(zhǔn)方法最為嚴(yán)謹(jǐn),頻譜分析儀次之,示波器的校準(zhǔn)方法最為簡(jiǎn)單。因此,我們這里主要討論網(wǎng)絡(luò)分析儀的校準(zhǔn)方法。網(wǎng)絡(luò)分析儀常用的校準(zhǔn)方法有三種,Thru、TRL和SOLT。三種方法的特性如表1所示。

表1:網(wǎng)絡(luò)分析儀常用的校準(zhǔn)

方法有三種,Thru、TRL和SOLT

Thru的實(shí)質(zhì)是歸一化,校準(zhǔn)時(shí)網(wǎng)絡(luò)分析儀記錄夾具的測(cè)試結(jié)果(S21_C),在實(shí)際測(cè)試中,直接將測(cè)試結(jié)果(S21_M)與S21_C相除,即得到待測(cè)件的測(cè)試結(jié)果(S21_A)。Thru校準(zhǔn)忽略了測(cè)試夾具中的不匹配造成的反射以及空間中的電磁耦合,因此,它的校準(zhǔn)精度最低。在僅測(cè)試S21,而且測(cè)試精度要求不高的情況下可以使用該校準(zhǔn)方式。

在PCB等非Coaxial結(jié)構(gòu)中,有時(shí)需要對(duì)走線(xiàn)、過(guò)孔、連接器等的特性做測(cè)試。在這種情況下,測(cè)試儀器供應(yīng)商沒(méi)有提供標(biāo)準(zhǔn)校準(zhǔn)件,而且測(cè)試人員也很難在測(cè)試校準(zhǔn)端口做出良好的開(kāi)路、短路、匹配負(fù)載等校準(zhǔn)件,因此,不能做傳統(tǒng)的SOLT校準(zhǔn)。利用TRL校準(zhǔn)的優(yōu)點(diǎn)是不需要標(biāo)準(zhǔn)校準(zhǔn)件,可以將測(cè)試校準(zhǔn)端口延伸至所需要的位置。目前TRL校準(zhǔn)在PCB結(jié)構(gòu)測(cè)試中的使用已經(jīng)比較廣泛。

SOLT通常被認(rèn)為是標(biāo)準(zhǔn)的校準(zhǔn)方法,校準(zhǔn)模型中共有12個(gè)校準(zhǔn)誤差參數(shù),通過(guò)使用短路、開(kāi)路、負(fù)載和直通對(duì)各種誤差做校準(zhǔn)計(jì)算。由于測(cè)試儀器供應(yīng)商通常僅提供Coaxial校準(zhǔn)件,所以在非Coaxial結(jié)構(gòu),無(wú)法使用SOLT校準(zhǔn)方法。

以上三種校準(zhǔn)方法都可以利用信號(hào)流圖的方式做詳細(xì)的分析,其中各個(gè)誤差參數(shù)在信號(hào)流圖中均有對(duì)應(yīng)參數(shù)。通過(guò)信號(hào)流圖,可以很清楚的了解各種校準(zhǔn)方法的誤差敏感度,從而了解實(shí)際測(cè)試的誤差范圍。這里需要提出的一點(diǎn)是,即使是標(biāo)準(zhǔn)的SOLT校準(zhǔn)方法,在校準(zhǔn)模型中也忽略了五個(gè)誤差參數(shù)。通常情況下,這五個(gè)誤差參數(shù)不會(huì)影響校準(zhǔn)精度。但在使用時(shí)如果不注意校準(zhǔn)夾具的設(shè)計(jì),會(huì)出現(xiàn)無(wú)法校不準(zhǔn)的現(xiàn)象。

頻譜分析儀內(nèi)部提供一個(gè)標(biāo)準(zhǔn)源供校準(zhǔn)使用,校準(zhǔn)時(shí)只需要將內(nèi)部標(biāo)準(zhǔn)源通過(guò)測(cè)試夾具與輸入端口相連即可,校準(zhǔn)所需時(shí)間約為10分鐘。示波器的校準(zhǔn)則更為簡(jiǎn)單,將探頭連接至內(nèi)部標(biāo)準(zhǔn)源,確認(rèn)即可,校準(zhǔn)所需時(shí)間約為1分鐘。

無(wú)源器件的測(cè)試和建模

隨著信號(hào)速率的不斷升高,無(wú)源器件在信號(hào)鏈路中的作用越來(lái)越重要,系統(tǒng)性能仿真分析準(zhǔn)確與否,往往決定于無(wú)源器件的模型精度。因此,無(wú)源器件的測(cè)試和建模逐漸成為各個(gè)設(shè)備供應(yīng)商的互連設(shè)計(jì)中的重要組成部分。常用的無(wú)源器件有以下幾種:

1. 連接器

2. PCB走線(xiàn)及過(guò)孔

3. 電容

4. 電感(磁珠)

在高速信號(hào)完整性設(shè)計(jì)中,連接器對(duì)信號(hào)鏈路的影響最大。對(duì)于經(jīng)常使用的高速連接器,通常的做法是按照TRL校準(zhǔn)方法做校準(zhǔn)夾具,對(duì)連接器進(jìn)行測(cè)試建模,供仿真分析使用。PCB走線(xiàn)及過(guò)孔的測(cè)試建模方法與連接器相類(lèi)似,也使用TRL校準(zhǔn)將測(cè)試端口移至所需位置,然后測(cè)試建模。

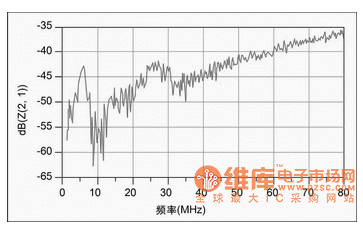

圖2:某單板電源阻抗特性

電容模型在信號(hào)完整性分析中有應(yīng)用,更主要的應(yīng)用在電源完整性分析中。業(yè)界常用的電容建模儀器是阻抗分析儀和網(wǎng)絡(luò)分析儀,分別適用于不同頻段,阻抗分析儀適用于低頻段,網(wǎng)絡(luò)分析儀適用于高頻段。如果具體實(shí)際測(cè)試中使用網(wǎng)絡(luò)分析儀做電源完整性測(cè)試,建議在電容建模的全頻段均使用網(wǎng)絡(luò)分析儀,以保證建模和應(yīng)用的一致性。由于電容的阻抗較小,在使用網(wǎng)絡(luò)分析儀建模時(shí),通常使用并聯(lián)方式。目前業(yè)界在電容建模中沒(méi)有解決的問(wèn)題是如何消除夾具與電容之間的互耦,以減小夾具對(duì)建模結(jié)果的影響。

在傳統(tǒng)的電源設(shè)計(jì)中,經(jīng)常會(huì)使用電感(磁珠)對(duì)電源做隔離,以減小噪聲干擾。而實(shí)際設(shè)計(jì)中,經(jīng)常會(huì)出現(xiàn)去除隔離電感(磁珠),電源地噪聲反而減小。這是由于電感(磁珠)與其它濾波器件產(chǎn)生諧振。為了避免這種情況的發(fā)生,有必要對(duì)電感(磁珠)建模并仿真以避免諧振。業(yè)界常用的電感(磁珠)建模方式也是采用網(wǎng)絡(luò)分析儀,具體方法與電容建模相類(lèi)似,不同之處在于電感(磁珠)建模時(shí)采用串聯(lián)方式,電容建模時(shí)采用并聯(lián)方式。

上面的幾種無(wú)源器件的建模主要應(yīng)用在信號(hào)完整性和電源完整性方面,近些年EMI的仿真分析正逐步發(fā)展,關(guān)于EMI無(wú)源器件的測(cè)試建模也逐漸成為互連設(shè)計(jì)的重點(diǎn)。如圖1所示為電容的阻抗曲線(xiàn)。

電源完整性測(cè)試

隨著芯片功率不斷升高,工作電壓不斷降低,電源地噪聲逐漸成為互連設(shè)計(jì)中關(guān)注的對(duì)象。從測(cè)試對(duì)象的角度,電源完整性測(cè)試可分為兩步分,電源系統(tǒng)特性測(cè)試和電源地噪聲測(cè)試。前者是對(duì)系統(tǒng)供電部分性能的測(cè)試(無(wú)源測(cè)試),后者是直接測(cè)試系統(tǒng)工作時(shí)的電源地噪聲(有源測(cè)試),同步開(kāi)關(guān)噪聲也可歸類(lèi)為電源地噪聲。

測(cè)試電源系統(tǒng)性能時(shí),通常使用網(wǎng)絡(luò)分析儀,測(cè)試對(duì)象是電源系統(tǒng)的Self-Impedance和Transfer-Impedance。一般情況下,電源系統(tǒng)的阻抗均遠(yuǎn)小于網(wǎng)絡(luò)分析儀系統(tǒng)阻抗(50歐姆),所以測(cè)試時(shí)只要做直通校準(zhǔn)就可以了,利用公式S21=Z/25就可以得到電源系統(tǒng)的阻抗。圖2所示為某單板電源阻抗特性。

測(cè)試電源地噪聲可以使用頻譜分析儀和示波器,頻譜分析儀的輸入端口不能接入直流分量,因此在測(cè)試電源地噪聲時(shí),必須在測(cè)試夾具中串連DC-Blocking。頻譜分析儀的輸入阻抗為50歐姆,電源地網(wǎng)絡(luò)的阻抗一般為毫歐姆級(jí),所以,測(cè)試夾具不會(huì)對(duì)待測(cè)系統(tǒng)產(chǎn)生影響。示波器的輸入阻抗隨設(shè)置的不同而改變,以泰克公司的TDS784為例,其低頻截至頻率隨耦合方式和系統(tǒng)阻抗變化而變化,如表2所示。

上面所描述的方法都是測(cè)試單板上的電源地噪聲,而真正影響芯片工作的是芯片內(nèi)的電源地噪聲,這時(shí)需要借助同步開(kāi)關(guān)噪聲測(cè)試來(lái)確定芯片內(nèi)的電源地噪聲。設(shè)芯片有N個(gè)IO端口,令其中一個(gè)保持靜止,另外N-1個(gè)同時(shí)翻轉(zhuǎn),測(cè)試靜止網(wǎng)絡(luò)上的信號(hào)波形,即同步開(kāi)關(guān)噪聲。同步開(kāi)關(guān)噪聲中既包括電源地噪聲,也包括封裝內(nèi)不同信號(hào)之間的串?dāng)_,目前沒(méi)有辦法將二者完全區(qū)分開(kāi)。

表2:示波器輸入阻抗隨設(shè)置而改變

時(shí)鐘信號(hào)抖動(dòng)的測(cè)試

在一些高端產(chǎn)品中,抖動(dòng)逐漸成為影響產(chǎn)品性能的重要指標(biāo),這里僅對(duì)如何利用頻譜分析儀測(cè)試時(shí)鐘信號(hào)抖動(dòng)及問(wèn)題定位做簡(jiǎn)單介紹,關(guān)于數(shù)據(jù)信號(hào)的抖動(dòng)測(cè)試暫不涉及。

在大多數(shù)系統(tǒng)中,時(shí)鐘都是由晶振或鎖相環(huán)產(chǎn)生。時(shí)鐘信號(hào)的抖動(dòng)測(cè)試比較簡(jiǎn)單,不需要高端的測(cè)試儀器,使用常用的頻譜分析儀就可以做問(wèn)題定位。理想的時(shí)鐘信號(hào)的頻譜是干凈的離散頻譜,僅在時(shí)鐘頻率的倍頻上有分量。如果時(shí)鐘信號(hào)出現(xiàn)抖動(dòng),在這些倍頻的附近會(huì)出現(xiàn)旁瓣,抖動(dòng)大小與這些旁瓣的功率大小成正比。

利用頻譜分析儀測(cè)試時(shí)鐘抖動(dòng)的具體方法是在時(shí)鐘信號(hào)鏈路上任意找一個(gè)可測(cè)試點(diǎn),將該點(diǎn)信號(hào)通過(guò)DC-Blocking連接至頻譜分析儀,觀察測(cè)試結(jié)果。由于測(cè)試夾具是線(xiàn)性系統(tǒng),因此,不必?fù)?dān)心產(chǎn)生新的頻譜分量。前面提到時(shí)鐘都是由晶振或鎖相環(huán)產(chǎn)生,在這種情況下,引入時(shí)鐘抖動(dòng)的重要原因是晶振或鎖相環(huán)的電源噪聲。利用前面介紹的方法測(cè)試所得的晶振或鎖相環(huán)的電源噪聲,與時(shí)鐘頻譜中的旁瓣做對(duì)比,基本可以確定出導(dǎo)致時(shí)鐘抖動(dòng)的原因。問(wèn)題的解決辦法是根據(jù)時(shí)鐘頻譜旁瓣,重新設(shè)計(jì)晶振或鎖相環(huán)的濾波電路,在一般情況下,這些問(wèn)題可以通過(guò)合理選擇濾波電容解決。

DesignCon2005的技術(shù)方向

DesignCon是每年互連技術(shù)領(lǐng)域的第一次大會(huì),每年的大會(huì)上在今年DesignCon2005中,主要有以下一些技術(shù)發(fā)展趨勢(shì):

1. 單純的電源完整性的仿真與測(cè)試在業(yè)界已經(jīng)有很多應(yīng)用,不再是分析工作中的難點(diǎn)。

2. 電容和電感(磁珠)的建模已經(jīng)在業(yè)界推廣,其方法已經(jīng)較為完善。

3. 互連設(shè)計(jì)的重點(diǎn)向封裝移動(dòng),板級(jí)分析已經(jīng)較為成熟,同步開(kāi)關(guān)噪聲的仿真與測(cè)試逐漸成為業(yè)界關(guān)注的問(wèn)題。

4. 抖動(dòng)(Jitter)的測(cè)試方法及標(biāo)準(zhǔn)逐漸成為業(yè)界關(guān)注的問(wèn)題,大會(huì)上有多家測(cè)試設(shè)備供應(yīng)商推出自己的抖動(dòng)分析儀。

總結(jié)

本文簡(jiǎn)要的對(duì)目前互連設(shè)計(jì)領(lǐng)域的測(cè)試對(duì)象和測(cè)試方法做了簡(jiǎn)要的介紹。隨著信號(hào)速率的不斷提高,逐漸出現(xiàn)一些新的測(cè)試內(nèi)容,其中包括電源地噪聲、無(wú)源器件建模、抖動(dòng)等內(nèi)容。作者根據(jù)自己的工作經(jīng)驗(yàn),提出了對(duì)于這些新的測(cè)試內(nèi)容的測(cè)試方法。在傳統(tǒng)的信號(hào)波形測(cè)試中,主要應(yīng)考慮減小地線(xiàn)長(zhǎng)度,以避免Pigtail耦合入噪聲,降低測(cè)試精度。在未來(lái)的互連設(shè)計(jì)中,由于信號(hào)工作頻率提升,工作重點(diǎn)將向芯片封裝轉(zhuǎn)移,相關(guān)的測(cè)試和建模技術(shù)將成為工作重點(diǎn)。

來(lái)源:維庫(kù)電子市場(chǎng)網(wǎng)

-

pcb

+關(guān)注

關(guān)注

4406文章

23883瀏覽量

424429 -

華強(qiáng)pcb線(xiàn)路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44644

發(fā)布評(píng)論請(qǐng)先 登錄

PCB板焊點(diǎn)高低溫環(huán)境下強(qiáng)度測(cè)試|推拉力測(cè)試機(jī)選型指南+實(shí)測(cè)演示

PCB阻抗測(cè)試設(shè)備怎么選?

國(guó)產(chǎn)PCB阻抗測(cè)試分析儀品牌:Bamtone班通

從內(nèi)存接口到PCIe/CXL、以太網(wǎng)及光互連,高速互連芯片市場(chǎng)分析

TE推出的AMPMODU互連系統(tǒng)有何特點(diǎn)?赫聯(lián)電子怎么樣?

金相技術(shù)在PCB失效分析中應(yīng)用

TE推出AMPMODU互連系統(tǒng)具有哪些產(chǎn)品特性?-赫聯(lián)電子

PCB分板應(yīng)力測(cè)試方法和步驟

XSR芯片間互連技術(shù)的定義和優(yōu)勢(shì)

互連層RC延遲的降低方法

光纖VS 同軸互連:如何選擇正確的高速測(cè)試方案?

PCB互連應(yīng)力測(cè)試與溫度沖擊測(cè)試的區(qū)別

PCB互連設(shè)計(jì)中的測(cè)試是怎樣設(shè)計(jì)的

PCB互連設(shè)計(jì)中的測(cè)試是怎樣設(shè)計(jì)的

評(píng)論