在進行比較復雜的板子設計時,你必須進行一些設計權衡,而這些權衡會存在一些影響到PCB的電源分配網絡設計的因素。

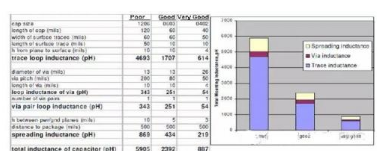

當電容安裝在PCB板上時,會存在一個額外的回路電感,這個電感就與電容的安裝有關系。回路電感值的大小依賴于設計,回路電感的大小取決于電容到過孔這段線的線寬和線長。走線的長度即連接電容和電源/地平面的長度、兩個孔間的距離、孔的直徑、電容的焊盤等等。如圖1所示為各種電容的安裝圖形:

圖1 最佳的和最差的電容布局

對于電容的安裝和傳播電感,接下來是三種不同情況的設計。圖2表示的是各種設計情況對回路電感量的引入情況:

圖2 最佳的和最差的電容布局

情況1-差的設計

設計人員不關注電源分配網絡(PDN)的設計。

孔的間距沒有優化。

電源和地平面間的距離沒有優化。

孔到電容引腳之間的走線距離較長。

對于整個回路電感大小來講,回路電感主要來自所布的線,因為與其它兩種情況比較,差的設計的線長是它們(較好的設計和非常好的設計)的5倍。從安裝電容的底層到最近平面的距離也是回路電感大小的主要因素,因為這是沒有優化的(10mil),走線對整個回路電感大小的影響非常大。同樣,因為設計人員在電源和地之間用了10mil的電介質材料,那么回路電感的次要因素來自傳播電感。過孔間的距離沒有優化的效果相對于小孔的長度就沒有那么顯著,孔的影響在比較長的過孔時會變得更大。

情況2-好的設計

設計人員關注了部分電源分配網絡(PDN)的設計。

孔的間距有所改善,孔的長度保持不變。

電源和地平面間的距離有所改善。

過孔到電容引腳之間的走線距離經過了優化。

走線的回路電感依然還是整個回路電感的主要貢獻者。好的設計的走線回路電感要比差的設計情況的走線回路電感小2.7倍左右,因為設計人員減小了電介質的厚度,從10mil減小到了5mil,傳播電感減小了一半。由于減小了過孔間的距離,過孔的影響有了一點點改善。

權衡多路設計的情況

在一塊有多路外設的PCB打樣板上,你的設計就不能再共享一個供電電源。這也許需要你通過你的設計去執行DDR的電源接口,聯合各種I/O口的電源軌跡,或者聯合各種接收端的電源軌跡以減少PCB的BOM成本和PCB的布局復雜度。

電源軌跡共享增加了PDN的復雜度,同時在PCB上和die的位置處也增加了大量的噪聲。對于多路的情況,設計電源的分配解決方法主要有兩步:

1、低頻解決方法

2、高頻解決方法

在非常低頻的時候,第一步確保VRM的大小是否適合處理各種電流的需要。

低頻去耦一定要考慮清楚各種組合電源供電電流的情況。Bulk電容一定要選擇能覆蓋目標阻抗所覆蓋的頻段,做到精確的知道頻率范圍是有困難的,因為這有一個區域超過了阻抗曲線。這是在die上給定的電源區域,建立在自己的最大電流消耗上,而不是與其它路電流相關聯的由同一個供電電源供電組合的電流消耗。對于設計,bulk電容去耦的頻率范圍估計是從DC到大約5~10MHz。

這個例子是電源共享在核心電源供電(Vcc)和PCI Express hard IP Block(VccHIP)電源供電,例外的原因是:

VCC的電流會比VCCHIP的大很多。

對比VCC和VCCHIP,VCC的BGA的過孔電感會比VCCHIP低很多。

對比VCC和VCCHIP,VCC的截止頻率會比VCCHIP低很多。

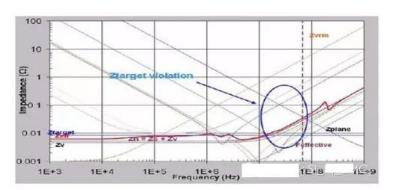

因此,對于電源設計情況,在BGA過孔處使用最高截止頻率去耦是不適用的。如圖3所示的是VCC、VCCHIP電源路組合阻抗曲線不符合目標阻抗的情況,相當于不符合VCCHIP的截止頻率去耦,這是因為去耦電容效果被限制了。

圖3 VCCHIP的截止頻率阻抗曲線

在這種情況下,你必須基于PCB去耦項目用整個瞬態電流來計算目標阻抗曲線,相當于電源路截止頻率的最大的電流消耗。在VCC和VCCHIP電源路共享的例子中,你必須用VCC電源路的截止頻率。如圖3所示為核心電源去耦的截止頻率的組合電源路的阻抗曲線。對于核心電源,用沿著BGA的球或者過孔的(VCC+VCCHIP)的總電流得到阻抗曲線。那么你可以檢查核對結果是否符合單個電源設計指導的目標阻抗。

基于同樣的去耦項目與圖4-A一樣,圖4-B所示為VCCHIP電源的阻抗曲線。但是,當得到這條曲線時,只有對于VCCHIP需要考慮電流消耗和BGA過孔數。如圖4-B所示,直到VCCHIP電源的截止頻率,VCCHIP的阻抗曲線都達到了目標阻抗。

最終的去耦項目必須達到各自目標阻抗的頻率。如果存在一些特殊的違反設計目標的情況,可以盡量小的調整以優化去耦項目。

遇到類似的情況,可以根據VCC和VCCHIP的例子對任何供電電源組合進行優化。

在一塊PCB板上,當有多個FPGA需要從同一個電源供電時,你可以使用相似的方法來應對這種情況。對于設計低頻解決方案一定要用芯片的總電流消耗,對于高頻解決方案設計,一定要用其中一個芯片的電流消耗。你可以使用同樣數目的電容給其他芯片在高頻情況時去耦。

-

pcb

+關注

關注

4404文章

23878瀏覽量

424272 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44638

發布評論請先 登錄

PCB設計師必看!這些‘反常識’操作正在毀掉你的電路板

深度解讀PCB設計布局準則

PCB設計與工藝規范

PCB設計,輕松歸檔,效率倍增!

pcb設計和電源之間怎樣來權衡

pcb設計和電源之間怎樣來權衡

評論