Kilopass Technology,Inc。宣布其XPM技術現在可用于ASIC和SoC,使用標準邏輯CMOS 90納米硅工藝,以及目前使用0.18,0.15和0.13微米工藝的產品。

XPM,a獨特的嵌入式一次性可編程(OTP)NVM技術,提供可擴展性與先進硅工藝的組合,例如90納米,低標準邏輯CMOS制造成本,從幾位到多兆位的存儲密度以及高度安全的存儲。憑借其完整的位尺寸范圍和廣泛的應用,XPM幾乎可以增強任何芯片設計。

博士。 Kilopass Technology首席執行官Jack Peng指出,“我們已經將我們的專利XPM技術發送給了十幾個客戶,我們非常高興地宣布,我們已經測試并驗證了90納米的硅,1000小時的老化,我們的客戶希望在未來幾個月內從硅原型轉向大批量生產。“

作為外部存儲芯片的替代品,XPM技術可用于高密度嵌入式存儲器應用,用于發布游戲,電影和其他多媒體內容,以及嵌入式MCU和基于DSP的系統中的安全固件存儲。 XPM還可用于智能卡的安全ID和數據存儲,嵌入式ID和參數存儲,存儲加密密鑰,模擬微調和校準參數存儲,存儲唯一配置代碼和嵌入式存儲器修復。

有關XPM技術的更多信息

XPM專利的熔絲可編程技術每個存儲器單元使用1.5個晶體管,可通過外部或內部電壓源以低編程電流進行編程,并提供快速讀取訪問時間40nsec - 70nsec(1Mbit,0.18微米工藝)。需要多次編程的應用可以使用多扇區方法,最小的芯片面積損失。例如,從1K位基于XPM的存儲器到8K位的大小調整提供了8個扇區,用于有限時間的可重新編程,并且它增加了可忽略不計的裸片面積。

XPM內存技術可靠性&安全性

XPM技術非常安全。數據在大多數系統(超過20年)的使用壽命期間永久保留,并且不受逆向工程的影響,因為無法通過顯微鏡或電壓對比測試來檢測存儲的數據。

可用性

現在可以獲得XPM內存技術的許可證,包括GDSII布局以及模擬和時序模型。

-

CMOS

+關注

關注

58文章

6217瀏覽量

242841 -

asic

+關注

關注

34文章

1274瀏覽量

124586 -

XPM

+關注

關注

0文章

12瀏覽量

8914

發布評論請先 登錄

【封裝技術】幾種常用硅光芯片光纖耦合方案

燒結銀膏在硅光技術和EML技術的應用

【「龍芯之光 自主可控處理器設計解析」閱讀體驗】--LoongArch的SOC邏輯設計

臺階儀在納米薄膜工藝監控:基于三臺階標準的高精度厚度與沉積速率測定

單片機TTL和CMOS電平知識

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

下一代高速芯片晶體管解制造問題解決了!

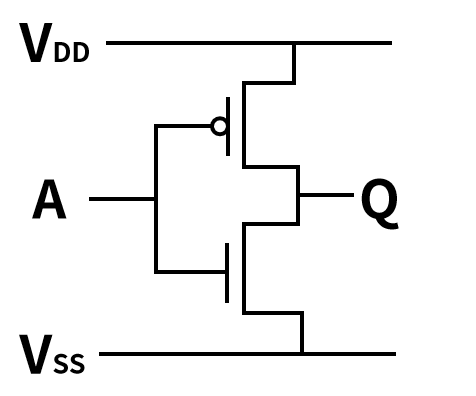

CMOS的邏輯門如何應用在電路中

實用電子電路設計(全6本)——數字邏輯電路的ASIC設計

使用BCU和標準邏輯分析儀Saleae進行功率測量時不匹配怎么解決?

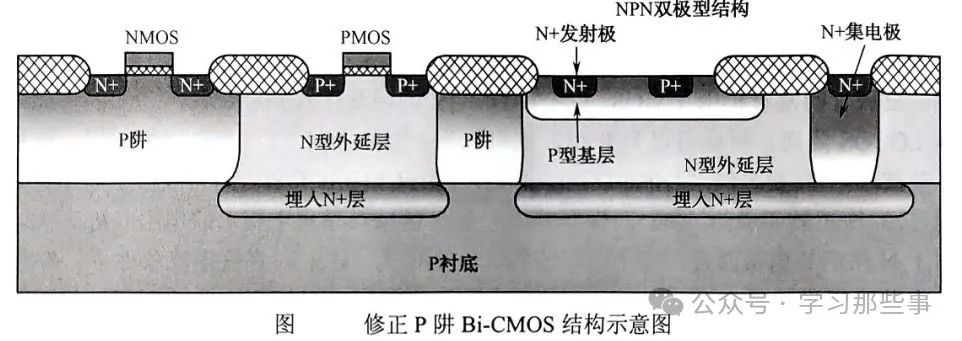

CMOS,Bipolar,FET這三種工藝的優缺點是什么?

CMOS邏輯IC是如何構成的

XPM技術使用標準邏輯CMOS 90納米硅工藝 現在可用于ASIC和SoC

XPM技術使用標準邏輯CMOS 90納米硅工藝 現在可用于ASIC和SoC

評論