學(xué)習(xí)高速PCB設(shè)計,首先要知道什么是傳輸線。信號會產(chǎn)生反射,就是因為PCB上的走線具有一定的阻抗,線上阻抗與輸出端的阻抗不匹配,就會導(dǎo)致信號反射。信號在PCB中傳輸會有延時,如果時序沒有匹配,系統(tǒng)就會罷工。這些都是因為傳輸線產(chǎn)生的問題。

什么是傳輸線?

傳輸線的定義是有信號回流的信號線(由兩條一定長度導(dǎo)線組成,一條是信號傳播路徑,另一條是信號返回路徑。),最常見的傳輸線也就是我們PCB板上的走線。

1. 分析傳輸線,一定要聯(lián)系返回路徑,單根的導(dǎo)體并不能成為傳輸線;2. 和電阻,電容,電感一樣,傳輸線也是一種理想的電路元件,但是其特性卻大不相同,用于仿真效果較好,但電路概念卻比較復(fù)雜;3. 傳輸線有兩個非常重要的特征:特性阻抗和時延。

高速PCB設(shè)計中傳輸線的概念及結(jié)構(gòu)分析

傳輸線阻抗

先來澄清幾個概念,我們經(jīng)常會看到阻抗、特性阻抗、瞬時阻抗,嚴(yán)格來講,他們是有區(qū)別的,但是萬變不離其宗,它們?nèi)匀皇亲杩沟幕径x:

將傳輸線始端的輸入阻抗簡稱為阻抗;

將信號隨時遇到的及時阻抗稱為瞬時阻抗;

如果傳輸線具有恒定不變的瞬時阻抗,就稱之為傳輸線的特性阻抗。

特性阻抗描述了信號沿傳輸線傳播時所受到的瞬態(tài)阻抗,這是影響傳輸線電路中信號完整性的一個主要因素。

如果沒有特殊說明,一般用特性阻抗來統(tǒng)稱傳輸線阻抗。

傳輸時延

Time delay又叫時延(TD),通常是指電磁信號或者光信號通過整個傳輸介質(zhì)所用的時間。在傳輸線上的時延就是指信號通過整個傳輸線所用的時間。

Propagation delay又叫傳播延遲(PD),通常是指電磁信號或者光信號在單位長度的傳輸介質(zhì)中傳輸?shù)臅r間延遲,與“傳播速度”成反比例(倒數(shù))關(guān)系,單位為“Ps/inch”或“s/m”。

從定義中可以看出時延=傳播延遲*傳輸長度(L)。

PCB的傳輸線結(jié)構(gòu)

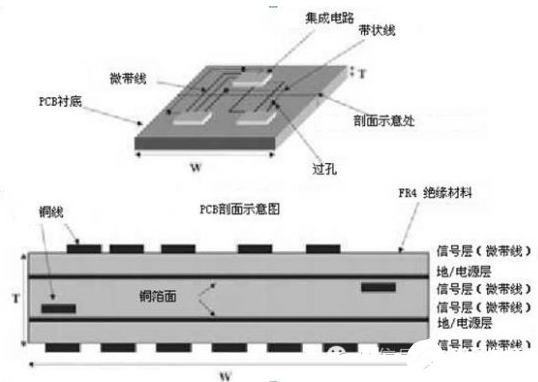

典型PCB中所見到的傳輸線結(jié)構(gòu)是由嵌入或臨近電介質(zhì)或絕緣材料,并且具有一個或多個參考平面的導(dǎo)線構(gòu)成。典型PCB中的金屬是銅,而電介質(zhì)是一種叫FR4的玻璃纖維。數(shù)字設(shè)計中最常見的兩種傳輸線類型是微帶線和帶狀線。

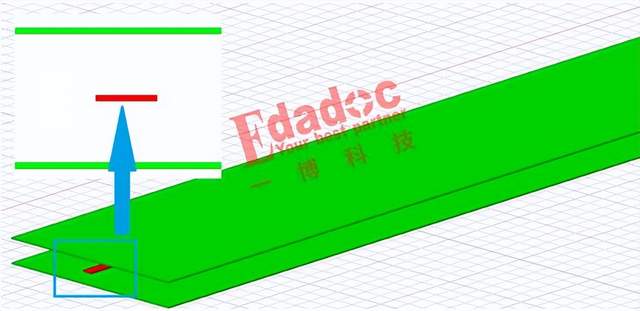

微帶線通常指PCB外層的走線,并且只有一個參考平面。微帶線有兩種類型:埋式或非埋式。埋式(有時又稱作潛入式)微帶線就是將一根傳輸線簡單地嵌入電介質(zhì)中,但其依然只有一個參考平面。帶狀線是指介于兩個參考平面之間的內(nèi)層走線。

下圖所示為PCB上不同元件之間的內(nèi)層走線(帶狀線)和外層走線(微帶線)。標(biāo)識處的剖面圖顯示了傳輸線與地/電源層的相對關(guān)系。

責(zé)任編輯:ct

-

pcb

+關(guān)注

關(guān)注

4415文章

23932瀏覽量

425678 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44701

發(fā)布評論請先 登錄

深入解析 PI7AT04:低電壓、零延遲有源傳輸線鉗位器

高速PCB設(shè)計EMI避坑指南:5個實戰(zhàn)技巧

PCB“蝕刻因子”是啥,聽說它很影響走線加工的阻抗?

深度解讀PCB設(shè)計布局準(zhǔn)則

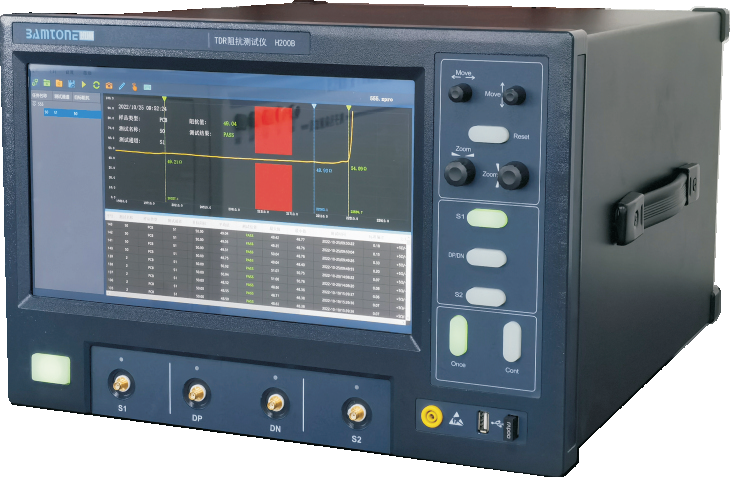

如何用TDR阻抗測量儀快速定位PCB傳輸線故障?

PCB反焊盤的樣子越詭異,高速過孔的性能越好?

知識分享-傳輸線的返回電流(信號完整性揭秘)

傳輸線高頻參數(shù)之Crosstalk

高速多層板SI/PI分析的關(guān)鍵要點是什么

原理圖和PCB設(shè)計中的常見錯誤

高頻PCB設(shè)計中出現(xiàn)的干擾分析及對策

DDR模塊的PCB設(shè)計要點

高速PCB設(shè)計中傳輸線你都有了解嗎

高速PCB設(shè)計中傳輸線你都有了解嗎

評論