本系列的第1部分介紹了數字信號如何通過PC板傳播,第2部分描述了特定的電路板疊層設計,以實現低EMI。第3部分將討論電路部分的劃分,高速走線的布線以及一些其他布局實踐,以幫助降低EMI。

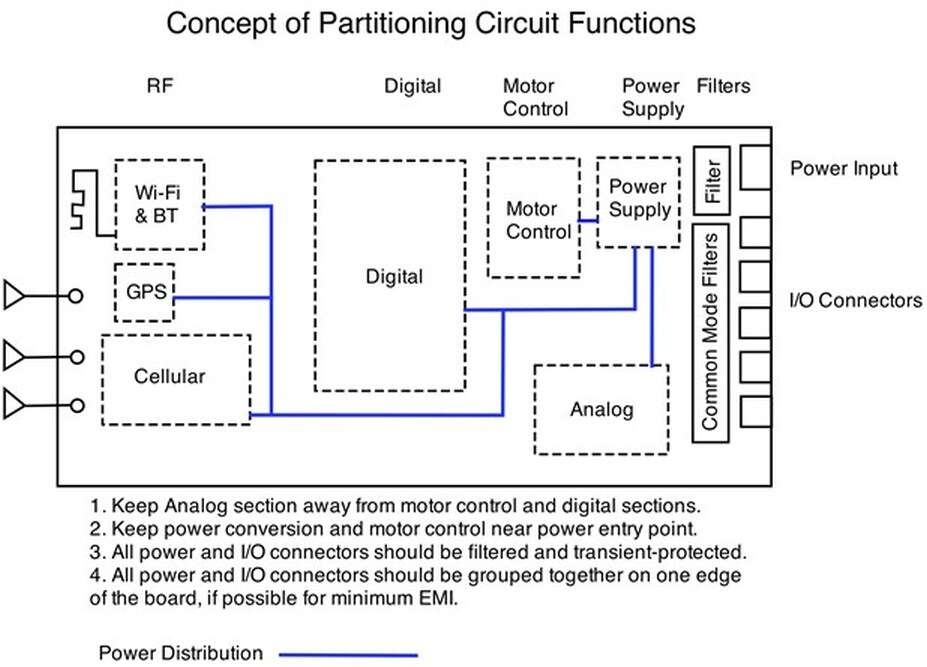

除了適當的層堆疊,在電路板上布置電路時,下一個最重要的考慮因素是電路功能的劃分,例如數字,模擬,電源轉換,RF以及電機控制或其他高功率電路等。

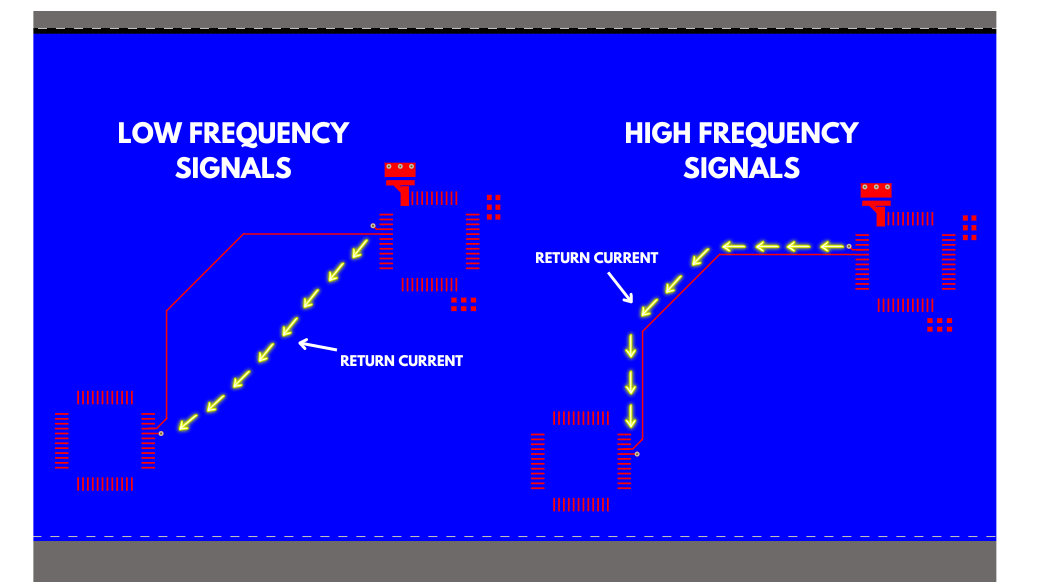

在進行電路布局之前,我們必須首先了解和可視化返回電流的流動方式以及電磁場在高速電路走線下的分布情況。在低于約50kHz的低頻下,返回電流趨向于遵循最低電阻的路徑。它們傾向于沿著源和負載之間的最短距離行進,如圖1中的綠色區域所模擬。

圖1. 50 kHz以下的返回電流場分布遵循以下路徑:阻力最小。 Keysight Technologies供圖。

大約50 kHz至100 kHz時,返回電流由于信號路徑之間的互阻抗耦合效應,傾向于遵循最低阻抗的路徑。這些電流傾向于直接在源和負載之間的信號路徑下方傳播,如圖2中的綠色區域所模擬。

圖2.頻率高于50 kHz的返回電流場分布,將通過阻抗最小的路徑返回源。 Keysight Technologies供圖。

您現在可以理解為什么要定位模擬電路了遠離數字或其他噪聲電路。保持這些“展開”的返回電流與來自噪聲電路的返回電流混合。這就是分區如此重要的主要原因。

分區

第1部分該系列描述了數字(和其他高頻)信號如何通過電路板的介電空間傳播。為避免信號耦合和串擾,您不得允許各種返回信號在同一電介質空間內混合。因此,您需要對主要電路功能進行分區。圖3演示了一個分區示例。當然,隨著電路板尺寸縮小,這將變得更具挑戰性。 Henry Ott還在參考文獻1中描述了這個概念。

圖3.如何在電路板上劃分電路功能的示例。

現在知道低頻信號的回波趨于擴散,我們可以看到任何模擬或低頻電路必須與數字,電源轉換或電機控制器電路。同樣,敏感的RF接收器電路,如GPS,蜂窩或Wi-Fi設備也必須與數字,電源轉換或電機控制器電路分開。

-

pcb

+關注

關注

4407文章

23883瀏覽量

424458 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44647

發布評論請先 登錄

深入探討PCB布局布線的專業設計要點與常見挑戰

FAQ_MA35_Family eMMC如何將映像編程到其中一個分區中,并將其他分區用于其他目的?

技術資訊 I 如何在 PCB 中降低 EMI 并優化 EMC?

高速PCB布局/布線的原則

時源芯微 PCB 布線規則詳解

高層數層疊結構PCB的布線策略

如何設計用于EMI的PCB分區和布線

如何設計用于EMI的PCB分區和布線

評論