本系列的第1部分描述了數字信號如何通過PC板傳播[參考文獻1]。 1,2,5,6]。在第2部分中,我們將研究特定的電路板設計,以實現低EMI。我在客戶的電路板設計中看到的最大問題是層疊不良。

重申第1部分中的兩個基本規則并實現數字信號電源(瞬態)是在電介質層中移動的電磁波,我們看到PC板設計有兩個非常重要的原則:

PC板上的每個信號和電源走線(或平面)都應該

傳輸線中的數字信號傳播實際上是銅跡線和GRP之間空間中電磁場的移動。

要構建傳輸線,你需要兩個相鄰的金屬片來捕獲或包含場地。例如,相鄰接地返回平面(GRP)上的微帶線或與GRP相鄰的帶狀線或與GRP相鄰的功率跡線(或平面)。例如,在電源和接地參考平面之間定位多個信號層將導致快速信號的真正EMI問題。觀察這兩個規則將決定層疊。

換句話說,每個信號或功率跟蹤(路由功率)必須具有相鄰的GRP,并且所有功率平面應具有相鄰的GRP。多個GRP應與拼接過孔矩陣連接在一起。在本文中,我們將研究幾種堆疊設計。

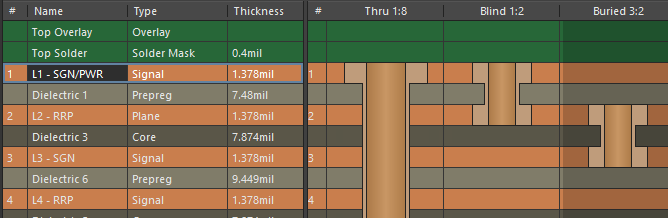

典型的六層設計(Altium)

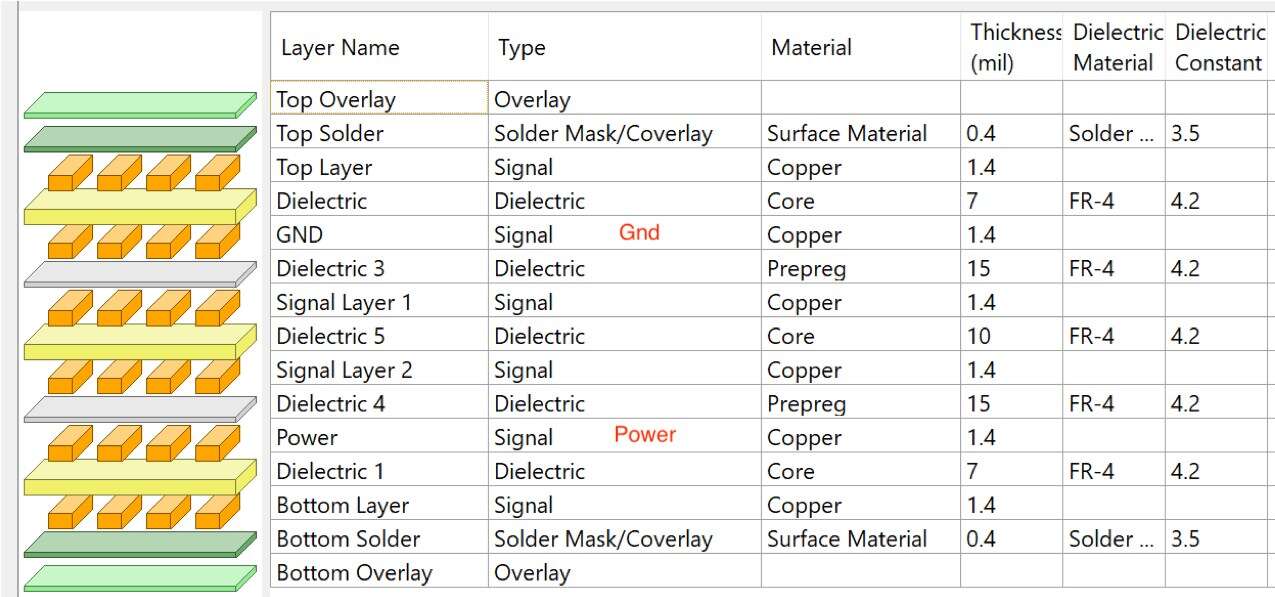

我經常看到的一個疊加是這個六層設計(圖1)。這在20世紀90年代到21世紀初可能運行良好,但是今天的速度和混合信號技術要快得多,這是EMI災難的秘訣。這有兩個問題:底部的兩個信號層以電源平面為參考,電源和接地返回平面不相鄰且距離太遠。

圖1.一種非常常見但很差的EMI疊層設計(6層示例)。信號層4和6以功率為參考,而GRP和功率平面不相鄰,其間有兩個信號層。這將耦合這兩個信號層上的電源瞬變。

除少數例外(一些DDR RAM電源和信號(例如)電流想要返回其源,這些源以GRP為參考。將這些信號引用到電源平面是非常具有EMI風險的,因為沒有明確定義的返回路徑,除了通過平面到平面的電容,在這種情況下相對較小。此外,返回路徑中的這些間隙導致場泄漏到電路板介電層的其他區域。反過來,這會導致交叉耦合和輻射EMI。

當我們將功率和GRP分成兩個信號層時,會出現第二個問題。任何電網瞬變都將在介電層內交叉耦合,沿著路徑耦合到層3和4上的任何信號跡線。如果這些平面間隔超過3-4密耳,您也會失去任何平面到平面的電容效益。

以下是幾個想法適用于符合數字信號傳播傳輸線方面的PC板疊加。

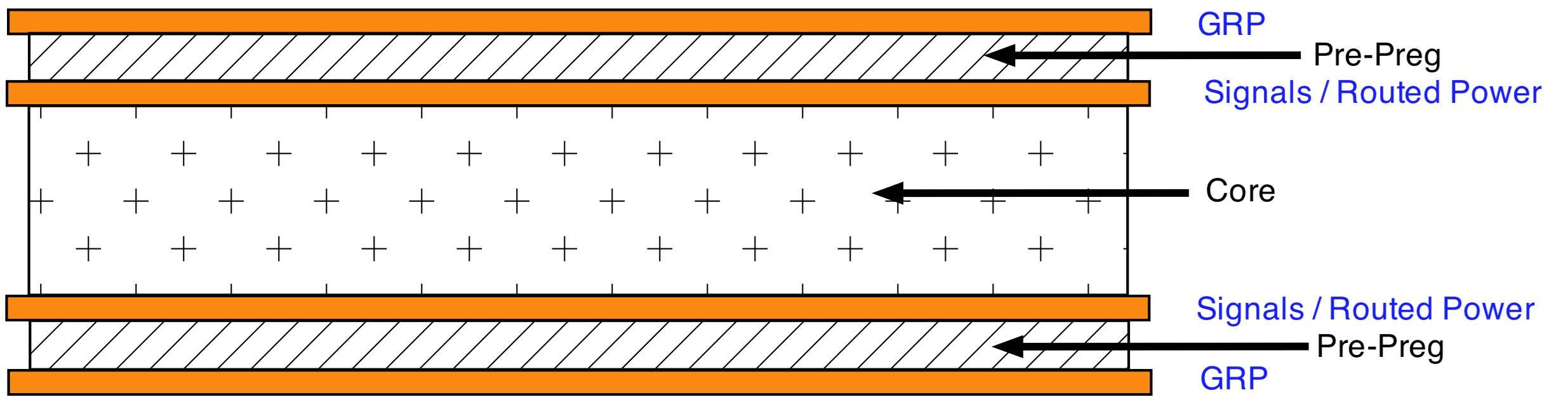

四層板:設計1

良好的四層電路板堆疊,可提高EMI(圖2)。我們使用路由或傾倒功率以及第2層和第3層上的信號來代替電源平面。因此,每個信號/功率跡線與GRP相鄰。此外,只要兩個GRP通過拼接過孔矩陣連接在一起,就可以輕松地在所有層之間運行過孔。如果沿著周邊(例如,每隔5mm)運行一排縫合過孔,則會形成法拉第籠。

圖2.這種良好的四層電路板疊層可提高EMI,使信號和布線功率保持在接地參考平面附近。

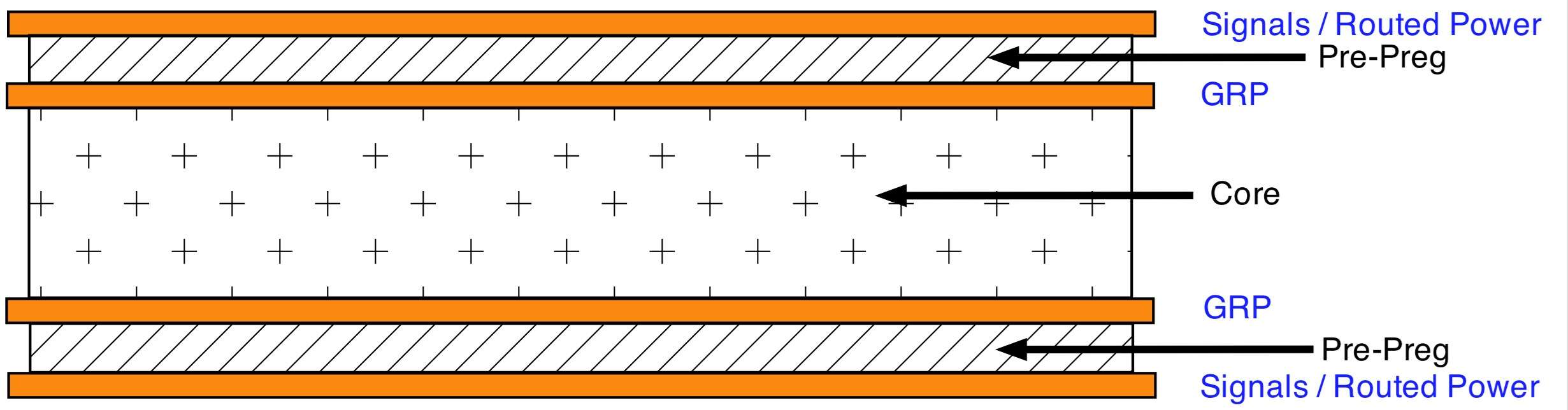

四層板:設計2

另一方面,如果您更愿意訪問信號和路由/傾倒的電源線,您可以簡單地反轉層對,這樣兩個GRP層位于中間,兩個信號層位于中間在頂部和底部,具有布線功率和足夠的去耦電容,而不是電源平面(圖3)。

圖3.這種用于改善EMI的良好的四層電路板疊層將接地參考平面放置在電路板內。結果

對于這兩種設計,您希望運行一種縫合過孔圖案,將兩個GRP連接起來,最大距離為1厘米。

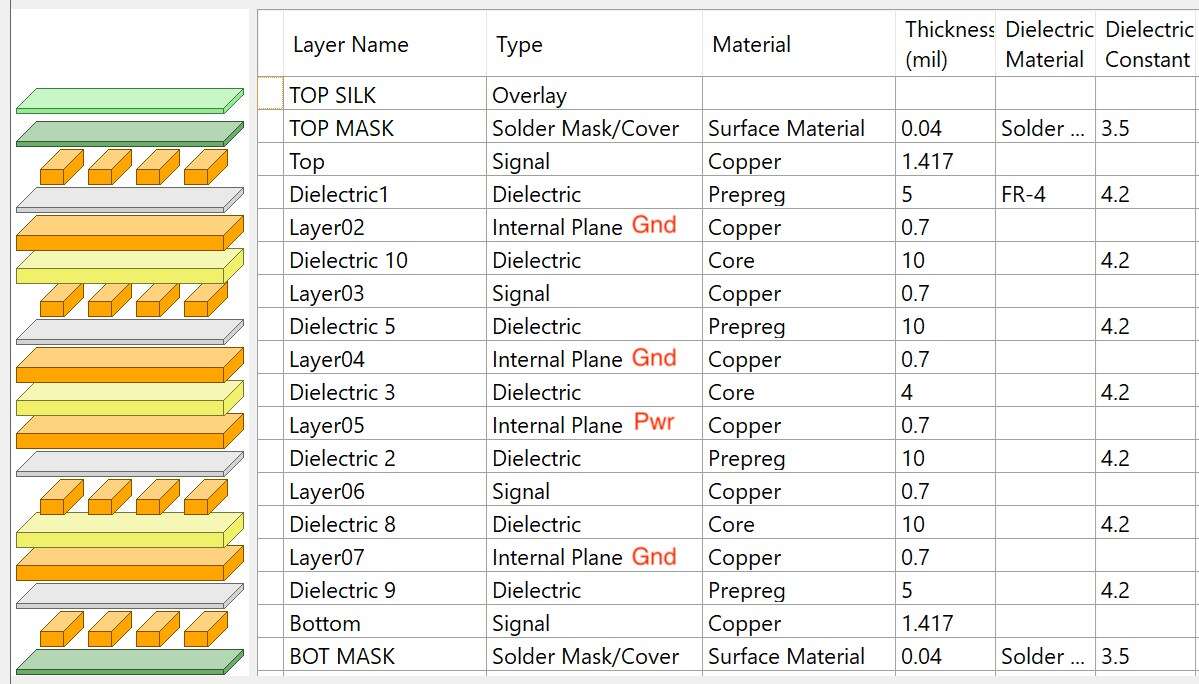

八層板(Altium)

四層和八層板設計(圖4)遵循保持良好傳輸線設計的兩個基本規則。此外,對于八層設計,功率和GRP平面現在相距4密耳,提供相當好的平面到平面電容。更接近甚至會更好。例如,1密耳至3密耳的間隔對于最小化EMI是理想的。所有GRP應與1 cm的過孔圖案拼接在一起。

圖4.良好的EMI疊層設計(8層示例)。所有信號層都參考相鄰的GRP,而功率也參考相鄰的GRP。

當然,在信號和GRP或功率和GRP之間創建正確的傳輸線對還有很多次迭代。

兩層電路板怎么樣?

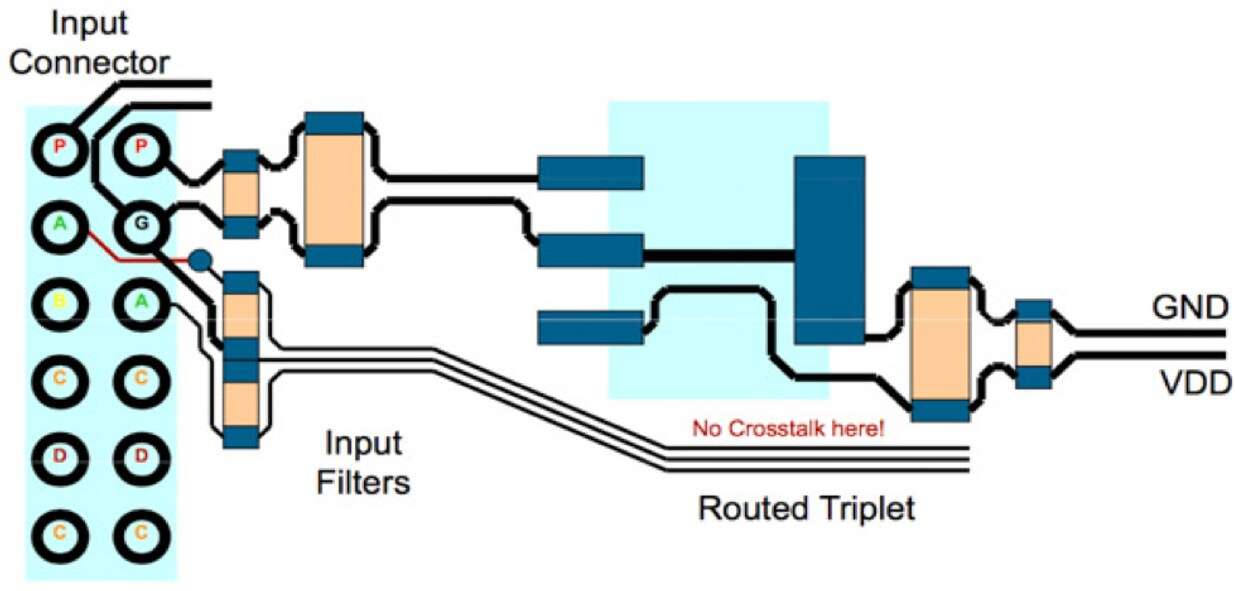

簡單,只需在第1層運行信號和路由電源,并在第2層使用GRP。那么,這可能適用于昨天的技術。在今天的技術中,我們經常需要使用至少兩層來運行信號。答案是在兩條信號走線之間運行“三聯體”和接地回路(圖5)。這是恩智浦半導體高級應用工程師Daniel Beeker的一個想法[參考文獻5]。

圖5.信號路由三元組的示例,以及嘗試保留路由功率的傳輸線原理。禮貌:Daniel Beeker,恩智浦半導體

在這里,我們看到了保護路由功率的傳輸線特性。該示例還顯示了模擬信號跡線,它們之間具有接地返回跡線 - 路由“三重態”。由于在每個信號走線和返回走線之間充分捕獲電磁場,因此幾乎沒有場泄漏。

如果您愿意要了解更多有關在PC板上設計EMI合規性的信息,我還建議Rick Hartley作為他為期2天的研討會的優秀來源(參考文獻6)。最后,我要感謝Ralph Morrison,Dan Beeker和Rick Hartley,他們真正教我電路板中的快速信號[參考文獻3,4,5,6]。

本系列的第3部分將討論電路部分的劃分,高速走線的布線以及一些其他布局實踐,以幫助降低EMI。

-

pcb

+關注

關注

4407文章

23883瀏覽量

424458 -

emi

+關注

關注

54文章

3883瀏覽量

135313 -

可制造性設計

+關注

關注

10文章

2066瀏覽量

16475 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44647 -

華秋DFM

+關注

關注

20文章

3515瀏覽量

6408

發布評論請先 登錄

西門子PCB疊層設計工具Z-planner Enterprise 2510版本的新增功能

疊層固態電容:小型化封裝,釋放PCB更多空間

晶科能源再度實現鈣鈦礦/TOPCon疊層電池轉換效率突破

疊層固態電容的性能優勢

貼片電感代理-疊層電感的實際應用

捷多邦專家解讀:如何選擇最優PCB疊層方案?

HDMI2.0濾波保護疊層共模濾波器介紹

效率超30%!雙面鈣鈦礦/晶硅疊層電池的IBC光柵設計與性能優化

如何設計用于EMI的PCB基本疊層

如何設計用于EMI的PCB基本疊層

評論