EMI工程師應該都能從理論上分析了EMI的產生情況,并主要從系統(tǒng)設計方面考慮很多實際采用的抑制EMI的手段和方式,這里我們將針對高速PCB設計,來分析如何進行EMI控制。

1、傳輸線RLC參數(shù)和EMI

對于PCB板來說,PCB上的每一條走線都可以有用三個基本的分布參數(shù)來對它進行描述,即電阻,電容和電感。在EMI和阻抗的控制中,電感和電容的作用很大。

電容是電路系統(tǒng)存儲系統(tǒng)電能的元件。任何相鄰的兩條傳輸線之間,兩層PCB導電層之間以及電壓層和周圍的地平面之間都可以組成電容。在這些所有的電容中,傳輸線和它的回流電流之間組成的電容數(shù)值最大,也數(shù)量最多,因為任何的傳輸線,它都會在它的周圍通過某種導電物質形成回流。根據(jù)電容的公式:C=εs/(4kπd),他們之間形成的電容的大小和傳輸線到參考平面的距離成反比,和傳輸線的直徑(橫截面積)成正比。我們都知道,如果電容的數(shù)值越大,那么他們之間存儲的電場能量也越多,換句話說,他往外部泄露系統(tǒng)能量的比率將更少,那么這個系統(tǒng)產生的EMI就會得到一定的抑制作用。

電感是電路系統(tǒng)中存儲周圍磁場能量的元件。磁場是由流過導體的電流產生的感生場。電感的數(shù)值表示它存儲導體周圍磁場的能力,如果磁場減弱,感抗就會變小,感抗變大的時候,磁場就會增大,那么對外的磁能量輻射也會變大,即EMI值越大。所以,如果系統(tǒng)的電感越小,那么就能對EMI進行抑制。在低頻情況下,如果導體變短,厚度變大,變寬的時候,導體的電感就會變小,而在高頻情況下,磁場的大小則和導線及其回流構成的閉環(huán)面積的函數(shù),如果把導線與其回路靠近,由于回流和本身電流大小相等(在最佳回流狀態(tài))方向相反,所以兩者產生的磁場就會相互抵消,降低了導體的感應電感,所以,保持導體上電流和其最佳回流路徑,能夠一定程度的減小EMI。

-

pcb

+關注

關注

4405文章

23878瀏覽量

424347 -

emi

+關注

關注

54文章

3882瀏覽量

135277 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44640

發(fā)布評論請先 登錄

淺談晶振在PCB設計中的要點

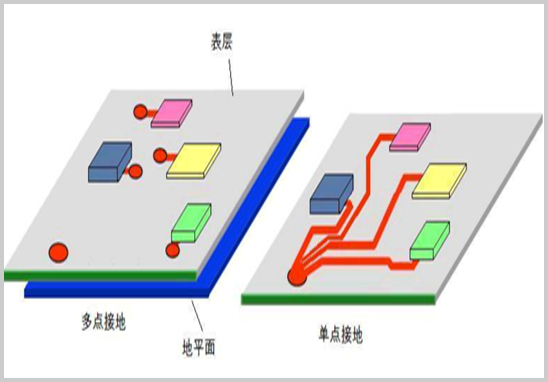

PCB設計中單點接地與多點接地的區(qū)別與設計要點

深度解讀PCB設計布局準則

開關電源的PCB設計

原理圖和PCB設計中的常見錯誤

DDR模塊的PCB設計要點

怎樣控制高速PCB設計中的EMI輻射

怎樣控制高速PCB設計中的EMI輻射

評論