所有大型晶圓代工廠都已宣布FinFET技術為其最先進的工藝。Intel在22 nm節點上采用該晶體管1,TSMC在其16 nm工藝上使用2,而Samsung和GlobalFoundries則將其用于14 nm工藝中3。與所有新工藝一樣,對于IC設計人員來說最重要的問題是“這對我意味著什么?”新的,更小的工藝意味著設計人員將可獲益于更低的功耗、更高的面積利用率以及源自半導體縮放的其他傳統的改善。但除了這些優勢外,還存在著一定的學習成本,以了解新的設計規則、參數差異,以及必須實施才能在新節點進行設計的新方法或改進的方法。目前為止,收益總能證明成本的價值所在。對FinFET來說也是這樣嗎?

與其他所有新技術一樣,FinFET工藝包含一種與學習如何使用其進行設計相關的成本。由于FinFETs是一種完全不同的晶體管,問題變成,這種改變是漸進的(典型學習成本)還是革命性的(顯著學習成本)。答案取決于你的觀點…

漸進

首先要記住的是,對于大多數晶圓代工廠來說,16nm和14 nm的后道工序(BEOL)結構與20 nm節點的一樣。20 nm采用了雙重曝光(DP)4,對設計和制造界產生了極大影響。DP推動了設計流程的變化,是EDA工具在設計、驗證、寄生參數提取和分析方面變化的催化劑。

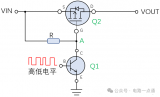

幸運的是,DP的挑戰就發生在最近。三重曝光或多重曝光業已到來,但并非用于現有的FinFET工藝。由于BEOL與20 nm相同,設計人員最需學習并了解前道工序 (FEOL)幾何形狀的變化。圖1是具有單“鰭片”的FinFET器件圖示,當然大部分FinFET器件都有多鰭片。

圖1:單“鰭片”FinFET。

(信息來源:GLOBALFOUNDRIES)

第一次看到這些器件時,大部分設計人員會問以下問題:

1.如何設計?

2.一個器件應包含多少鰭片?

3.鰭片尺寸/間距應該是多少?

4.如何獲取所需信息來了解幾何形狀與電氣性能的折衷方案?

這些都是棘手的問題!通常,設計人員,尤其是數字設計人員,在權衡晶體管結構和電氣性能時將寬度、長度和面積作為參數進行考量。FinFET設計的性質可能極大地改變這一切。幸運的是,大多數晶圓代工廠已考慮到這一點,并為FinFET工藝開發了一種與20nm及以上工藝相同的設計方法。

沒錯,對于這第一代FinFET,設計人員沒有設計/開發鰭片(除非是SRAM設計人員)。如同之前的節點,IC設計人員將會通過定義器件的寬度、長度和面積來設計晶體管。設計、驗證、提取和分析工具將根據晶圓代工廠的規范將版圖分解為鰭片,然后執行必要的分析來進行物理驗證、參數和寄生計算,甚至是執行幾何形狀填充和電路仿真。

通過這些EDA創新,如果你是即將采用FinFET工藝的數字設計人員且最近的節點是20nm,那么FinFETs只不過是一種漸進的變化。BEOL沒有新的內容,物理設計在很大程度上仍舊保持不變,而EDA工具負責執行必要的分析。

革命性

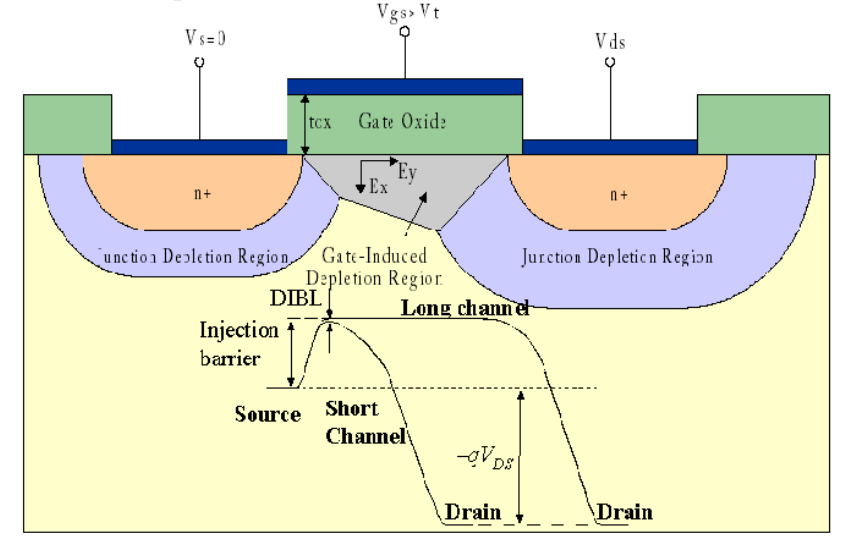

圖2更加真實地描述出了FinFET,用弧形代替了之前示例中的方框和平面。大部分設計人員都同意,預測這種結構的電氣性能需要重大創新。器件及其互連周圍的電場比他們在傳統MOSFET中遇到的要復雜得多。另外,FinFET器件的驅動能力比同樣尺寸的MOSFET更強,這意味著設計人員在預測電氣行為方面將需要更高的精確度。為滿足這些要求,就需要新的技術來進行器件和其互連的建模。

圖2:弧形結構的FinFET圖示(TEM圖片來源:ChipWorks;仿真來源:Gold StandardSimulations Ltd.)

另外,從模擬或IP設計人員的角度來看,上述設計方法(鰭片由晶圓代工廠實施)并非首選模型。這些設計人員希望能獲得更大的自由度,以減少滲漏、匹配驅動能力、提高頻率響應以及推動電氣和幾何限制,而這些都是固定鰭片無法做到的。根據其性質,這種設計是定制的,而無法控制鰭片數量或大小對于其中很多設計人員來說是非常別扭。

對于從28nm或以上工藝跳到FinFET工藝的定制、模擬或IP設計人員來說,這種設計是革命性的,但不一定是字面上的“全新改良”。雖然有工具創新來緩和這種過渡,進行這種設計的方法與其習慣的設計手法相比可能更顯嚴格。采用傳統MOSFET工藝,這些設計人員設計定制化的晶體管包括定制其尺寸和方向。對于FinFET,設計人員將通過更少的變量來達成所需的電氣響應。有人懷疑是否可以通過FinFET 工藝來完成先進的模擬設計,而關于此問題,已經有很多人討論過了。答案是肯定的,但需要對設計方法進行重大改變,且可能需要更多的實驗。

-

電路設計

+關注

關注

6741文章

2702瀏覽量

219516 -

晶圓代工

+關注

關注

6文章

880瀏覽量

49775

發布評論請先 登錄

【書籍評測活動NO.70】全方位的電路設計精進指南《Altium Designer 25 電路設計精進實踐》

IGBT驅動與保護電路設計及 應用電路實例

體硅FinFET和SOI FinFET的差異

【免費工具】華秋AI電路識別助手:讓電路設計與分析變得輕松高效!

如何學好電路設計?(文末分享電路設計資料合集)

關于FinFET技術中的電路設計的分析和介紹

關于FinFET技術中的電路設計的分析和介紹

評論