得益于這兩年資本市場和政策對集成電路產(chǎn)業(yè)的發(fā)展,今年的ISSCC也格外引人關注,最近陸陸續(xù)續(xù)在網(wǎng)上看到了一些大牛對于ISSCC2019上各個領域細分文章的解讀,其中包括了PLL、PA、ADDA、CPU architecture等等,但對于ISSCC上占比很高的一個領域—DCDC電源類,卻始終沒有看到大神出來解讀,可能是電源太基礎太底層,不能向AI, 5G, 人工智能這些風口靠攏,但是也正因為基礎,每個系統(tǒng)都需要電源供電,所以才更多樣化的需求,正好最近囫圇吞棗地看完了這部分的slides,試著基于自己的理解做個總結(jié),希望能起到拋磚引玉的效果。

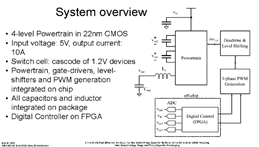

INTEL的文章這篇文章的主要特色是在22nm工藝下實現(xiàn)了高效率低壓大電流的輸出(峰值效率達到了93.8%),通過多級多相位的架構(gòu)選擇,提高了開關頻率,從而提高了load-transient的響應速度,并減小了電感面積,同時采用片上集成電容電感縮減了供電模塊所占面積。

先進工藝下能量傳輸所面臨的挑戰(zhàn)也是在如下幾個方面進行的Trade-off : efficiency <-> size <-> transient response。這篇文章所采用的flyingcapacitor multiple converters結(jié)構(gòu),通過以下特點使DCDC的幾個主要特性參數(shù)得到了優(yōu)化:

1.利用flying cap,在傳統(tǒng)BUCK的基礎上加入兩個FLYING開關電容,構(gòu)成了混合型開拓撲(Hybird topology),并采用三相PWM控制,減少功率傳輸路徑上單個MOS FET的壓降,從而使用低壓器件完成高壓傳輸,低壓器件也節(jié)約了power MOS的面積,減小了Rdson,減小了功率管柵端的寄生電容,提高了效率;

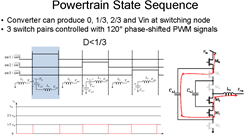

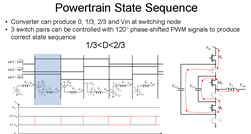

2.兩個FLYING電容,三相PWM控制,SW端就有0, 1/3, 2/3, 1這四種電平的可能性,即三相四電平變換器;

3.4電平傳輸進一步降低了每個功率管的耐壓需求,電路中將每個管子上分擔的輸入電壓除以三,分擔了每個管子上的壓降;

4.6個開關管需要三個相位差為120°的,相同驅(qū)動能力的驅(qū)動信號,等效開關頻率提高至之前的3倍,因此可以有效地減小所需要的電感;

三組PWM驅(qū)動和兩個FLYING電容的結(jié)構(gòu)選擇,使得功率級開關管有多種驅(qū)動控制的組合來獲得更寬的輸出電壓范圍。上面左圖為占空比D<1/3的條件下,6個phase階段開關管M1~M6的導通狀態(tài),由上圖可得,電感左側(cè)SW端的電壓為0~1/3VIN的方波,SW開關頻率為控制開關頻率的3倍。右圖為1/3

仔細分析開關導通過程中開關管分擔的壓降,因為電容上電壓不能突變,所以要實現(xiàn)上圖的效果,需要保證電容Cx1上的電壓為2/3Vin,Cx2上電壓為1/3VIN,不知你們有沒有疑惑,剛開始看的時候我其實很納悶這個值是怎么來的,帶著這個疑惑往下看,就會恍然大悟,這里會涉及多相位開關架構(gòu)的一個關鍵技術—FLYING電容的預充電。當由下圖可得在該方案中,開關switch之前,通過在VBUS上電過程中對其檢測,系統(tǒng)對電容Cx1和Cx2進行了預充電,并且Cx1上電壓為2/3VIN, Cx2上電壓為1/3VIN。當VIN<1/3*5V時,同時對兩個FLYING電容充電,當1/3*5V

結(jié)合上面兩圖試著解讀一下該方案變換器的整體架構(gòu),數(shù)字部分是基于FPGA的數(shù)字控制,個人推測應該是因為預研和驗證采用FPGA比較方便,驗證成功之后應該會將控制部分集成進芯片。其控制思路為,ADC采樣VOUT和VIN計算出當前占空比,再與目標占空比進行比較,如果小于目標占空比,則增大當前占空比d,然后通過DAC轉(zhuǎn)換去調(diào)制DLL的延時,從而生成相位差固定三路驅(qū)動的PWM波形,該波形經(jīng)過level-shift轉(zhuǎn)換后去驅(qū)動開關管SW1~SW6。

該文章的測試結(jié)果可得,其在3A時效率達到了93.8%,得益于高頻和高環(huán)路帶寬,0-6A的瞬態(tài)響應達到了Vpp=150mV。總結(jié)下這種三相位控制的混合拓撲結(jié)構(gòu),從這篇文章來看,優(yōu)勢是頻率更高,因此瞬態(tài)響應和紋波更好,同時用低壓管耐高壓,減小了rds_on,從而提高了效率。同時頻率的提高減小了所需的電感值,該文章采用FCCSP的方案集成了Die、電感、片外電容,進一步減小了模塊在PCB上的面積,提高了集成度。

最后想總結(jié)一下該方案在電路設計時可能會遇到難點,歡迎大家補充:

1.三相位PWM控制信號的產(chǎn)生,DLL環(huán)路對三相信號鎖頻和鎖相的設計;

2.控制信號轉(zhuǎn)為疊管柵端驅(qū)動信號的設計,驅(qū)動電平轉(zhuǎn)換的處理以及時序關系設計;

3. FLYING電容預充電時功率管耐壓處理和時序關系設計;

4.高集成度封裝和散熱之間的trade-off;

5. 占空比變化時不同控制模式切換的過渡處理。

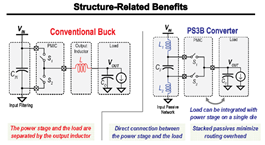

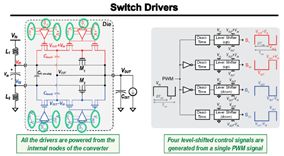

第二篇來自UCSD大學,他們的思路是通過變形的CUK converter架構(gòu)實現(xiàn)高密度的功率集成。即將傳統(tǒng)BUCK變換器的輸出電感分成兩個放在了輸入端,這樣做有如下優(yōu)勢:

1.將電感放在輸入端,利用電感電流不能突變的原理,可以實現(xiàn)輸入電流連續(xù),這樣在開關頻率比較高,功率比較大的時候可以減小輸入濾波器的設計難度,減小片外輸入電容的取值和面積;

2.對于BUCK變換器來說,輸入電流小于輸出端電流,因此相比于輸出電流,輸入電流流過同樣的電感上時由寄生DCR產(chǎn)生的功耗更小;

3.這種架構(gòu)所實現(xiàn)的BUCK變換器在EMI特性、功率密度和效率方面都優(yōu)于傳統(tǒng)的變換器,另外,右二的圖也說明,相比于傳統(tǒng)BUCK,這種變換器把電感放在輸入端,這樣PCB上就只剩下輸入濾波、PMIC、輸出負載這三部分,PCB的布局方面會更有優(yōu)勢。

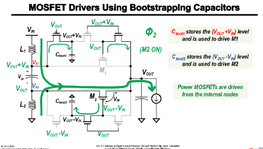

下面結(jié)合上圖的原理圖介紹一下這種架構(gòu)的工作原理,圖中,M1和M2為主功率管,在驅(qū)動相位φ1期間,M1的gate端為VOUT+VIN,M2的gate端為VOUT,M1導通,M2截止,輸入電壓將電容CIN兩端電壓充至VIN,CBOOT2兩端的電壓被充至VOUT-VIN,使其可以在φ2驅(qū)動M2導通;在φ2期間,M1的gate端為VOUT,M2的gate端為VOUT-VIN,M1截止,M2導通,輸入電容CIN的上極板電壓VX1的電位為VOUT+VIN,因此會將電容CBOOT1上電壓充至VOUT+VIN,使其可以在φ1驅(qū)動M1導通。

但從這一頁的原理圖來說,個人認為有如下難點:

1.高端驅(qū)動和低端驅(qū)動的電源軌都不固定,需要特別去考慮和設計驅(qū)動信號的電平轉(zhuǎn)換;

2.用VIN-VOUT驅(qū)動源端為VOUT的PMOS管,就決定了其占空比不能太大,文章采用的0.18um工藝,文章后面的summary里面總結(jié)可以在VIN=1.8V的條件下輸入0.5V~1.5V,這一點我持懷疑態(tài)度,除非在電路中做了特殊的設計;

3.驅(qū)動電路中需要大量的隔離器件,因此在LAYOUT的時候要慎重考慮latch up、noise方面的影響。

總體而言,這篇文章是本次ISSCC會議上DC-DC session里極具創(chuàng)新的一篇文章,不同于INTEL那篇,這篇文章在0.18um的工藝下實現(xiàn),同時給出了功率管驅(qū)動耐壓和驅(qū)動電平轉(zhuǎn)換的解決方案,并且也從工業(yè)界的應用角度考慮了將BUCK的輸出電感拆分成兩個放在輸入端對于PMU整體面積和效率產(chǎn)生的影響和對比。相比于今年來比較火的10mA~100mA功率段的SC converter,這篇文章給出了大電流下(2.5A)高功率密度集成的PMU解決方案,未來應該會有很廣闊的應用市場。

ADI的文章第三篇想介紹的是來自ADI的一篇文章。近幾年來,隨著汽車充電器和移動電源的市場越來越大,BUCK-BOOST架構(gòu)的升降壓電源在業(yè)界應用變得很火。

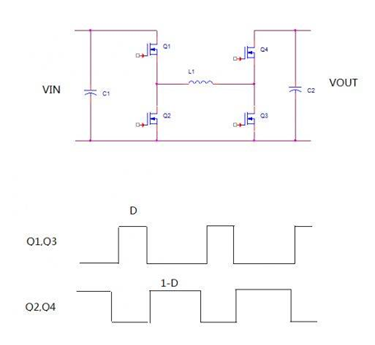

傳統(tǒng)的四開關Buck-Boost電路,Vo=Vin*D/(1-D),輸出電壓的極性與輸入電壓相同。如下圖,

如上圖所示,Q1和Q3同時工作,Q2和Q4同時工作,并且兩組MOS交替導通。對于這種控制方式,在CCM情況下我們可以得到公式:

VIN×D=VOUT ×(1-D)

這個電壓轉(zhuǎn)換比和我們常見的buck-boost是一樣的,這種控制方式的優(yōu)點是控制方式簡單,沒有模態(tài)切換。但是缺點是,四個管子都在一直工作,損耗大,共模噪音也大。

ADI的這篇文章就是針對傳統(tǒng)BUCK-BOOST四個開關管輪流導通共模噪聲大的痛點,提出了更優(yōu)的控制方式和模式切換方案。

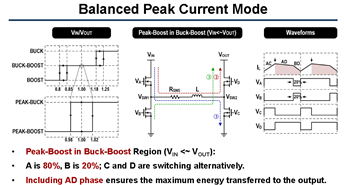

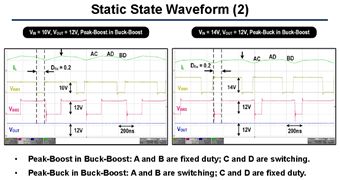

其思路就是當Vin>>Vout的時候,SC管常關,SD管常開,把這個拓撲當純粹的BUCK來用,當Vin<

本文的思路是,在VIN>>VOUT,即BUCK工作模式下,當VOUT逐漸升高,占空比逐漸增大至80%時,VIN≥VOUT,開關管SC和SD不再常開或者常關,其也會導通從而切換至BOOST/BUCK模式,即前半周期為BOOST模式,后半周期為BUCK模式。同理,在VIN<

不知道大家有沒有這樣的疑問?在占空比比較接近時芯片還是工作在BUCK-BOOST模式,那么是不是在這種條件下,共模噪聲的問題就不會有很大改善?這個問題我是這么理解的,如果全程在BUCK-BOOST模式下,四個開關管SA/SC,SB/SD輪流導通,那么電感兩端在整個周期內(nèi)的都有VIN/VOUT的電壓差,會產(chǎn)生較大的dv/dt干擾,如果采用這篇文章所提的控制模式,那么芯片控制方式在BUCK和BOOST之間切換,其EMI特性與單獨的BUCK芯片或BOOST芯片接近,產(chǎn)生的EMI干擾會遠遠小于BUCK-BOOST的工作模式。

本次會議DC-DCconverters部分收錄了8篇文章,總體的發(fā)展趨勢是向著高效率,高能量密度的方向,各路大神對于新的拓撲架構(gòu)進行了的多樣化探索。特別可以看出,對于大功率的應用,混合型(Hybrid)拓撲在效率方面更具有優(yōu)勢,而對于中小型功率(Io=10mA~100mA)的需求,SC Converter因為其高能量密度(PD)的特點,得到了學術界的火熱探索。個人認為,之后DC-DC Converter領域內(nèi),不會再像之前那樣,被電壓模/電流模拓撲一統(tǒng)天下,而是會根據(jù)應用的不同,在架構(gòu)方面出現(xiàn)百花爭艷的局面,之前的DC-DC 在trade-off設計時可能做到?jīng)]有短板就行了,而之后的設計,更多的是在此基礎上對個別進行極限的挑戰(zhàn)。比如低噪聲、低EMI、高效率、高能量密度、快速瞬態(tài)響應、高PSRR等待,每一個性能可能都需要從架構(gòu)上做優(yōu)化。這里面的挑戰(zhàn)和樂趣可能會顛覆很多人對于DC-DC Converter門檻低、架構(gòu)固化、新的挑戰(zhàn)少的觀點。所以,不管在企業(yè)做產(chǎn)品還是在高校做學術研究,還是有很多東西可以做的。

因為最近太懶工作太忙,將這8篇囫圇吞棗地過了一遍之后,挑了自己覺得比較精彩的三篇做個簡單分享,其中可能有很多不妥或者考慮不夠深入之處,歡迎各位同仁拍磚過來一起探討。

-

電路

+關注

關注

173文章

6076瀏覽量

178403 -

MOS

+關注

關注

32文章

1741瀏覽量

100720 -

Buck-Boost

+關注

關注

5文章

80瀏覽量

20516

原文標題:ISSCC2019 DC-DC converter淺析

文章出處:【微信號:yaliDV,微信公眾號:模擬混合信號設計驗證】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

聯(lián)電宣布22nm技術就緒

透視IVB核芯 22nm工藝3D技術終極揭秘

功率和成本減半 Achronix交付先進22nm Speedster22i 系列FPGAs

22nm平面工藝流程介紹

銳成芯微宣布在22nm工藝上推出雙模藍牙射頻IP

Intel 22nm光刻工藝背后的故事

臺積電又跳過22nm工藝 改而直上20nm

Arasan宣布用于臺積公司22nm工藝技術的eMMC PHY IP立即可用

北斗22nm芯片用途是什么?

22nm和28nm芯片性能差異

22nm芯片應用在哪些地方?

22nm芯片是什么年代的技術?

北斗22nm芯片用途

旋極星源基于22nm工藝完成關鍵IP發(fā)布與驗證

22nm工藝下如何實現(xiàn)高效率低壓大電流輸出

22nm工藝下如何實現(xiàn)高效率低壓大電流輸出

評論