賽靈思 Zynq-7000 All Programmable SoC 系列代表了嵌入式設計的新局面,為嵌入式系統工程設計群體帶來前所未有的高性能和靈活性。這些產品在單個器件上集成了特性豐富的雙核 ARM Cortex-A9 MPCore 處理系統和賽靈思可編程邏輯。3,000 多個互聯點將片上處理系統 (PS) 與片上可編程邏輯 (PL) 相連,使兩個片上系統之間的性能達到了任何雙芯片處理器 FPGA 都無法匹敵的高度。賽靈思在 2011 年發布這款 Zynq SoC 器件時,便立即得到了很多精通硬件設計語言和方法以及嵌入式軟件開發的嵌入式系統工程師和架構師的追捧。如今,首款 Zynq SoC 已被用于無線基礎設施、智能工廠和智能視頻/視覺等多種嵌入式應用領域,并且快速成為高級駕駛員輔助系統約定俗成的標準平臺。

為了讓這款性能卓越的器件能夠被具有很強軟件背景但沒有 HDL 經驗的嵌入式工程師所用,賽靈思在今年年初推出了基于 Eclipse 的 SDSoC 集成開發環境,使軟件工程師能夠對 Zynq SoC 中的可編程邏輯和 ARM 處理系統進行編程。

我們仔細了解一下 Zynq SoC [1] 的特性以及軟件工程師如何利用 SDSoC 環境來創建用任何其他“處理器+FPGA”系統均無法實現的系統設計。為進行研究,我們將使用包含一個 Zynq Z-7020-1 器件的賽靈思 ZC702 評估板 [2] 作為硬件平臺。

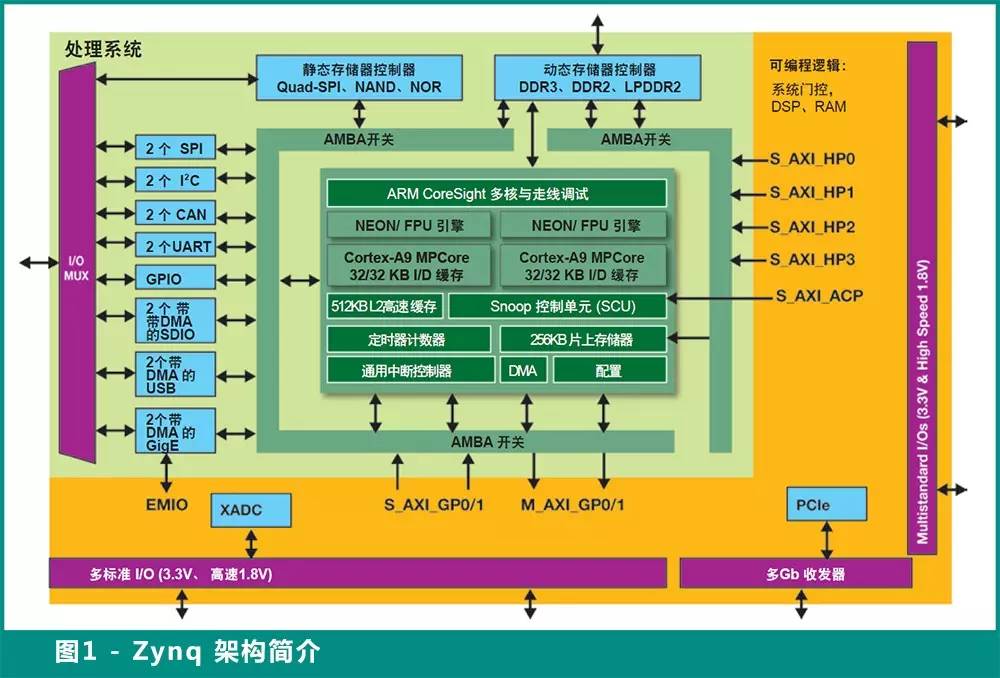

如圖 1 所示,Zynq SoC 包含兩大功能模塊:PS(包含應用處理器單元、存儲器接口、外設和互聯)和 PL(傳統的 FPGA 架構)。

PS 和 PL 通過與 ARM AMBA AXI4 接口兼容的互聯鏈路緊密耦合在一起。四個高性能 (HP) AXI4 接口端口將 PL 連接到 PS 中的異步 FIFO 接口 (AFI) 模塊,從而在 PL和 PS 存儲器系統(DDR 和片上存儲器)之間提供一條高吞吐量的數據路徑。AXI4 加速器一致性端口 (ACP) 允許直接從 PL 主設備對 L1 和 L2 高速緩存進行低時延的一致性訪問。通用 (GP) 端口包含可從 PS 和 PL 訪問的低性能通用端口。

在傳統的以硬件設計為核心的流程中,通過使用賽靈思的 Vivado Design Suite 在 Zynq SoC 上設計嵌入式系統大致需要四個步驟:

系統架構師確定硬件-軟件分區方案。計算密集型算法最適合硬件。特性分析結果是鑒別性能瓶頸以及在數據移動成本與加速優勢之間進行權衡研究的基礎。

硬件工程師處理被分到硬件中的功能,并將它們轉換或設計成 IP 核,例如,用 Vivado 取代 VHDL 或 Verilog ;用 Vivado 高層次綜合 (HLS) 實現 C/C++ 高層次綜合[3],或者用 Vivado System Generator for DSP 實現模型化設計 [4]。

然后,工程師使用 Vivado IP Integrator [5]創建整個嵌入式系統的模塊化設計。整個系統的開發需要用到不同的數據移動工具(AXI-DMA、AXI Memory Master、AXI-FIFO 等),以及連接 PL IP 與 PS 的AXI 接口(GP、HP 和 ACP)。一旦 IP Integrator 中所有設計規則檢查都通過,就可將項目導出至賽靈思軟件開發套件 (SDK) [6]。

軟件工程師使用賽靈思 SDK 開發針對 PS 中 ARM處理器的驅動程序和應用。

最近幾年,賽靈思對 Vivado Design Suite 的簡便易用性實現了顯著提高,該套件能夠讓工程師縮短 IP 開發時間以及 IP 模塊連接步驟(上述步驟 2 以及步驟 3 的部分內容)。就 IP 開發而言,采用這些最新設計技術(例如在 Vivado HLS 工具中實現 C/C++ 高層次綜合;用 Vivado System Generator for DSP 實現模型化設計)可以顯著縮短開發和驗證時間,同時讓設計團隊能夠使用高層次抽象探索更大的架構范圍。對于使用 VHDL 或 Verilog 需要數周才能完成的設計,利用新型工具只需數天就能完成。

SDSoC 環境會自動安排所有必要的賽靈思工具,以生成針對 Zynq SoC 的完整軟硬件系統,而且所需的用戶介入程度很小。

賽靈思通過 Vivado IP Integrator 可進一步強化流程。Vivado Design Suite 的這個功能使設計人員只需要在圖形用戶界面 (GUI) 中連接 IP 模塊,就可以設計復雜的硬件系統(嵌入式或非嵌入式),從而實現快速的硬件系統集成。

新的 Vivado Design Suite 功能可幫助設計與開發團隊簡化 Zynq SoC 的使用。但對于以硬件為中心的優化流程而言,要縮短探索不同數據移動工具和 PS-PL接口(步驟 3 的一部分)以及寫入和調試驅動程序與應用(步驟 4)所需的開發時間,辦法并不多。如果整個系統不能滿足吞吐量、時延或占位面積等方面的設計要求,那么設計團隊不得不修改步驟 3 中的系統連接,以重構硬件架構。這些修改會不可避免地導致步驟 4 中的軟件應用發生變化。有些情況下,加速不足或者硬件利用率過高會迫使開發團隊重新考慮最初的軟硬件分區。多個硬件和軟件團隊將不得不再次反復設計系統,以探索可能滿足最終要求的其他架構。

這些實例表明手動進行系統優化對上市時間的影響。系統優化對于緊密集成的系統(例如 Zynq SoC)很關鍵,因為瓶頸經常發生在 PS 與 PL 之間的系統連接上。

SDSoC 環境能大大簡化 Zynq SoC 開發過程,可將步驟 2、3、4 實現高度自動化,以縮短總開發時間。該開發環境會生成必要的硬件和軟件組件,用以同步硬件和軟件并保存源程序語義,同時支持任務級并行處理和流水線化的通信與計算,從而實現高性能。SDSoC 環境會自動安排所有必要的賽靈思工具(Vivado、IP Integrator、HLS 和 SDK),以生成針對Zynq SoC 的完整軟硬件系統,而且所需的用戶介入程度很小。

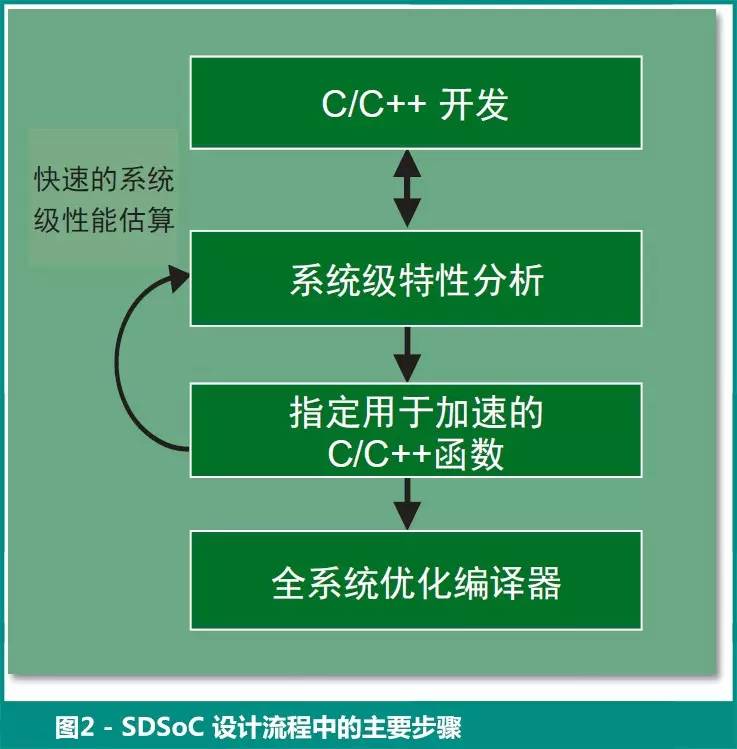

假設我們已有一個針對 PS 的完全用 C/C++ 描述的應用,而且已經決定將哪些功能分配到 PL 以實現加速,那么 SDSoC 開發流程大致按照如下所示(圖2):

SDSoC 環境使用快速估算流程(通過調用內含的Vivado HLS)構建應用項目。這樣在數分鐘內就能大致估算出性能和資源情況。

如果我們認為有必要,我們會用適當的指令優化 C/C++ 應用和硬件功能,并重新運行估算直到實現所需的性能和占位面積。

然后,SDSoC 環境構建整個系統。該過程會生成完整的 Vivado Design Suite 項目和比特流,以及一個針對 Linux、FreeRTOS 或裸機的可引導的運行時間軟件映像。

用 SDSOC 環境進行硬件 VS 軟件的性能估算

線性代數幾乎在任何工程領域中都是基礎而強大的工具,能夠計算求解具有多維變量的方程組。例如,工程師可將線性控制理論系統描述為“狀態”和“狀態變換”矩陣。圖像的數字信號處理是線性代數的另一個典型應用。尤其是,通過 Cholesky 分解進行矩陣求逆被認為是求解方程組或矩陣求逆的最有效的方法之一。現在讓我們仔細看一看 32 位浮點實際數據 64 x 64 矩陣的 Cholesky 分解,并作為 Zynq SoC 上軟硬件分區的應用實例。

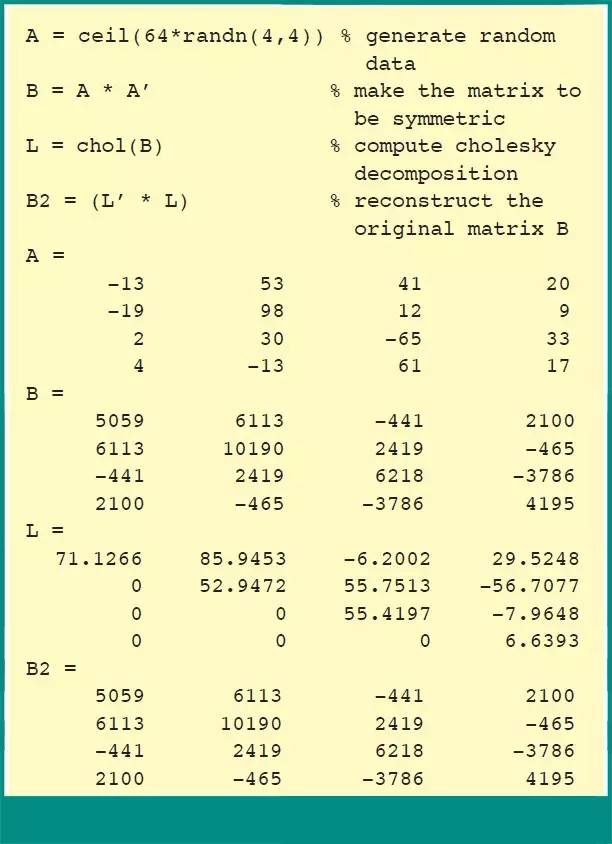

Cholesky 分解將正定矩陣變換為具有嚴格正對角線的下三角和上三角矩陣的乘積。矩陣 B 在三角矩陣 L 中分解,即 B = L’ * L,其中 L’ 是 L 的轉置矩陣,如下面的 4 x 4 矩陣 MATLAB 代碼所示:

選擇加速器很簡單,只需在 SDSoC 環境的圖形用戶界面 (GUI) 中用鼠標點擊特定功能即可。

讓我們看看如何估算應用設計的性能和資源利用率,而且無需經過整個構建周期。

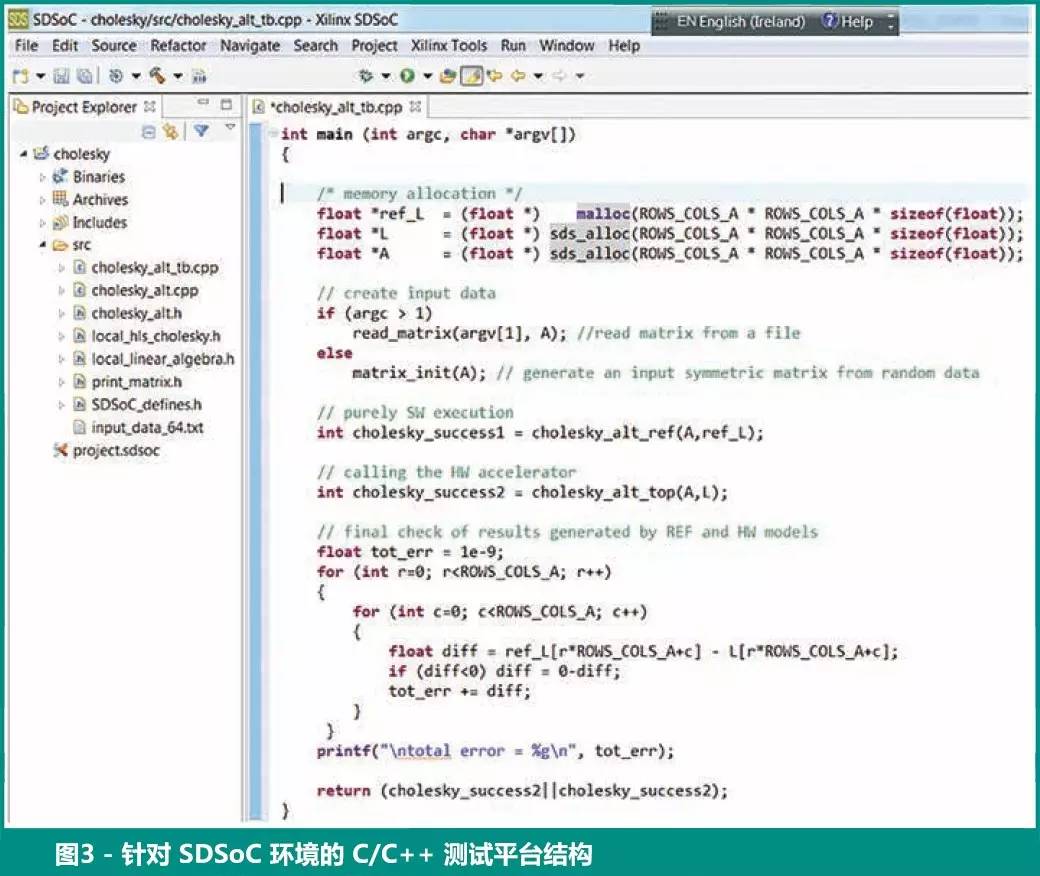

圖 3 給出了適合 SDSoC 環境的測試平臺結構。主程序為所有空矩陣分配動態存儲器并填入數據(從文件中讀入或者隨機生成)。然后,主程序調用參考軟件函數和硬件備選函數。最后,主程序檢查兩個函數計算出的數值結果以測試有效正確性。

注意,這里針對每個輸入/輸出數組使用了一個名為sds_alloc 的專用存儲分配器,以讓 SDSoC 環境自動在硬件加速器的每個 I/O 端口之間插入一個 Simple DMA IP;相比之下,malloc 則實例化一個 Scatter-Gather DMA,用以處理分布在物理地址空間中多個非連續頁面上的數組。Simple DMA 從占位面積和性能開銷上將要比 Scatter-Gather DMA 廉價,但需要 sds_alloc 獲得物理上的連續存儲空間。

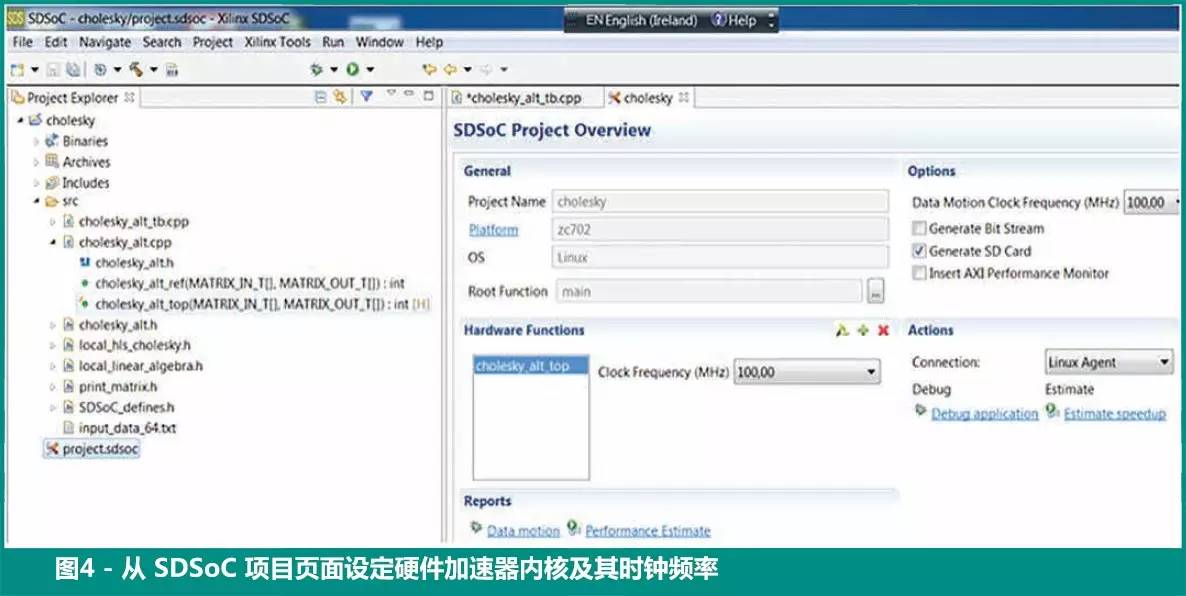

選擇加速器很簡單,只需在 SDSoC 環境的圖形用戶界面 (GUI) 中用鼠標點擊特定功能即可。如圖 4 所示,例程 cholesky_alt_top 標記為 “H”,以表明它將被送到硬件加速器。我們還可以為加速器和數據移動內核選擇時鐘頻率(如圖 4 的 SDSoC 項目頁面中所示為 100 MHz)。

現在,我們可以啟動“估算加速”過程。在經過幾分鐘的編譯后,我們就可以在 Vivado 項目中生成所有內核和數據移動網絡。SDSoC 環境還生成一個 SD 卡映像,其中包含 Linux 引導映像,里面有 FPGA 比特流以及純軟件版本的二進制應用程序。我們從這個 SD卡引導,并在 ZC702 目標平臺上運行應用。

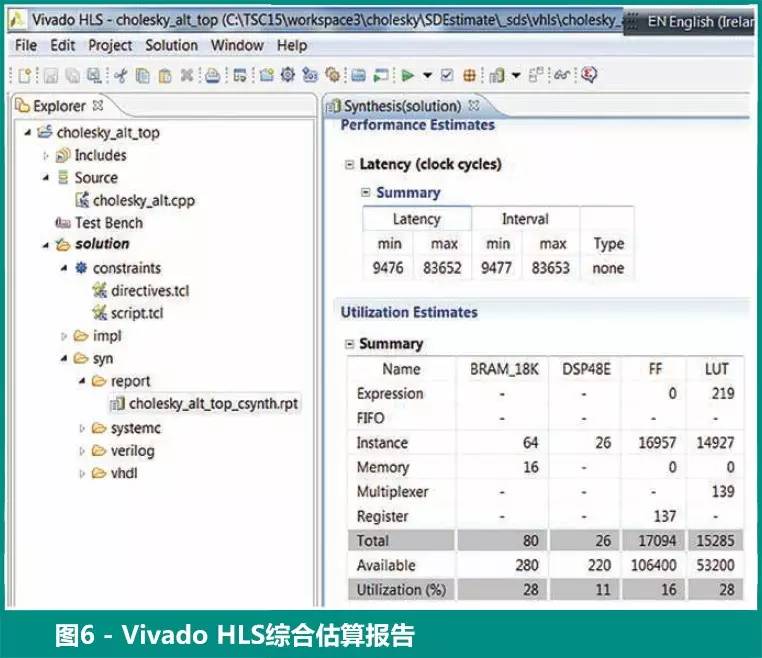

Linux 在開發板上啟動之后,我們可執行純軟件應用,然后,SDSoC 環境生成圖 5 中的性能估算報告。如果在硬件中而非軟件中執行,我們可看到 cholesky_alt_top 函數的 FPGA 資源利用率 (26 DSP、80 BRAM、 15,285 LUT、17,094 FF) 和性能加速 (1.75)。

在主應用程序方面,我們還可以看到總體加速比較低 (1.23),原因在于其他軟件開銷,例如 malloc 和數據傳輸。我們的整個應用比較小,主要在于展示 SDSoC 流程和設計方法;我們需要在 PL 中加速更多例程,但這超出了本文的范疇。

使用 SDSoC 環境,只要幾分鐘就能生成該信息,且無需綜合和布局布線這樣的 FPGA 編譯過程;這些過程根據硬件系統的復雜程度可能需要數小時才能完成。這樣的估算通常足以用來分析硬件-軟件分區的系統級性能,并讓用戶能夠迅速進行設計迭代以創建出最佳系統。

了解性能估算結果

當 SDSoC 開發環境針對估算加速進程編譯應用代碼時,會生成一個中間目錄 (圖 5 中的_sds),用來放置所有中間項目(Vivado HLS、Vivado IP Integrator 等)。它會特別在源代碼中插入對自由運行的 ARM 性能計數器函數 sds_clock_counter() 的調用,以測量程序函數中關鍵部分的執行時間。這也就是為什么目標板需要在估算加速進程中與SDSoC 環境的 GUI 連接。圖 5 中報告的所有數字都在運行執行過程中用這些計數器測量得到。唯一的例外是硬件加速函數,該函數直到整個 FPGA 構建(包括布局布線)完成后才存在。不過,Vivado HLS 會在有效 Vivado HLS 的綜合步驟過程中在估算資源利用率的同時計算硬件加速函數的估算周期數。

假設備選硬件加速器函數以 FHW MHz 時鐘頻率運行,并需要 CKHW 個時鐘周期完成整個計算(這是時延概念),并且假設在 ARM CPU 執行時,函數在 FARM MHz 時鐘頻率下占用 CKARM 個周期,那么,如果計算時間相同,硬件加速器就能實現與 ARM CPU 相同的性能,即 CKHW / FHW= CKARM / FARM。從這個公式中我們得到 CKARM = CKHW*FARM / FHW。這代表加速器能為處理器分擔的最大時鐘周期數量,以展示將函數遷移到硬件而獲得的加速效果。

圖 6 中報告了 Vivado HLS 綜合估算結果。注意,硬件加速器時延為 CKHW = 83,652 個周期,時鐘頻率 FHW = 100-MHz。在 ZC702板 中,FARM = 666 MHz,而且 CKARM = CKHW*FARM / FHW = 83,653*666/100 = 557,128,獲得的硬件加速效果與圖 5 中 SDSoC 環境報告的 565,554 個周期達到了很好的匹配。這就是為什么 SDSoC 環境能估算加速器所需的時鐘周期數量而又不需要進行實際的布局布線。

用 SDSOC 環境構建硬件-軟件系統

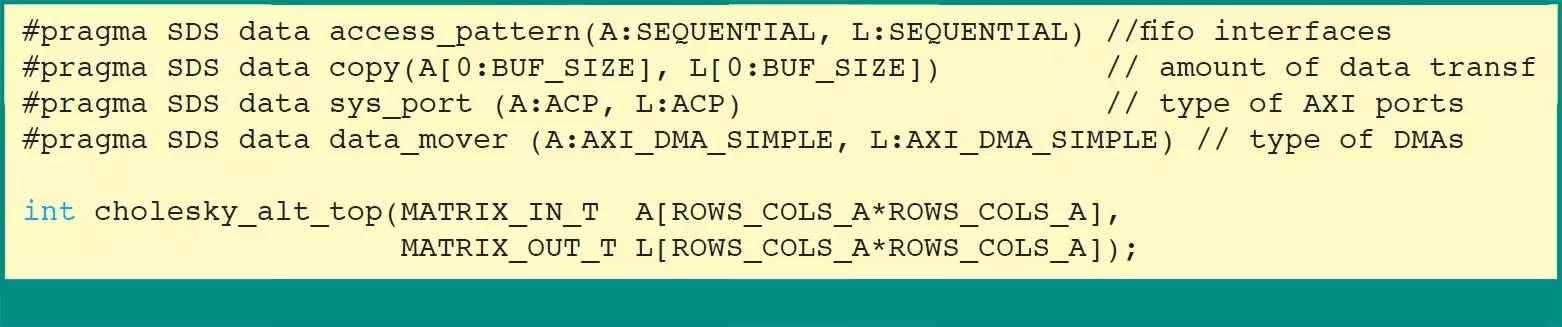

在確定硬件加速有效果之后,我們可以用 SDSoC 環境實現整個硬件和軟件系統。我們需要做的是添加正確的指令(以 Pragma 命令的形式)來分別指定 FIFO 接口(由于 I/O 陣列的連續掃描);在運行時針對任何加速器調用而需傳送的數據量;連接 PL 中的 IP 核與 PS 的 AXI 端口類型;以及數據移動工具的類型。下面的 C/C++ 代碼表明了這些指令的使用。注意,實際情況下最后的指令不需要,原因是 SDSoC 環境會因 sds_alloc 的使用而實例化一個 Simple DMA;我們在這里提到它只是為了說清楚。

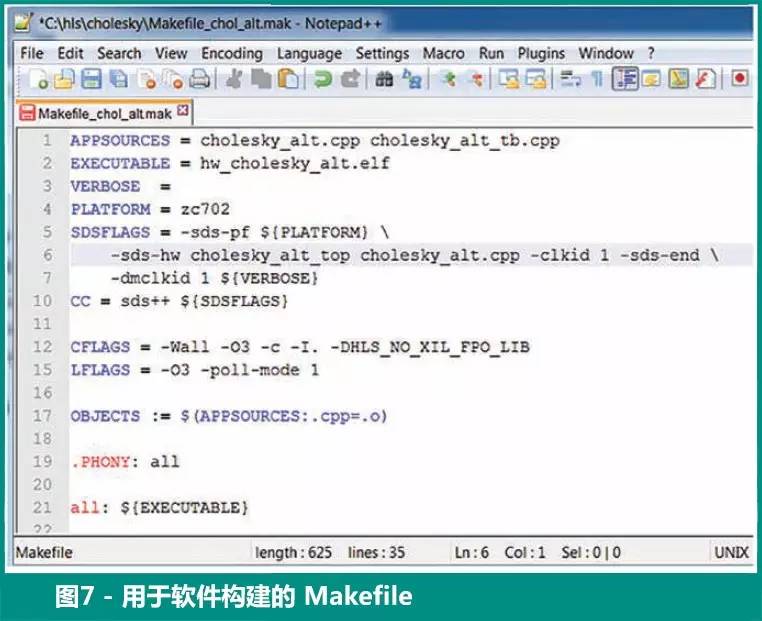

我們可以在 SDSoC 環境的 GUI 中直接在 Release 配置中構建項目,或者,也可使用圖 7 中的 Makefile 并從 SDSoC 工具命令語言 (Tcl) 解釋器中啟動。不管是Vivado Design Suite 中的什么工具,設計人員都可以采用 GUI 或 Tcl 腳本。為了提高加速效果,我們將硬件加速器的時鐘頻率增加至 FHW =142 MHz(通過-clkid 1 makefile 標志設置)。

FPGA 編譯完成后不到半個小時,我們就得到對ZC702 板進行編程的比特流以及在 Linux OS 上執行的可執行連接文件 (ELF) 格式文件。然后,我們在ZC702 板上測量性能:純軟件時是 995,592 個周期,有硬件加速時是 402,529 個周期。因此,cholesky_alt_top 函數的有效性能提升 2.47。

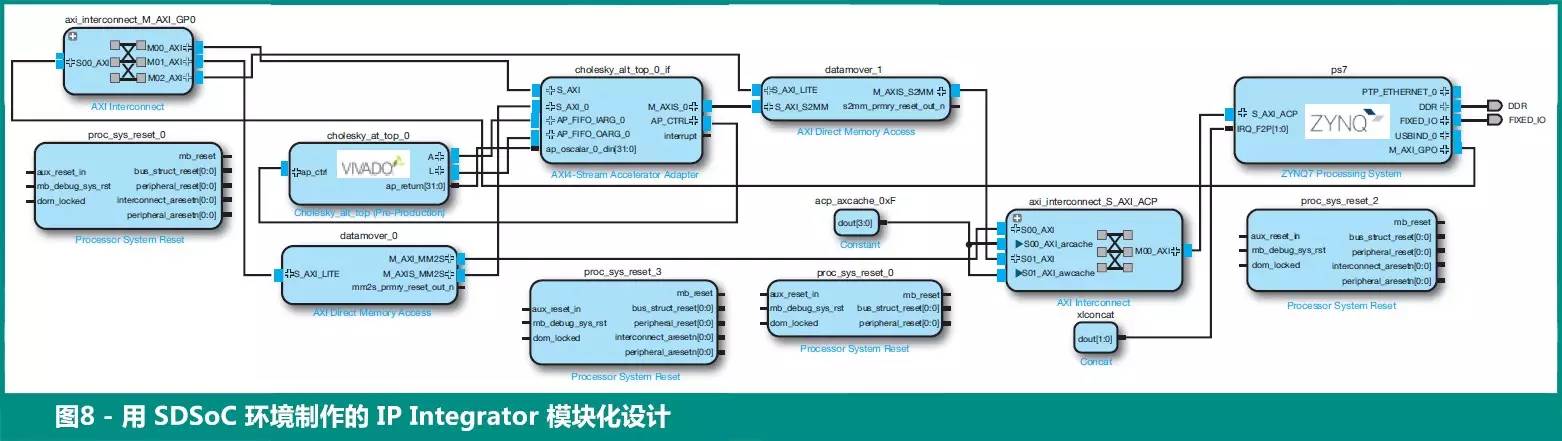

圖 8 給出了整個嵌入式系統的方框圖;SDSoC 環境將 Vivado IP Integrator 方框圖以 HTML 文件報告的形式給出,以使其易于閱讀(圖 9)。該報告清楚顯示,硬件加速器通過簡單 AXI4-DMA 連接 ACP 端口,而通用端口用來通過 AXI4-Lite 接口設置加速器。

在嵌入式系統啟動并運行時,我們需要花多長時間為 ZC702 板生成 SD 卡?我們需要一個工作日來編寫適合 Vivado HLS 和 SDSoC 環境的 C++ 測試平臺,然后,用一個小時進行實驗以從 Linear Algebra HLS Library 中獲得好的結果,再用一個小時的時間通過SDSoC 環境創建嵌入式系統(FPGA 編譯過程)。這個過程共需要 10 個小時。我們估算手動完成所有這些工作(步驟 3 用 Vivado IP Integrator,步驟 4 用賽靈思SDK)至少需要兩周的辛苦工作,這還不算高效使用這些工具所需的時間。

FPGA 編譯完成后不到半個小時,我們就得到對 ZC702 板進行編程的比特流以及在 Linux OS 上執行的 ELF 格式文件。

SDSoC 開發環境使更多嵌入式系統和軟件開發人員能夠憑借熟悉的嵌入式 C/C++ 開發經驗針對 Zynq SoC 開展工作。包括業界首款 C/C++ 全系統優化編譯器的 SDSoC 環境提供系統級特性分析、可編程邏輯中的自動軟件加速、自動系統連接生成和庫,以加快開發速度。

-

嵌入式系統

+關注

關注

41文章

3747瀏覽量

133640 -

加速器

+關注

關注

2文章

839瀏覽量

40106 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133435

發布評論請先 登錄

探索PCM510xA系列音頻DAC:高性能與靈活性的完美結合

探索PCM510xA系列音頻DAC:高性能與靈活性的完美結合

探索PCM510xA系列音頻DAC:高性能與靈活性的完美結合

德州儀器PCM186x音頻ADC:高性能與靈活性的完美結合

探索PCM186x系列音頻ADC:高性能與靈活性的完美結合

探索PCM186x-Q1音頻ADC:高性能與靈活性的完美結合

TLV320ADC3140音頻ADC:高性能與靈活性的完美結合

TLV320ADC5120音頻ADC:高性能與靈活性的完美結合

TAA3020音頻ADC:高性能與靈活性的完美結合

通過高性能MCU與集成外設破解現代嵌入式設計難題

探索XMC7000工業微控制器:高性能與靈活性的完美結合

探索AMD Kria K24 SOM:高性能嵌入式平臺的卓越之選

嵌入式和FPGA的區別

瑞芯微RK3288解決方案:高性能、高擴展性的嵌入式系統設計理念與應用分析

賽靈思系列為嵌入式系統工程設計群體帶來高性能和靈活性

賽靈思系列為嵌入式系統工程設計群體帶來高性能和靈活性

評論