摘要:針對E2V公司的高速ADC芯片EV10AQ190,提出了一種高速ADC接口電路設計方案。首先簡要介紹了高速ADC芯片EV10AQ190技術特點,然后重點敘述了影響高速ADC接口電路性能的兩大關鍵技術:FPGA片同步技術和多路ADC校正技術,最后給出了硬件調試及實驗結果。實驗結果表明,該高速ADC接口電路采樣率可穩定工作在4GHz以上。這種方案已成功應用到某寬帶雷達回波模擬系統的設計中。

隨著電子通信行業的高速發展,越來越多的應用都要求更高的速率和更大的帶寬,高速模數轉換(ADC)芯片的采樣率已經從以前的MHz級發展到當前的GHz級。伴隨著信號采樣率的不斷提高,信號偏斜(SKEW)、抖動和噪聲都在吞噬著時序余量,如何在高速系統中進行穩定、可靠的采樣和數據變換將面臨極大的挑戰。

高速ADC電路設計一直是電子通信領域的研究熱點。

文獻[1]給出了一種基于FPGA片同步技術的高速ADC接口電路設計方法。

文獻[5]利用E2V公司ADC芯片EV8AQ160實現了雙通道2.5Gsample/s信號的采集。

文獻[6]介紹了利用FPGA通過SPI協議對ADC芯片ADC083000進行配置的方法,實現了3Gsample/s數據采樣。

文獻[7-8]講述了如何利用FPGA來設計多通道高速ADC采樣控制器。

文獻[9-10]分別介紹了高速ADC電路的設計方法和PCB設計要點。

公司ADC芯片EV10AQ190實現了一種高速ADC接口電路,信號采樣率高達4Gsample/s。EV10AQ190是E2V公司的一款高速ADC芯片,具有10bit分辨率,最高采樣率可達5GHz。在如此高速的ADC接口設計中,時鐘和數據穩定的相位關系、同步性能的好壞將直接影響信號采集的質量,必須采用源同步技術,保證采樣時鐘和數據嚴格同步、時序關系穩定。此外,對于高速ADC芯片EV10AQ190,內部集成了多路ADC,通過采用多通道ADC交錯采樣拼接技術來獲得更高采集變換速率。因此,多個通道ADC輸出幅度、相位、直流偏置是否一致將直接影響采樣拼接后的高速ADC輸出信號質量,高速ADC接口電路設計時必須對EV10AQ190芯片內部4路ADC進行幅相一致性校正。

本文提出了一種基于片同步(CHIPSYNC)技術的高速ADC接口電路設計方案,利用XILINX公司Virtex-6系列FPGA完成了高速ADC接口設計,實現了采樣時鐘和數據的動態相位調整,確保了高速ADC的穩定、可靠工作。同時,采用了多路校正技

術對芯片EV10AQ190內部4路ADC的偏置(Offset)、增益(Gain)、相位(Phase)進行校正,保證多通道ADC輸出的幅相一致性,確保高速ADC的動態性能指標滿足設計要求。

1 高速ADC 器件EV10AQ190EV10AQ190是E2V公司的一款低功耗、高性能模數轉換芯片,片內集成了4路1.25GHz采樣率、10bit分辨率ADC,輸出為LVDS標準電平,可以工作在單通道、雙通道、四通道3種模式,最高采樣率可達5GHz。EV10AQ190內部集成了1∶1和1∶2的數據多路分離器(DMUX)和LVDS輸出緩沖器,可以降低輸出數據率,方便與多種類型的高速FPGA直接相連,實現高速率的數據存儲和處理。為了補償由于器件參數離散和傳輸路徑差異所造成的采樣數據誤差,該ADC具有針對每路ADC數據的增益、偏置、相位的控制和校正。EV10AQ190提供測試和自檢功能,方便用戶根據自己的習慣對ADC是否正常工作進行測試和對時序是否對齊進行調試。

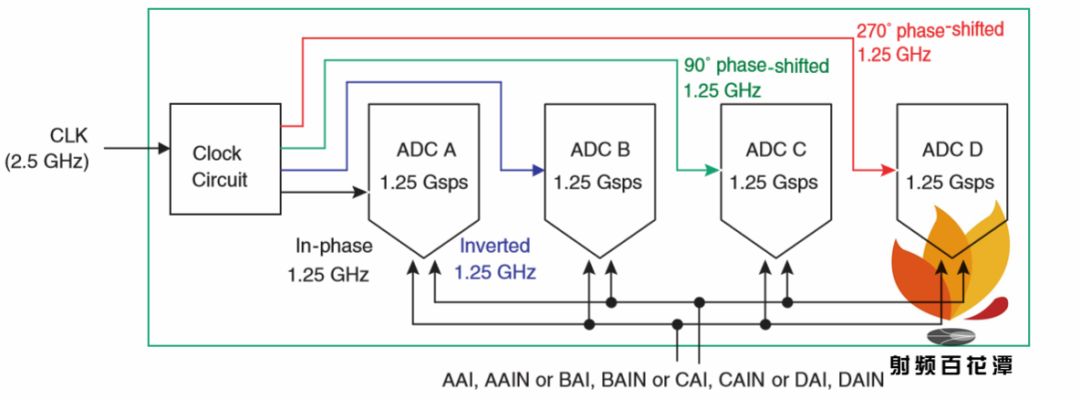

EV10AQ190可以工作在3種模式下,分別是采樣率為1.25GHz的四通道模式,采樣率為2.5GHz的雙通道模式以及采樣率為5GHz的單通道模式。EV10AQ190的所有控制參數,包括通道選擇、旁路模式、編碼格式、輸出多路分離器、積分非線性校正、偏置校正、增益校正、相位校正等,均可通過SPI串行控制端口對相應的控制寄存器進行設置。本文中,EV10AQ190配置工作在單通道模式,如圖1所示。

圖1 單通道模式時鐘驅動( 模擬信號由AAI /AAIN 輸入)

外部模擬信號通過一個射頻轉換器將單端信號轉換成差分信號,可選擇A、B、C、D任一通道輸入,輸入信號在內部同其他3路ADC連通,且4路ADC時鐘均由同一外部時鐘驅動,即4路ADC共用時鐘電路。在單通道模式下,外部輸入2.5GHz時鐘,該時鐘會被2分頻為1.25GHz,以驅動內部采樣時鐘。同相的1.25GHz時鐘驅動A路ADC,同時反相的1.25GHz時鐘驅動B路ADC,同相的1.25GHz時鐘經過90°延時后驅動C路ADC,反相的1.25GHz時鐘經過90°延時后驅動D路ADC,在此交錯拼接模式下將得到最高5GHz的等效采樣率。

2 高速ADC 接口設計中的關鍵技術2. 1 基于片同步技術的高速ADC 接口片同步(CHIPSYNC)是XILINX公司命名的一種同步技術,其本質是一種源同步技術,目的是為FPGA提供一個高速的源同步數據總線接口。它是XILINX公司在Virtex-4及之后系列FPGA上采用的一種技術,XILINXFPGA內部具有若干全局時鐘緩沖器(BUFG)和區域時鐘緩沖器(BUFR),特別適合做源同步接口。FPGA片內每個I/O管腳中集成了一個64階的可編程調節信號延遲的延時模塊(IODELAY),可精確控制信號延時實現采樣時鐘和數據相位的動態調整,從而確定信號采集的最佳采樣點,實現高速ADC接口的可靠、穩定工作。

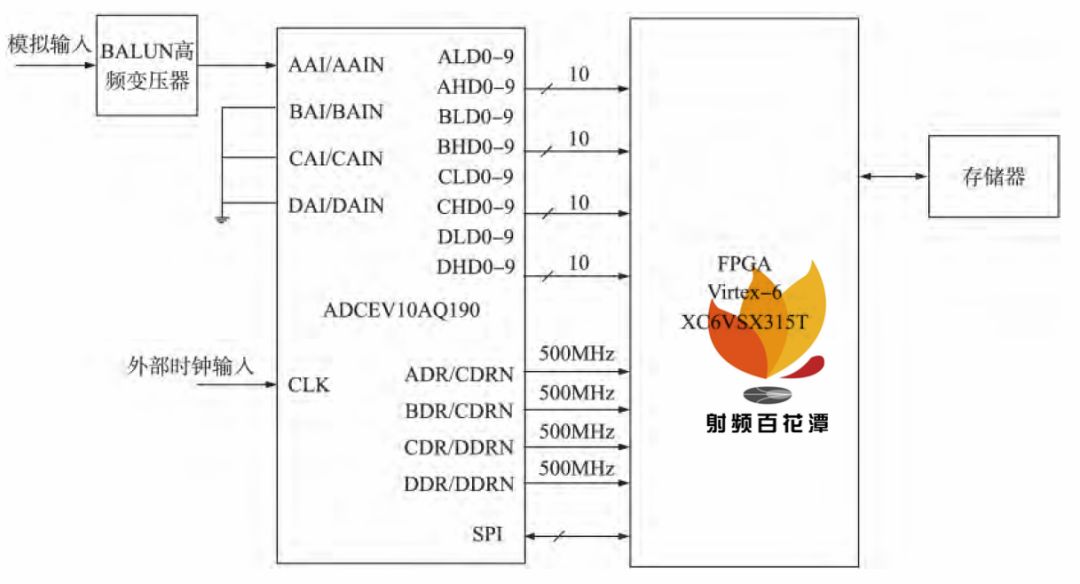

圖2 4. 0GHz 采樣高速ADC 接口電路原理框圖

圖2為基于片同步技術的4GHz采樣高速ADC接口電路原理框圖,主要包括高速ADC和高性能FPGA接口處理2部分。

模擬輸入信號經過巴倫(BALUN)變壓器完成單端信號到差分信號的轉換,然后輸入到高速ADC芯片EV10AQ190的模擬輸入端。利用XILINX公司高性能Virtex-6系列FPGA芯片XC6VSX315T中的40對LVDS管腳接收來自EV10AQ190的4路10bit1000Mbit/s的輸出數據,并用4個LVDS專用時鐘輸入通道接收4路ADC輸出的500MHz同步采樣時鐘(DDR輸出,采樣時鐘為數據速率的一半)。FPGA接收到的4路1000Mbit/s高速數據后,經過內部1:4串并轉換模塊(ISERDES)后,變成16路并行10bit數據,速度降為250Mbit/s,便于FPGA內部處理并和低速的外部存儲器相連。

2. 1. 1 高速ADC

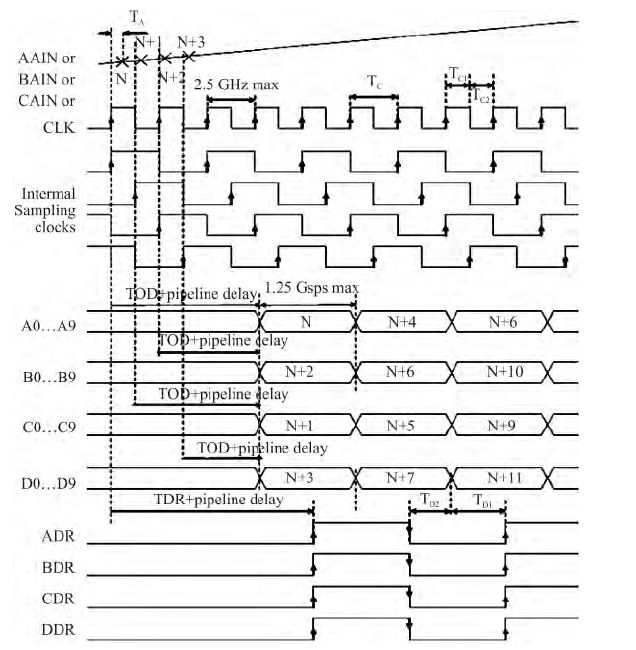

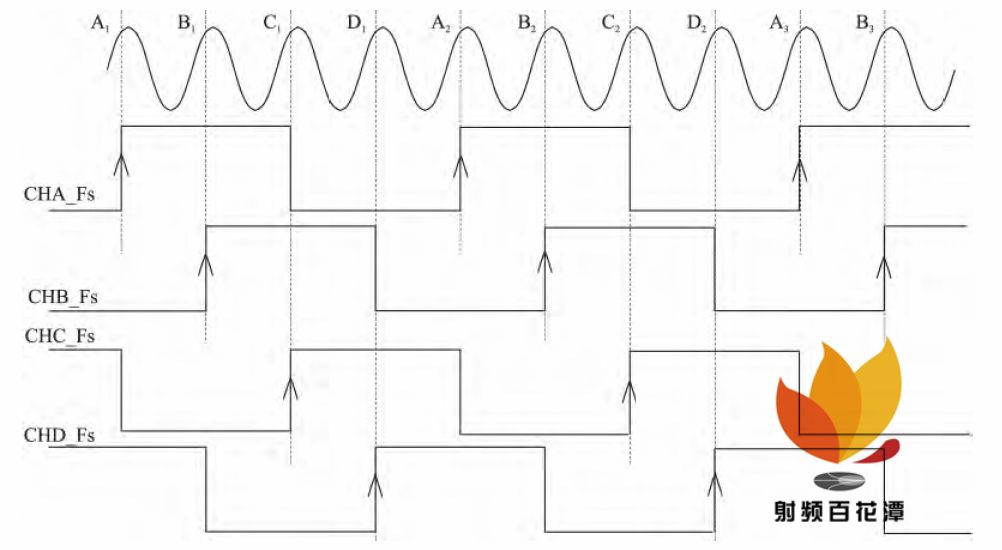

EV10AQ190工作在單通道模式下,模擬信號從ADC的A通道輸入,且DMUX=1:1輸出模式,此時ADC工作時序如圖3所示。

圖3EV10AQ190單通道模式1:1DMUX模式的工作時序

圖3中,芯片A端口上的模擬輸入將會在AHD0~AHD9、BHD0~BHD9、CHD0~CHD9和DHD0~DHD9上以交錯方式輸出。本文中,信號采樣率為4GHz,輸入芯片時鐘頻率為2GHz,內部4路ADC采樣時鐘為輸入時鐘頻率的一半,即內部4路ADC以1GHz進行采樣。ADC變換數據以DDR方式輸出,輸出1000Mbit/s速率數據的同時輸出500MHz同步采樣時鐘,輸出數據位寬為4×10=40對LVDS信號。

2. 1. 2 ADC 與FPGA 數據接口本文采用了XILINX公司Virtex-6系列FPGA(XC6VSX315T)來實現高速ADC接口。ADC芯片EV10AQ190輸出的數據和同步時鐘送到FPGA芯片XC6VSX315T中,Virtex-6系列FPGA具有多個專用LVDS差分邏輯接收通道,發送數據速率高達1.25Gbit/s,接收數據速率也高達1Gbit/s,能夠滿足EV10AQ190輸出數據和控制邏輯的要求。Virtex-6系列FPGA的每個I/O管腳都采用了CHIPSYNC技術[3],在其I/O管腳中嵌入了一個64階的可編程調節信號延遲的延時模塊IODELAY,對于200MHz延時時鐘(周期為5ns)輸入,可調節的最小延時為5ns/64=78.15ps。這樣,可以精確地獨立調整每根數據線的延遲,甚至可以通過設置一些控制信號在程序運行過程中改變信號的延遲,使鎖存時鐘可以精確地對準每根數據線數據有效窗口的中心,保證高速數據采集時整個數據總線的所有數據能夠可靠地鎖存。

FPGA內部數據和時鐘接收處理框圖如圖4所示,ADC數據和ADC時鐘信號通過專用差分數據接口IBUFDS和IBUFGDS進入FPGA內部,經精確延時模塊IODELAY進行相位動態調整,再經過輸入串并變換模塊ISERDES作1:4串并轉換,完成高速ADC數據的接收。

圖4 FPGA 內部數據和時鐘接收框圖

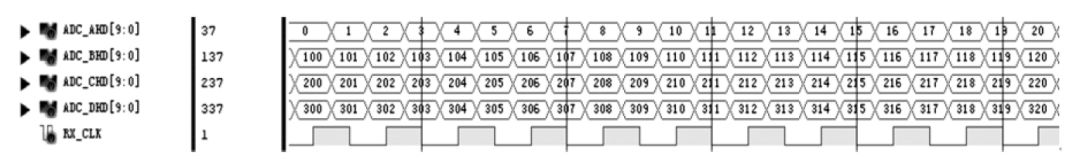

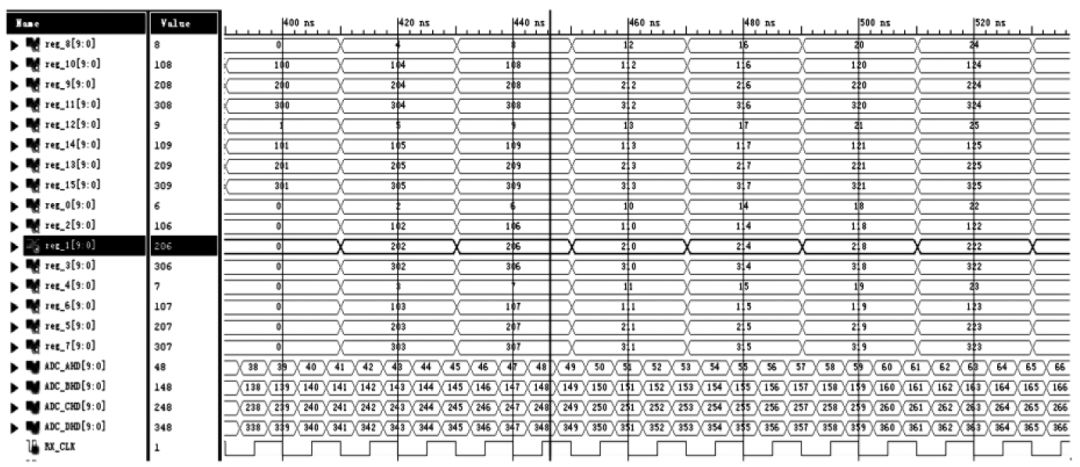

FPGA內部數據和時鐘接收功能采用VERILOG語言編程,設計中利用XILINX仿真軟件ISim對該程序進行了功能仿真。定義輸入的仿真激勵信號為4路10bit數據和時鐘,分別命名為ADC_AHD[9:0]、ADC_BHD[9:0]、ADC_CHD[9:0]、ADC_DHD[9:0]和RX_CLK,用來模擬ADC芯片EV10AQ190輸出的4路DDR方式的采樣數據和時鐘。其中,ADC_AHD為0~99循環計數,ADC_BHD為100~199循環計數,ADC_CHD為200~299循環計數,ADC_DHD為300~399循環計數,如圖5所示。

圖5 FPGA 內部時序仿真激勵信號

FPGA內部時序仿真結果如圖6所示。圖6中,reg0~15[9:0]為FPGA輸出的經過1:4串并轉換(ISERDES)后的16路10bit數據。從圖中可以看出,來自ADC芯片的4路高速串行數據變為16路較低速的并行數據,信號速率降為原來的1/4,并且輸出數據相對輸入數據具有十多個時鐘周期的延時,時序嚴格同步,驗證FPGA內部數據和時鐘接收處理程序的正確性。

圖6 FPGA 內部時序仿真結果

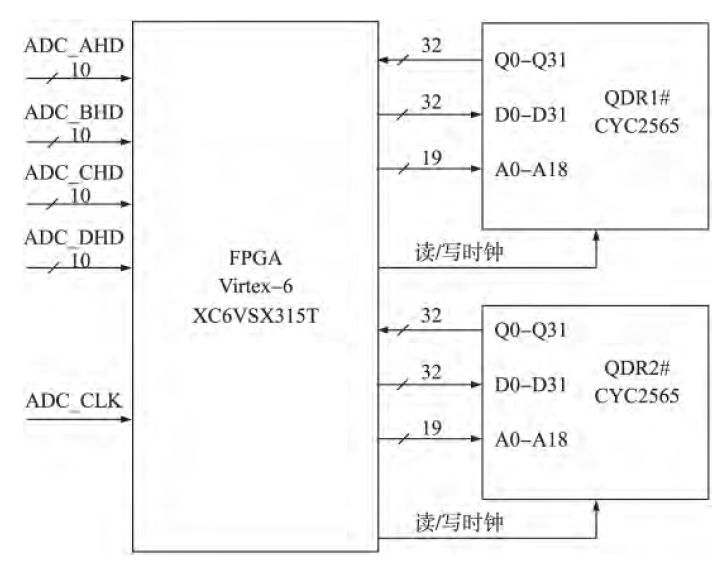

2. 2 QDR 存儲電路設計高速ADC 采集變換輸出數據經過FPGA 進行串并轉換降速處理、存儲器接口控制后可外接DDR( 雙倍數據速率) 或QDR( 四倍數據速率) 存儲器中進行緩存,本文高速ADC 接口電路用于寬帶雷達回波模擬系統,FPGA 外接存儲器為QDR SRAM 存儲器,用來實現對雷達發射信號的存儲轉發。

本文使用了CYPRESS公司的2片QDRSRAM存儲器CY7C2565KV18,FPGA和QDR存儲器之間的接口電路如圖7所示。

圖7 QDR 存儲器接口電路原理框圖

ADC芯片EV10AQ190輸出的4路10bit高速數據經過FPGA進行1:4串并變換后變為16路10bit數據,速率降為原來的1/4,便于和低速的QDR存儲器接口。再經過FPGA內部QDR讀寫控制器(XILINXFPGA內部專用的IPCore)后送到2片QDR存儲器CY7C2565KV18中進行暫存。

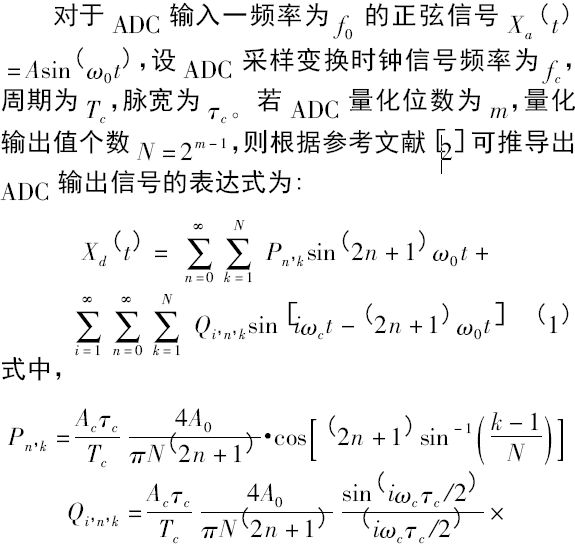

2. 3 多路ADC 校正技術2. 3. 1 ADC 輸出信號的雜散電平[2, 11]

從式(1)可以看出,ADC輸出信號頻率成分包括2部分:有用信號ω0和ω0的各次諧波分量(式(1)中的第一項)以及有用信號與采樣時鐘信號間的各次交調分量(式(1)中的第2項)。有用信號(ω0)的諧波分量可通過ADC之后的低通濾波器濾除,而有用信號和采樣時鐘間的某些交調分量,如ωc-ω0、ω0-ωc、2ωc-ω0頻率成分,會落在低通濾波器通帶內,無法濾除,影響ADC輸出信號無雜散動態范圍(SFDR)。因此,要提高ADC動態性能,必須盡量減小有用信號和采樣時鐘間的交調分量。

2. 3. 2 EV10AQ190 中多路ADC 校正方法

EV10AQ190芯片內部包含4個1.25GHz采樣率的ADC,通過交錯采樣拼接技術實現單通道最高5GHz采樣率。因此,要保證單通道模式下ADC輸出信號質量,減小ADC輸出信號雜散電平,必須確保內部4路ADC的幅度相同,相位上嚴格相差90°,即需要對EV10AQ190芯片內部4路ADC的直流偏置、增益、相位參數值進行校正,可通過內部SPI串行控制端口對相應的控制寄存器進行設置來完成。

EV10AQ190芯片工作在單通道模式下,若輸入芯片時鐘為fc,則內部4路ADC采樣率為fc/2,等效采樣率為2fc。輸入信號頻率為fin。根據2.3.1分析結果,影響ADC輸出信號SFDR性能的是有用信號和采樣時鐘間的某些交調分量,如fc-fin、fc/2-fin和fin-fc/2等均有可能落在低通濾波器通帶內,必須盡量抑制。通過幅相一致性校正技術可有效減小這些交調分量的大小。

EV10AQ190芯片內部多路ADC校正應注意兩點:一是校正順序是先校偏置,再校增益,最后校相位;二是校正時選擇輸入模擬信號頻率應選ADC最大頻率點。對于5GHz采樣,每路ADC采樣率為1.25GHz,故可選擇輸入校正信號頻率點為600.59MHz。

(1)偏置校正(OffsetCalibration)多通道ADC直流偏置不同將會影響輸出信號雜散分量中fc/2頻率信號電平大小,從而影響高速ADC的動態性能。由于ADC的偏置對增益和相位都有影響,因此首先應對偏置進行校正。EV10AQ190輸出為10bit無符號數,最大輸出值是1023,故直流偏置理論上應該為511。偏置的校正方法如下:ADC無信號輸入的情況下,記錄ADC輸出數據,計算4個通道ADC輸出數據的平均值,看平均值是否是511,如果是511說明偏置已經校好,如果不是,則通過SPI串口控制EV10AQ190的偏置控制寄存器來調整ADC偏置,調整完成,記錄并設置好4個通道偏置控制寄存器的值。

( 2) 增益校正( Gain Calibration)多通道ADC增益不同將會影響輸出信號雜散分量中fc-fin,fc/2-fin和fin-fc/2頻率信號電平大小,即影響輸入信號的鏡像頻率成分,從而影響ADC的動態性能。對增益的校正需要保證偏置已經校正完成。增益的校正方法如下:ADC輸入一個正弦信號,推薦頻率為600.59MHz,幅度為500mV,記錄下4個通道的采集數據并做FFT變換,比較4個通道采集數據頻譜的幅度是否相同。如果不同,以一個通道為標準,通過控制EV10AQ190的增益控制寄存器調整其他3個通道的增益,調整完成,記錄并設置好增益控制寄存器的值。增益校正過程要求輸入正弦信號和采樣時鐘信號要嚴格同源。( 3) 相位校正( Phase Calibration)多通道ADC相位不校準會影響輸出信號雜散分量中fc-fin,fc/2-fin和fin-fc/2頻率信號電平大小,即影響輸入信號的鏡像頻率成分,從而影響ADC的動態性能。

相位校正前應保證偏置和增益校正已完成。相位校正過程要求EV10AQ190輸入模擬信號頻率是輸入時鐘的2倍,是內部4通道ADC采樣率的4倍。對于EV10AQ190工作在單通道5GHz采樣模式下,輸入時鐘頻率為2.5GHz,內部每路ADC采樣率為1.25GHz,則將ADC的輸入模擬信號頻率設置為5GHz。如果EV10AQ190內部4路ADC相位嚴格相差90°,由于輸入信號頻率是內部ADC采樣時鐘頻率的4倍,則4個通道采集變換輸出信號幅度相等,4路ADC輸出將在一條直線上,如圖8所示。因此,相位校正時可以通過設置EV10AQ190的相位控制寄存器來調整A、B、C、D4個通道采樣時鐘的相位,使得4路輸出信號值(Ai、Bi、Ci、Di,i=1,2

,3,…)盡量相等。

圖8 ADC 相位校正原理

相位校正方法如下:ADC輸入一正弦信號,頻率是輸入采樣時鐘的2倍。記錄4個通道ADC輸出數據,如果4路ADC輸出數據相同,說明相位校正完成。如果不同,則以一個通道為基準,通過控制EV10AQ190的相位控制寄存器調整其他3個通道的相位,使得4個通道ADC輸出值相同。相位校正過程要求輸入正弦信號和采樣時鐘信號要嚴格同源。

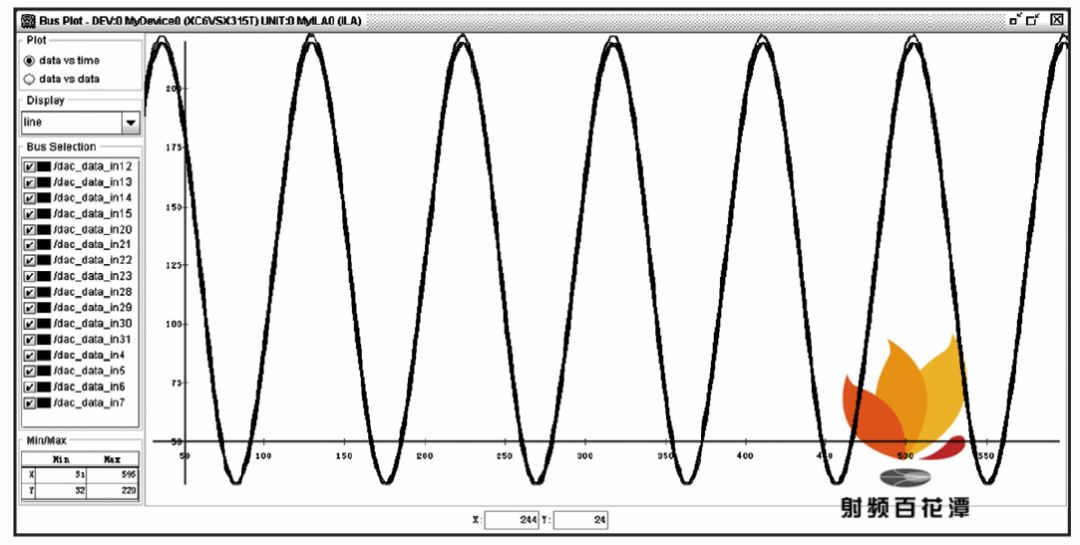

3 實驗與結果高速ADC接口程序在XILINX公司的ISE軟件中經過邏輯綜合、布局布線、目標代碼生成等過程,最終用高性能FPGA芯片XC6VSX315T實現,并下載到高速ADC接口電路板上的FPGA進行了實驗驗證。實驗過程設計如下:首先由信號源產生一點頻信號,頻率為500MHz,輸入采樣時鐘為2GHz,高速ADC采樣率為4GHz。500MHz點頻信號經過高速ADC芯片后變為4路并行的數字信號,數據速率為1000Mbit/s,進入FPGA芯片。然后在XILINX公司ChipScopeAnalyzer軟件中采集觀測高速ADC信號經過1:4串并變換后的數據,得到了16路10bit穩定的數據,并用總線(bus)波形圖方式顯示,如圖9所示:

圖9 FPGA 內部采集的ADC 輸出信號

圖9表明,用頻率為4GHz的采樣時鐘對頻率為500MHz的正弦信號進行采樣所得到的高速數據經過本文設計的高速ADC接口電路處理后得到了完美的正弦信號數據,從而證明了高速ADC接口電路的正確性和有效性。

另外,為測試多路校正技術對高速ADC接口電路性能影響效果,本文對校正前和校正后ADC輸出信號的無雜散動態范圍(SFDR)進行了測試。測試結果為:幅相一致性校正前輸出信號SFDR為35dBc,校正后輸出信號SFDR能夠達到42dBc,提高

了約7dBc。可見,多路校正技術對于改善高速ADC動態性能是十分明顯的。

4 結論

本文針對E2V公司的高速ADC芯片EV10AQ190,介紹了一種高速ADC接口電路設計方案。通過采用FPGA片同步技術和多路ADC校正技術,解決了高速電路中數據與時鐘的時序同步以及多通道ADC幅相一致性校正問題,確保了高速ADC的動態性能和可靠性。文章最后給出了硬件調試結果。

實驗結果表明,通過校正EV10AQ190芯片內部4路ADC的偏置、增益、相位并采用FPGA片同步技術,該高速ADC接口電路采樣率可達4GHz以上,雜散優于42dBc,高速ADC輸出數據能夠穩定、可靠的鎖存到FPGA內部。該接口電路方案已成功應用到某寬帶雷達回波模擬系統高速信號采集的設計中。

-

接口電路

+關注

關注

8文章

474瀏覽量

58534 -

adc

+關注

關注

100文章

7846瀏覽量

556686 -

模擬系統

+關注

關注

0文章

63瀏覽量

14060

原文標題:基于E2V的高速ADC接口設計

文章出處:【微信號:gh_f97d2589983b,微信公眾號:高速射頻百花潭】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一種低功耗以太網接口電路的設計方案

一種高速ADC接口電路設計方案

一種高速ADC接口電路設計方案

評論