UART(串口)收發模塊設計- 02

整體架構回顧

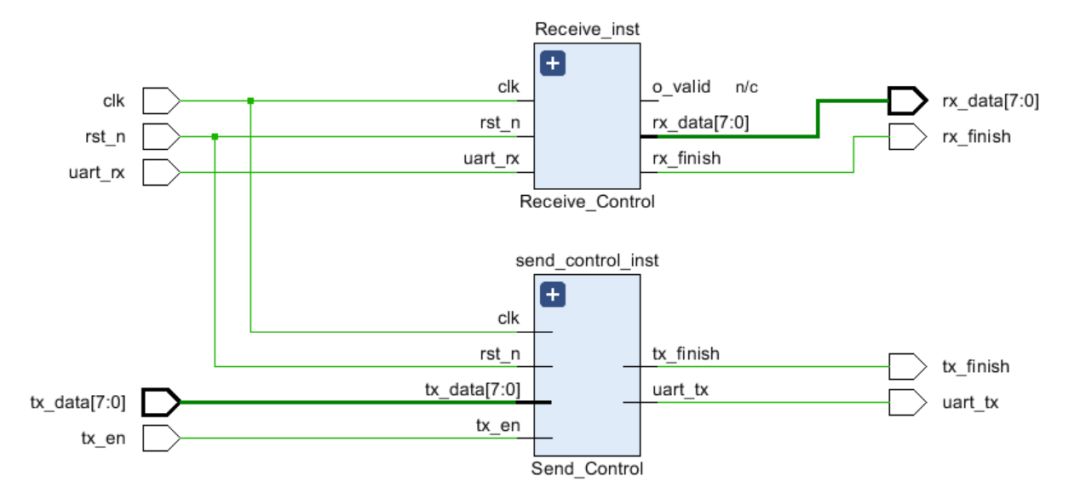

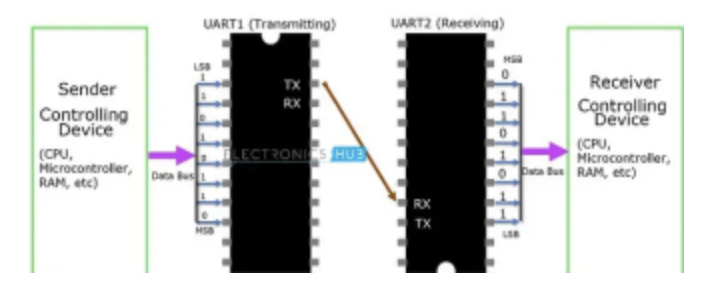

整體結構如下圖,整個UART有兩個大模塊,一個接收模塊,一個發送模塊。具體大家可以回顧文章《UART(串口)收發模塊設計- 01》。

波特率時鐘產生模塊

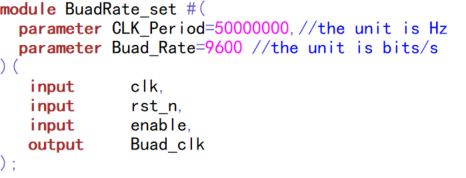

收發模塊里面都有一個波特率時鐘產生模塊BuadRate_set,用于將系統時鐘clk進行分頻,得到波特率時鐘Buad_clk,以控制數據的收發。

端口如下,通過CLK_Period指定當前的clk時鐘頻率,比如50M,則為50000000。Buad_Rate為設定的波特率。

主要設計代碼如下,通過localparam DIV_PEREM指定分頻計數值。分頻計數器為cnt,當enable為高時,cnt開始循環的從0遞增到DIV_PEREM。Buad_clk在每次cnt==DIV_PEREM的時候就翻轉一次,從而得到clk時鐘的CLK_Period/Buad_Rate倍分頻。

數據接收模塊

狀態機:數據接收模塊通過一個狀態機來控制。狀態機的跳轉由波特率時鐘下降沿控制。波特率時鐘Buad_clk起始為高電平。

IDLE:其中IDLE為空閑狀態,只有當檢測到起始位的時候,才進入GET_DATA。

GET_DATA:在GET_DATA狀態下獲得8位數據位數據,通過一個計數器來計數接收到的數據位數。當cnt為‘d7時表明接收到了8位數據,便跳到最后一個狀態END_BIT。

END_BIT:等待停止位的到來,然后回到IDLE狀態,完成數據的接收。

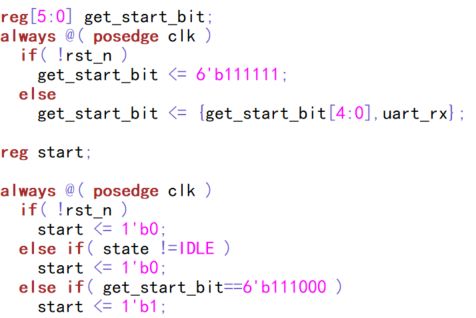

起始位的檢測:其實就是在IDLE狀態下,檢測uart_rx的下降沿,如下代碼所示。將uart_rx通過一個6bit的移位寄存器get_start_bit(uart_rx從低bit往高bit移動),那么當get_start_bit的,高3bit都為1,低3bit為0時,表明uart_rx出現了下降沿,此時將start拉高,以便啟動狀態機和波特率時鐘產生模塊BuadRate_set。

數據的接收:在GET_DATA狀態下,由波特率時鐘的下降沿控制,將uart_rx往一個8bit的移位寄存器送,uart_rx從高bit向低bit流動(由于串口發送是先發低位數據)。

數據發送模塊

狀態機:數據接收模塊通過一個狀態機來控制。狀態機的跳轉由clk時鐘上升沿控制。

IDLE:IDLE為空閑狀態,當檢測到tx_en(發送使能信號)為高,則進入EN_TX模塊。

EN_TX:在EN_TX模塊發送10bit數據(起始位,數據位,停止位)。數據的發送由波特率時鐘Buad_clk上升沿控制。如下代碼,在cnt為0時將tx_data(待發送的數據位)與起始位(0),裝載到data_to_send中,然后對data_to_send做從高位向低位的移位操作,高位填1。將data_to_send的最低位接uart_tx,發送出去。利用cnt計數發送的位數。

上板實測

這里設計了一個實測設計(UART_TEST),功能如下:

上電復位后,通過串口向上位機發送數據8'h34,然后只要收到上位機發送過來的數據,就將其返回給上位機。

大家可以把源碼下下來,自己新建工程,結合開發板上板測試一下。

文件里面提供了一個PC端串口調試上位機SSCOM。大家在上板測試時,需要一個USB轉串口器(有的開發板上集成了這個),使得板子的串口可以通過USB端口與PC上位機通信。

-

寄存器

+關注

關注

31文章

5608瀏覽量

130013 -

計數器

+關注

關注

32文章

2316瀏覽量

98210 -

時鐘

+關注

關注

11文章

1972瀏覽量

135023

原文標題:UART(串口)收發模塊設計- 02

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

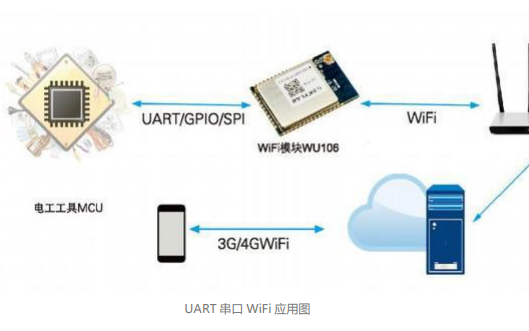

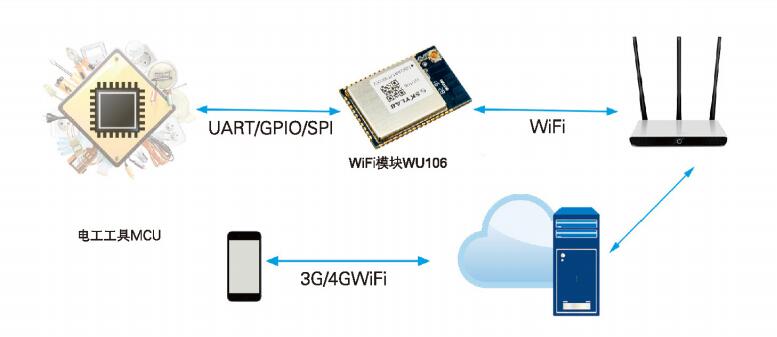

Iot物聯網UART串口WiFi模塊及智能插座wifi模塊解決方案

物聯網UART串口WiFi模塊及智能插座方案app界面介紹

uart是什么意思?認識uart串口

ESP8266方案小尺寸、UART串口WiFi模塊規格書下載.pdf

UART串口WiFi模塊的工作原理及應用

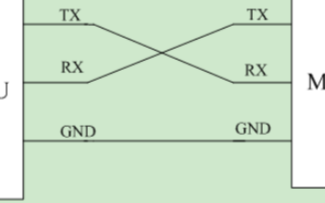

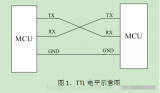

串口、COM口、UART口, TTL、RS-232、RS-485區別詳解

SKYLAB UART串口WiFi模塊改進無線控制設計—簡化設計

【CubeIDE】STM32 HAL庫史上最詳細教程(一):UART串口收發

串口、COM口、UART口和TTL、RS-232、RS-485介紹

UART(串口)收發模塊設計

UART(串口)收發模塊設計

評論