12位高速IF采樣ADC——AD9433的技術解析與應用指南

在電子設計領域,模數轉換器(ADC)是連接模擬世界和數字世界的關鍵橋梁。今天,我們要深入探討一款高性能的12位ADC——AD9433,它在高速采樣和寬頻應用中表現卓越。

文件下載:AD9433.pdf

一、AD9433概述

AD9433是一款12位的單片采樣模數轉換器,集成了片上跟蹤保持電路,設計初衷是為了便于使用。它的轉換速率最高可達125 MSPS,在寬帶和高IF載波系統中能提供出色的動態性能。

1.1 主要特性

- IF采樣能力:支持高達350 MHz的IF采樣,適用于3G寬帶蜂窩IF采樣接收器。

- 出色的動態性能:在105 MSPS時,SNR可達67.5 dB( (f{IN}) 達Nyquist頻率),SFDR在 (f{IN}=70 MHz) 時為83 dBc, (f_{IN}=150 MHz) 時為72 dBc。

- 寬輸入范圍:具有2 V p-p的模擬輸入范圍。

- 片上功能:集成時鐘占空比穩定電路、參考和跟蹤保持電路以及SFDR優化電路。

- 良好的線性度:DNL典型值為±0.25 LSB,INL典型值為±0.5 LSB。

- 寬模擬帶寬:全功率模擬帶寬達750 MHz。

- 低功耗:在125 MSPS時,典型功耗為1.35 W。

- 靈活的數據格式:支持二進制補碼或偏移二進制數據格式。

- 電源兼容性:5.0 V模擬電源供電,2.5 V至3.3 V TTL/CMOS輸出。

1.2 應用領域

- 蜂窩基礎設施通信系統

- 3G單載波和多載波接收器

- IF采樣方案

- 寬帶載波頻率系統

- 點對點無線電

- LMDS、無線寬帶

- MMDS基站單元

- 電纜反向路徑

- 通信測試設備

- 雷達和衛星地面系統

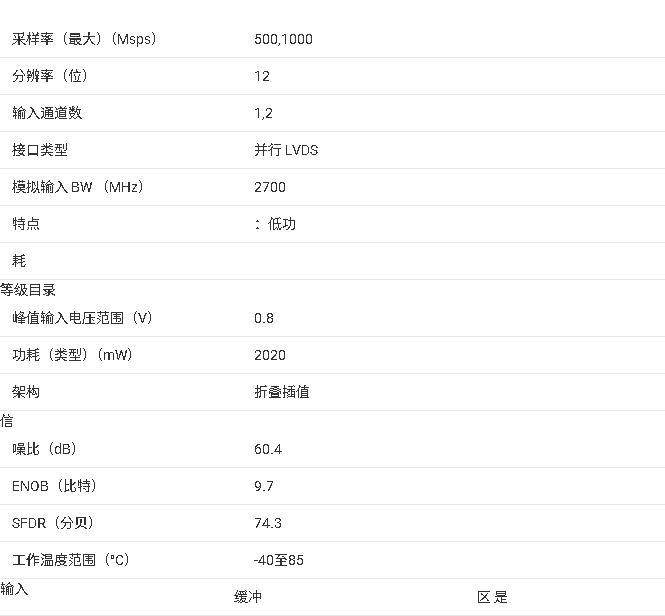

二、詳細規格參數

2.1 直流規格

包括分辨率、精度、熱漂移、參考電壓、模擬輸入、電源等參數。例如,分辨率為12位,保證無丟失碼,偏移誤差和增益誤差在一定范圍內,內部參考電壓典型值為2.5 V等。

2.2 交流規格

涵蓋動態性能指標,如信噪比(SNR)、信噪失真比(SINAD)、有效位數(ENOB)、諧波失真、雜散自由動態范圍(SFDR)等。不同輸入頻率下,這些指標表現不同,為設計提供了詳細的性能參考。

2.3 開關規格

涉及編碼速率、編碼脈沖寬度、孔徑延遲、抖動、輸出有效時間、輸出傳播延遲等參數,這些參數對于確保ADC的正確工作和數據傳輸至關重要。

三、功能模塊與工作原理

3.1 功能框圖

AD9433的功能框圖展示了其內部結構,包括模擬輸入、跟蹤保持電路、流水線ADC、輸出級等部分。各部分協同工作,實現模擬信號到數字信號的轉換。

3.2 工作原理

AD9433采用開關電容架構的12位流水線轉換器,優化后可在Nyquist極限及以上提供平坦的動態性能。DNL過渡誤差在最終測試時校準到典型精度0.25 LSB或更低。

3.2.1 編碼輸入

AD9433對用戶提供的采樣時鐘質量極為敏感。它具有內部時鐘占空比穩定電路,可鎖定ENCODE的上升沿(差分驅動時為 (ENCODE) 的下降沿)并優化內部時序。編碼輸入支持差分或單端信號,推薦使用差分信號以獲得最佳動態性能。

3.2.2 模擬輸入

模擬輸入是一個差分緩沖器,通過片上電阻分壓器自偏置,將直流共模電壓設置為標稱4 V。為獲得額定性能,建議采用差分驅動輸入,并且在高頻應用中,可能需要使用兩個變壓器以減少偶次諧波失真。

3.2.3 SFDR優化

SFDR MODE引腳設置為邏輯1時,可啟用專有的電路,改善AD9433的雜散自由動態范圍(SFDR)性能。但該動態特性可能不適用于某些時域應用,可將該引腳接地禁用此功能。

3.2.4 數字輸出

數字輸出為3 V(2.7 V至3.3 V)TTL/CMOS兼容,通過數據格式選擇(DFS)CMOS輸入可選擇偏移二進制或二進制補碼編碼。

3.2.5 電壓參考

AD9433內置穩定準確的2.5 V參考電壓(VREFOUT)。正常工作時,通過將引腳45連接到引腳46并在VREFIN處放置0.1 μF去耦電容來使用內部參考。調整參考電壓可調節輸入范圍,且在±5%范圍內調整參考電壓時,性能不會有明顯下降。

3.2.6 時序

AD9433提供鎖存數據輸出,經過10個流水線延遲后,在編碼命令上升沿后一個傳播延遲(tPD)輸出數據。為減少轉換器內部的瞬態,應盡量減小輸出數據線的長度和負載。

四、典型性能特性

通過一系列的FFT圖和性能曲線,展示了AD9433在不同采樣率、輸入頻率、SFDR模式下的性能表現,如SNR、SFDR、諧波失真等指標隨輸入信號的變化情況。這些特性有助于工程師根據實際應用需求選擇合適的工作參數。

五、應用注意事項

5.1 布局信息

推薦使用多層板以獲得最佳效果,使用高質量陶瓷芯片電容直接在器件處將每個電源引腳接地去耦。數字輸出和輸入應隔離布局,避免數字輸出耦合到模擬部分。編碼電路布局也很關鍵,應將其視為模擬輸入,編碼時鐘需與數字輸出和模擬輸入隔離。

5.2 替換AD9432

AD9433與AD9432引腳兼容,但有兩個控制引腳不同。使用AD9433替換AD9432時,SFDR改善電路將啟用,DFS引腳浮空選擇二進制補碼編碼。同時,兩者的模擬和編碼輸入共模電壓有所不同,可通過交流耦合實現互換使用。

六、總結

AD9433作為一款高性能的12位ADC,在高速采樣和寬頻應用中具有顯著優勢。其豐富的特性、良好的性能指標以及靈活的設計使得它在眾多通信和電子系統中得到廣泛應用。工程師在使用時,需根據具體應用需求合理選擇工作參數,并注意布局和替換等方面的問題,以充分發揮AD9433的性能優勢。你在使用AD9433或類似ADC時遇到過哪些問題呢?歡迎在評論區分享交流。

-

adc

+關注

關注

100文章

7893瀏覽量

556697 -

高速采樣

+關注

關注

0文章

4瀏覽量

7064

發布評論請先 登錄

12位高速IF采樣ADC——AD9433的技術解析與應用指南

12位高速IF采樣ADC——AD9433的技術解析與應用指南

評論