TMS320VC5409A 定點數(shù)字信號處理器深度解析

引言

在數(shù)字信號處理(DSP)領(lǐng)域,TMS320VC5409A 定點數(shù)字信號處理器憑借其卓越的性能和豐富的功能,成為眾多工程師的首選。它基于先進(jìn)的改進(jìn)型哈佛架構(gòu),擁有強大的處理能力和豐富的外設(shè),廣泛應(yīng)用于通信、音頻處理、工業(yè)控制等多個領(lǐng)域。本文將深入解析 TMS320VC5409A 的各項特性、功能以及相關(guān)的技術(shù)參數(shù),為電子工程師在設(shè)計中提供全面的參考。

文件下載:tms320vc5409a.pdf

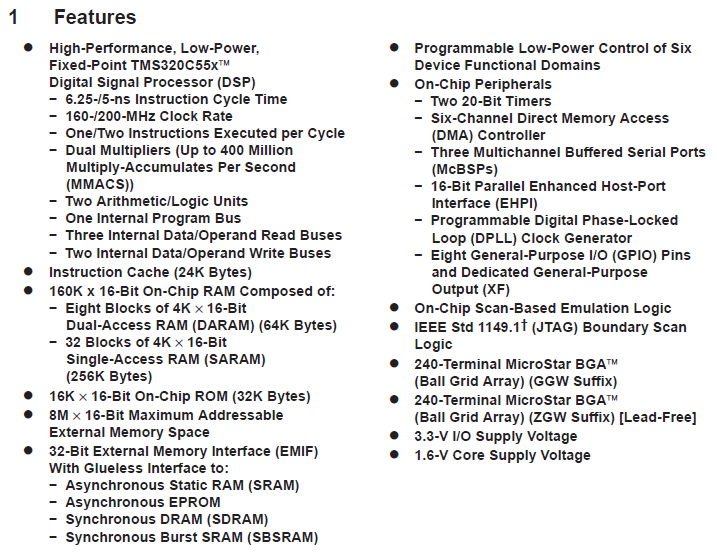

一、TMS320VC5409A 特性概覽

1.1 先進(jìn)架構(gòu)與強大運算能力

TMS320VC5409A 采用先進(jìn)的多總線架構(gòu),具備三條獨立的 16 位數(shù)據(jù)存儲器總線和一條程序存儲器總線,為數(shù)據(jù)的高效傳輸和處理提供了堅實的基礎(chǔ)。其 40 位算術(shù)邏輯單元(ALU),包含 40 位桶形移位器和兩個獨立的 40 位累加器,能夠?qū)崿F(xiàn)高精度的算術(shù)運算。17×17 位并行乘法器與 40 位專用加法器的結(jié)合,使得非流水線單周期乘法/累加(MAC)操作成為可能,大大提高了運算效率。

1.2 豐富的尋址與指令系統(tǒng)

該處理器擁有兩個地址生成器和八個輔助寄存器,以及兩個輔助寄存器算術(shù)單元(ARAUs),支持靈活的尋址模式。同時,其指令集豐富多樣,包括單指令重復(fù)和塊重復(fù)操作、塊內(nèi)存移動指令等,為程序代碼的優(yōu)化和數(shù)據(jù)管理提供了便利。

1.3 高效的內(nèi)存管理

TMS320VC5409A 配備 32K×16 位的片上 RAM 和 16K×16 位的片上 ROM,片上 RAM 由四個 8K×16 位的塊組成,支持雙訪問功能,可在一個周期內(nèi)進(jìn)行兩次讀取或一次讀取和一次寫入操作。此外,它還支持?jǐn)U展尋址模式,可訪問最大 8M×16 位的外部程序空間。

1.4 豐富的外設(shè)接口

處理器集成了多種片上外設(shè),如軟件可編程等待狀態(tài)生成器、可編程存儲體切換、增強型外部并行接口(XIO2)、六通道直接內(nèi)存訪問(DMA)控制器、三個多通道緩沖串行端口(McBSPs)以及 8/16 位增強型并行主機端口接口(HPI8/16)等,為系統(tǒng)的擴展和外設(shè)的連接提供了豐富的選擇。

1.5 低功耗設(shè)計

TMS320VC5409A 支持 IDLE1、IDLE2 和 IDLE3 指令的掉電模式,可有效降低功耗。同時,通過 CLKOUT 關(guān)閉控制功能,可進(jìn)一步減少功耗,延長設(shè)備的續(xù)航時間。

二、引腳分配與信號描述

2.1 引腳分配

TMS320VC5409A 提供兩種封裝形式:144 引腳球柵陣列(BGA)和 144 引腳薄型四方扁平封裝(LQFP)。文檔詳細(xì)給出了這兩種封裝的引腳分配圖和表格,方便工程師在設(shè)計 PCB 時進(jìn)行準(zhǔn)確的布局。

2.2 信號描述

文檔對每個引腳的功能和操作模式進(jìn)行了詳細(xì)描述,包括數(shù)據(jù)信號、初始化與復(fù)位信號、多處理信號、內(nèi)存控制信號、振蕩器/定時器信號、多通道緩沖串行端口信號、主機端口接口信號、電源引腳和測試引腳等。例如,地址總線 A[22:0]和數(shù)據(jù)總線 D[15:0]具有總線保持器功能,可消除無源元件并降低功耗;中斷信號 INT0 - INT3 為可屏蔽外部用戶中斷輸入,NMI 為不可屏蔽中斷等。

三、功能概述

3.1 內(nèi)存管理

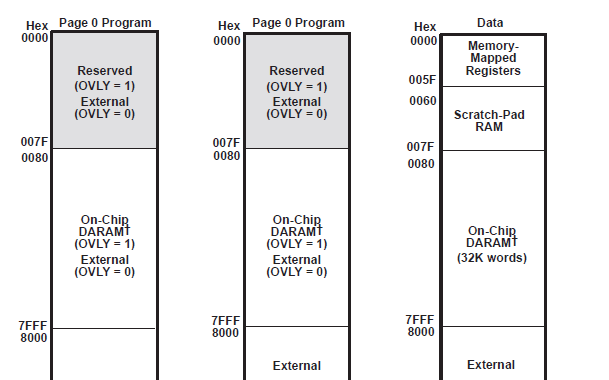

3.1.1 數(shù)據(jù)內(nèi)存

數(shù)據(jù)內(nèi)存空間可尋址高達(dá) 64K 的 16 位字。當(dāng)?shù)刂吩谄?RAM 范圍內(nèi)時,設(shè)備會自動訪問片上 RAM;當(dāng)?shù)刂烦?RAM 范圍時,則會自動進(jìn)行外部訪問。使用片上內(nèi)存具有性能高、成本低、功耗低等優(yōu)點,而使用片外內(nèi)存則可訪問更大的地址空間。

3.1.2 程序內(nèi)存

軟件可將內(nèi)存單元配置在程序地址映射內(nèi)或外。當(dāng)單元映射到程序空間時,設(shè)備會自動訪問它們;當(dāng)?shù)刂烦龇秶鷷r,會自動進(jìn)行外部訪問。同樣,片上程序內(nèi)存具有性能高、成本低、功耗低的優(yōu)勢,而片外程序內(nèi)存可提供更大的地址空間。

3.1.3 擴展程序內(nèi)存

TMS320VC5409A 在程序空間采用分頁擴展內(nèi)存方案,可訪問高達(dá) 8192K 的程序內(nèi)存。它具備 23 條地址線、一個額外的內(nèi)存映射寄存器 XPC 以及六條用于尋址擴展程序空間的額外指令。程序內(nèi)存被組織成 128 頁,每頁長度為 64K,XPC 寄存器的值定義了頁面選擇。

3.1.4 片上 ROM 與引導(dǎo)加載器

片上 16K 字×16 位的可屏蔽 ROM 只能映射到程序內(nèi)存空間,用戶可根據(jù)特定應(yīng)用對其進(jìn)行編程。標(biāo)準(zhǔn)的片上 ROM 包含引導(dǎo)加載器,可在電源上電時自動將用戶代碼從外部源傳輸?shù)匠绦騼?nèi)存的任意位置。

3.1.5 片上 RAM

片上 32K 字×16 位的雙訪問 RAM(DARAM)由四個 8K 字的塊組成,每個塊可在一個周期內(nèi)支持兩次讀取或一次讀取和一次寫入操作。通過設(shè)置 OVLY 位為 1,可將 DARAM 映射到程序/數(shù)據(jù)空間。

3.1.6 片上內(nèi)存安全

TMS320VC5409A 提供可屏蔽選項來保護(hù)片上內(nèi)存的內(nèi)容。當(dāng) ROM 保護(hù)位設(shè)置時,外部發(fā)起的指令無法訪問片上內(nèi)存空間,但 HPI 寫入不受限制,HPI 讀取則限制在 4000h - 5FFFh 范圍內(nèi)。

3.1.7 可重定位中斷向量表

復(fù)位、中斷和陷阱向量在程序空間中尋址,這些向量是軟向量,處理器在捕獲時會將程序計數(shù)器(PC)加載為陷阱地址并執(zhí)行向量位置的代碼。在設(shè)備復(fù)位時,這些向量映射到程序空間的地址 FF80h,但在設(shè)備復(fù)位后,可通過加載處理器模式狀態(tài)(PMST)寄存器中的中斷向量指針(IPTR)位,將它們重新映射到程序空間中任何 128 字頁面的開頭。

3.2 片上外設(shè)

3.2.1 軟件可編程等待狀態(tài)生成器

軟件等待狀態(tài)生成器可將外部總線周期延長至最多 14 個機器周期。對于需要超過 14 個等待狀態(tài)的設(shè)備,可使用硬件 READY 線進(jìn)行接口。當(dāng)所有外部訪問配置為零等待狀態(tài)時,等待狀態(tài)生成器的內(nèi)部時鐘會自動禁用,從而降低功耗。

3.2.2 可編程存儲體切換

可編程存儲體切換邏輯允許處理器在外部內(nèi)存存儲體之間切換,而無需為需要額外時間關(guān)閉的內(nèi)存設(shè)置外部等待狀態(tài)。當(dāng)訪問跨越程序或數(shù)據(jù)空間內(nèi) 32K 字的內(nèi)存存儲體邊界時,存儲體切換邏輯會自動插入一個周期。

3.2.3 總線保持器

處理器具有兩個總線保持器控制位 BH 和 HBH,用于控制地址總線(A[15 - 0])、數(shù)據(jù)總線(D[15 - 0])和 HPI 數(shù)據(jù)總線(HD[7 - 0])的總線保持器。通過合理配置這些位,可有效減少靜態(tài)功耗。

3.2.4 并行 I/O 端口

TMS320VC5409A 擁有總共 64K 個 I/O 端口,可通過 PORTR 指令或 PORTW 指令進(jìn)行尋址。IS 信號用于指示通過 I/O 端口的讀寫操作,處理器可通過 I/O 端口輕松與外部設(shè)備接口,同時只需最少的片外地址解碼電路。

3.2.5 增強型 8/16 位主機端口接口(HPI8/16)

HPI8/16 是標(biāo)準(zhǔn) 8 位 HPI 的增強版本,可用于與 8 位或 16 位主機接口。當(dāng)外部 I/O 的地址和數(shù)據(jù)總線未使用時,可將其配置為 HPI16 以與 16 位主機接口。HPI8 支持順序傳輸或隨機訪問傳輸,具備主機中斷和 C54x 中斷能力;HPI16 則提供 16 位雙向數(shù)據(jù)總線,支持多種數(shù)據(jù)選通和控制信號,可實現(xiàn)與各種主機的無縫接口。

3.2.6 多通道緩沖串行端口(McBSPs)

片上提供三個多通道緩沖串行端口,支持全雙工通信、雙緩沖數(shù)據(jù)寄存器,可實現(xiàn)連續(xù)數(shù)據(jù)流。它具有獨立的接收和傳輸幀同步和時鐘,可直接與 T1/E1 成幀器、MVIP 交換兼容和 ST - BUS 兼容設(shè)備、IOM - 2 兼容設(shè)備、AC97 兼容設(shè)備以及串行外設(shè)接口(SPI)等接口。此外,McBSP 還支持最多 128 個通道的多通道傳輸和接收,可選擇多種數(shù)據(jù)大小,具備 μ 律和 A 律壓縮擴展功能,以及可編程的幀同步和數(shù)據(jù)時鐘極性。

3.2.7 硬件定時器

處理器配備一個 16 位定時電路和一個 4 位預(yù)分頻器。定時器計數(shù)器每 CLKOUT 周期遞減一次,當(dāng)計數(shù)器遞減到 0 時,會生成一個定時器中斷。可通過特定狀態(tài)位停止、重啟、復(fù)位或禁用定時器。

3.2.8 時鐘生成器

時鐘生成器由鎖相環(huán)(PLL)電路組成,為處理器提供時鐘。它需要一個參考時鐘輸入,可由外部時鐘源提供。參考時鐘輸入可通過除以 2(DIV 模式)或使用 PLL 電路(PLL 模式)乘以一個比例因子來生成設(shè)備時鐘,從而允許使用頻率低于 CPU 的時鐘源。軟件可編程的 PLL 具有高度的靈活性,可通過 16 位內(nèi)存映射的時鐘模式寄存器(CLKMD)進(jìn)行控制。

3.2.9 增強型外部并行接口(XIO2)

XIO2 對外部接口進(jìn)行了重新設(shè)計,簡化了總線序列,提高了讀寫操作轉(zhuǎn)換時對總線爭用的免疫力,支持 DMA 控制器對外部內(nèi)存的訪問,并優(yōu)化了掉電模式。大多數(shù)外部訪問現(xiàn)在需要 3 個周期,包括一個前導(dǎo)周期、一個活動(讀或?qū)懀┲芷诤鸵粋€尾隨周期,同時提供連續(xù)讀取模式以保持高速讀取訪問。

3.2.10 DMA 控制器

DMA 控制器可在內(nèi)存映射中的各點之間傳輸數(shù)據(jù),而無需 CPU 干預(yù)。它具有六個獨立的可編程通道,允許在 CPU 操作的后臺進(jìn)行數(shù)據(jù)傳輸。DMA 具有獨立于 CPU 操作、多通道、高優(yōu)先級、可獨立編程優(yōu)先級、靈活的地址索引模式、可由選定事件初始化傳輸、完成塊傳輸時可發(fā)送中斷以及支持雙字內(nèi)部傳輸?shù)忍攸c。同時,它支持對擴展程序、擴展數(shù)據(jù)和擴展 I/O 內(nèi)存的外部訪問,但有一定的限制條件。

3.2.11 通用 I/O 引腳

除了標(biāo)準(zhǔn)的 BIO 和 XF 引腳外,TMS320VC5409A 還有一些引腳可配置為通用 I/O。這些引腳包括 18 個 McBSP 引腳和 8 個 HPI 數(shù)據(jù)引腳,其通用 I/O 功能僅在不需要主要引腳功能時可用。

3.2.12 設(shè)備 ID 寄存器

片上添加了一個只讀內(nèi)存映射寄存器,用于允許用戶應(yīng)用程序軟件識別程序正在執(zhí)行的設(shè)備。

3.2.13 內(nèi)存映射寄存器

處理器擁有 27 個內(nèi)存映射的 CPU 寄存器,映射在數(shù)據(jù)內(nèi)存空間地址 0h 到 1Fh。每個設(shè)備還有一組與外設(shè)相關(guān)的內(nèi)存映射寄存器,這些寄存器用于控制和配置處理器的各種功能。

3.2.14 中斷

文檔詳細(xì)列出了所有內(nèi)部和外部中斷的向量相對位置和優(yōu)先級,以及中斷標(biāo)志寄存器(IFR)和中斷屏蔽寄存器(IMR)的位布局。通過合理配置這些寄存器,可實現(xiàn)對中斷的有效管理。

四、支持與文檔資源

TI 為 TMS320VC5409A 提供了廣泛的文檔支持,包括 TMS320C54x DSP 家族功能概述、TMS320LC54x 功耗計算、TMS320C54x DSP 參考集等。這些文檔涵蓋了 CPU 架構(gòu)、總線結(jié)構(gòu)、內(nèi)存結(jié)構(gòu)、片上外設(shè)、指令集等方面的詳細(xì)信息,為工程師的設(shè)計和開發(fā)提供了有力的支持。

五、電氣規(guī)格

5.1 絕對最大額定值

文檔給出了 TMS320VC5409A 在工作外殼溫度范圍內(nèi)的絕對最大額定值,包括電源電壓范圍、輸入電壓范圍、輸出電壓范圍、工作外殼溫度范圍和存儲溫度范圍等。超過這些額定值可能會對設(shè)備造成永久性損壞。

5.2 推薦工作條件

推薦工作條件包括設(shè)備的電源電壓、輸入輸出電壓、電流、工作外殼溫度等參數(shù)。在設(shè)計電路時,應(yīng)確保設(shè)備在這些推薦條件下工作,以保證其性能和可靠性。

5.3 電氣特性

文檔詳細(xì)列出了在推薦工作外殼溫度范圍內(nèi)的電氣特性,如高電平輸出電壓、低電平輸出電壓、輸入電流、電源電流、輸入電容和輸出電容等。這些特性為電路設(shè)計和性能評估提供了重要的參考依據(jù)。

5.4 時鐘選項

處理器支持多種時鐘選項,包括將參考時鐘頻率除以 2 或 4 以及乘以一個因子 N 來生成內(nèi)部機器周期。文檔給出了不同時鐘選項的配置方法和相關(guān)的時序要求,工程師可根據(jù)具體需求選擇合適的時鐘模式。

5.5 內(nèi)存和并行 I/O 接口時序

文檔詳細(xì)描述了內(nèi)存讀取、內(nèi)存寫入、I/O 讀取和 I/O 寫入的時序要求和切換特性,同時考慮了 HOLD 操作對地址延遲時間的影響。這些時序信息對于確保數(shù)據(jù)的正確傳輸和處理至關(guān)重要。

5.6 其他時序

還給出了 READY 信號、HOLD 和 HOLDA 信號、復(fù)位、BIO、中斷、MP/MC 信號、指令獲取(IAQ)和中斷確認(rèn)(IACK)信號、外部標(biāo)志(XF)和 TOUT 信號、多通道緩沖串行端口(McBSP)以及主機端口接口(HPI)的時序要求和切換特性。

六、機械數(shù)據(jù)

文檔提供了 TMS320VC5409A 不同封裝的機械數(shù)據(jù),包括封裝的熱阻特性、外形尺寸和引腳布局等。這些信息對于 PCB 設(shè)計和散熱設(shè)計具有重要的指導(dǎo)意義。

總結(jié)

TMS320VC5409A 定點數(shù)字信號處理器以其先進(jìn)的架構(gòu)、豐富的功能和良好的電氣性能,為電子工程師在數(shù)字信號處理領(lǐng)域的設(shè)計提供了強大的支持。通過深入了解其特性、功能和技術(shù)參數(shù),工程師可以充分發(fā)揮該處理器的優(yōu)勢,設(shè)計出高效、穩(wěn)定的數(shù)字信號處理系統(tǒng)。在實際應(yīng)用中,工程師還需根據(jù)具體需求合理選擇時鐘模式、配置外設(shè)接口、優(yōu)化內(nèi)存管理等,以實現(xiàn)系統(tǒng)的最佳性能。你在使用 TMS320VC5409A 進(jìn)行設(shè)計時,是否遇到過一些特殊的挑戰(zhàn)呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

數(shù)字信號處理器

+關(guān)注

關(guān)注

5文章

519瀏覽量

28431

發(fā)布評論請先 登錄

TMS320VC5510 5510A定點數(shù)字信號處理器的詳細(xì)介紹概述

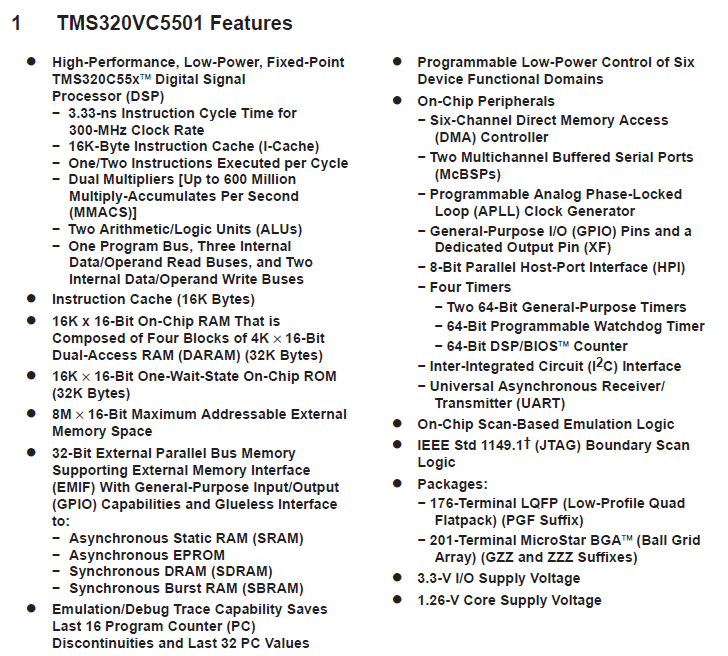

TMS320VC5501定點數(shù)字信號處理器詳細(xì)英文原版資料概述

SM320VC5409EP定點數(shù)字信號處理器的詳細(xì)資料概述

TMS320VC5402A定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5410A定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5506定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5502定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5409A定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5509A定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5503定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5402定點數(shù)字信號處理器數(shù)據(jù)表

TMS320VC5409A 定點數(shù)字信號處理器深度解析

TMS320VC5409A 定點數(shù)字信號處理器深度解析

評論