關(guān)鍵詞:十值門電路 十值加法器 十值陣列式乘法器 十值觸發(fā)器

十值十進(jìn)制及N值N進(jìn)制邏輯其本質(zhì)是“獨(dú)值”邏輯的累計(jì)組合形態(tài),而“獨(dú)值”邏輯和二值邏輯又充分兼容,于是十值十進(jìn)制及N值N進(jìn)制邏輯和二值邏輯亦是充分兼容的。

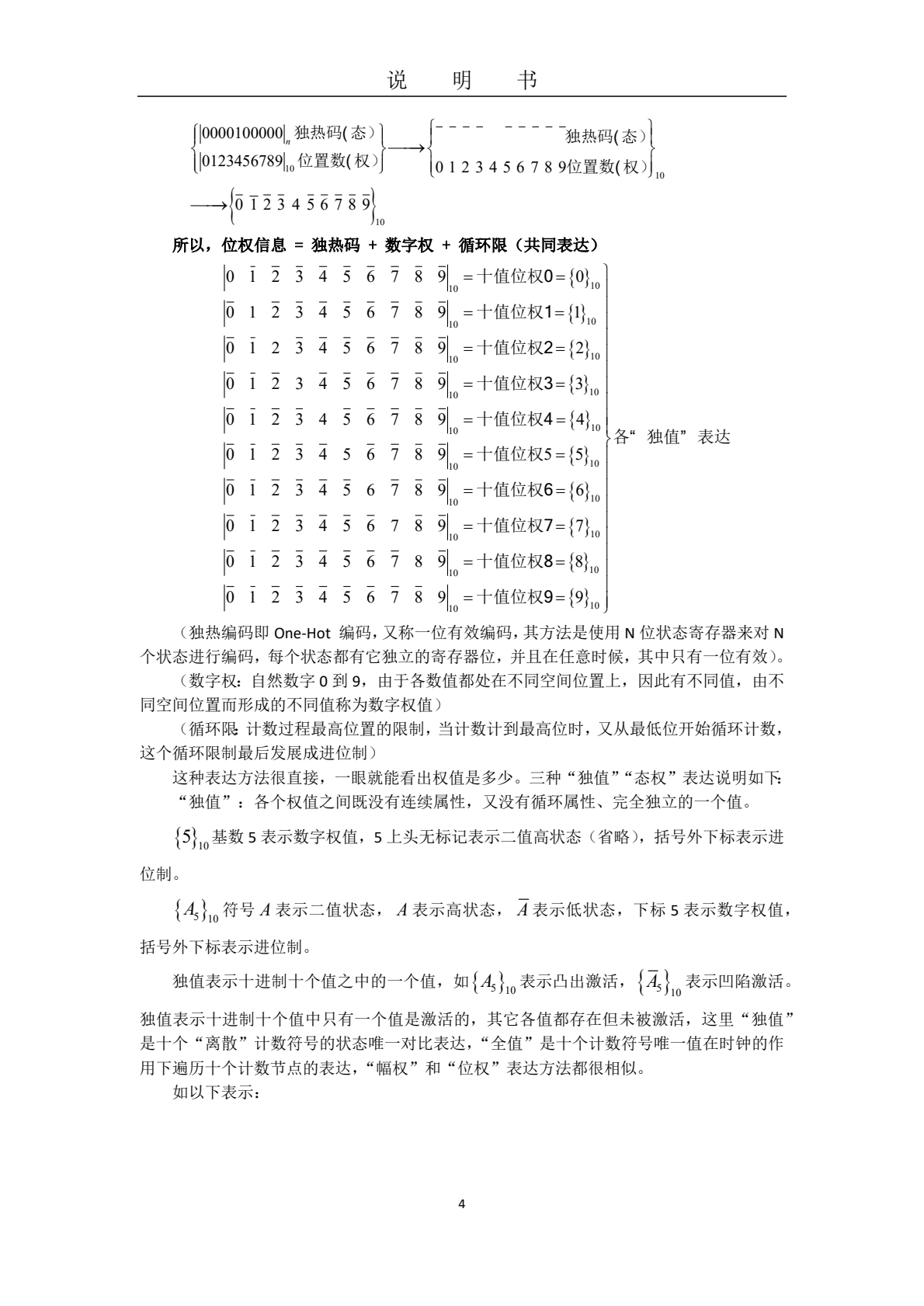

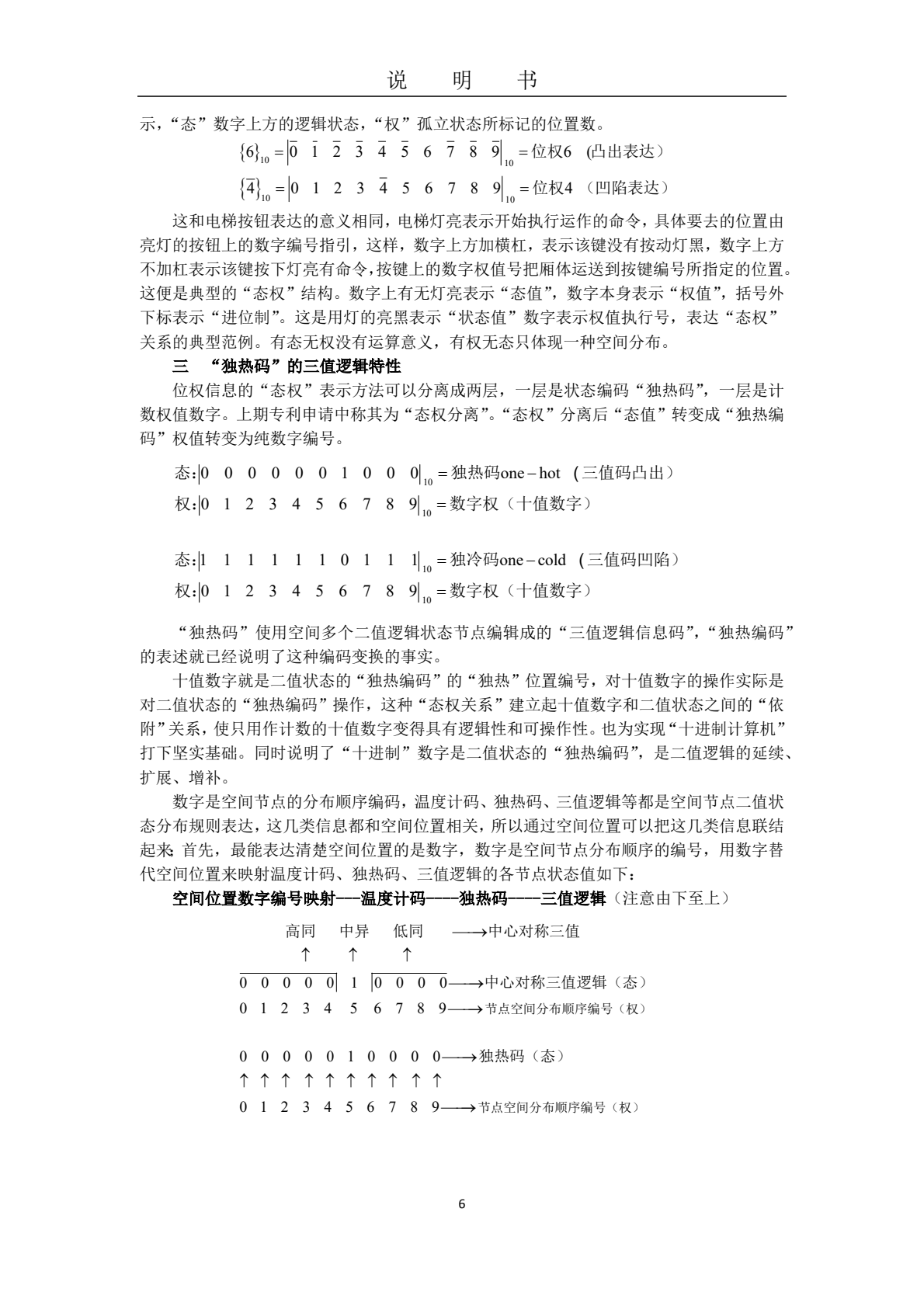

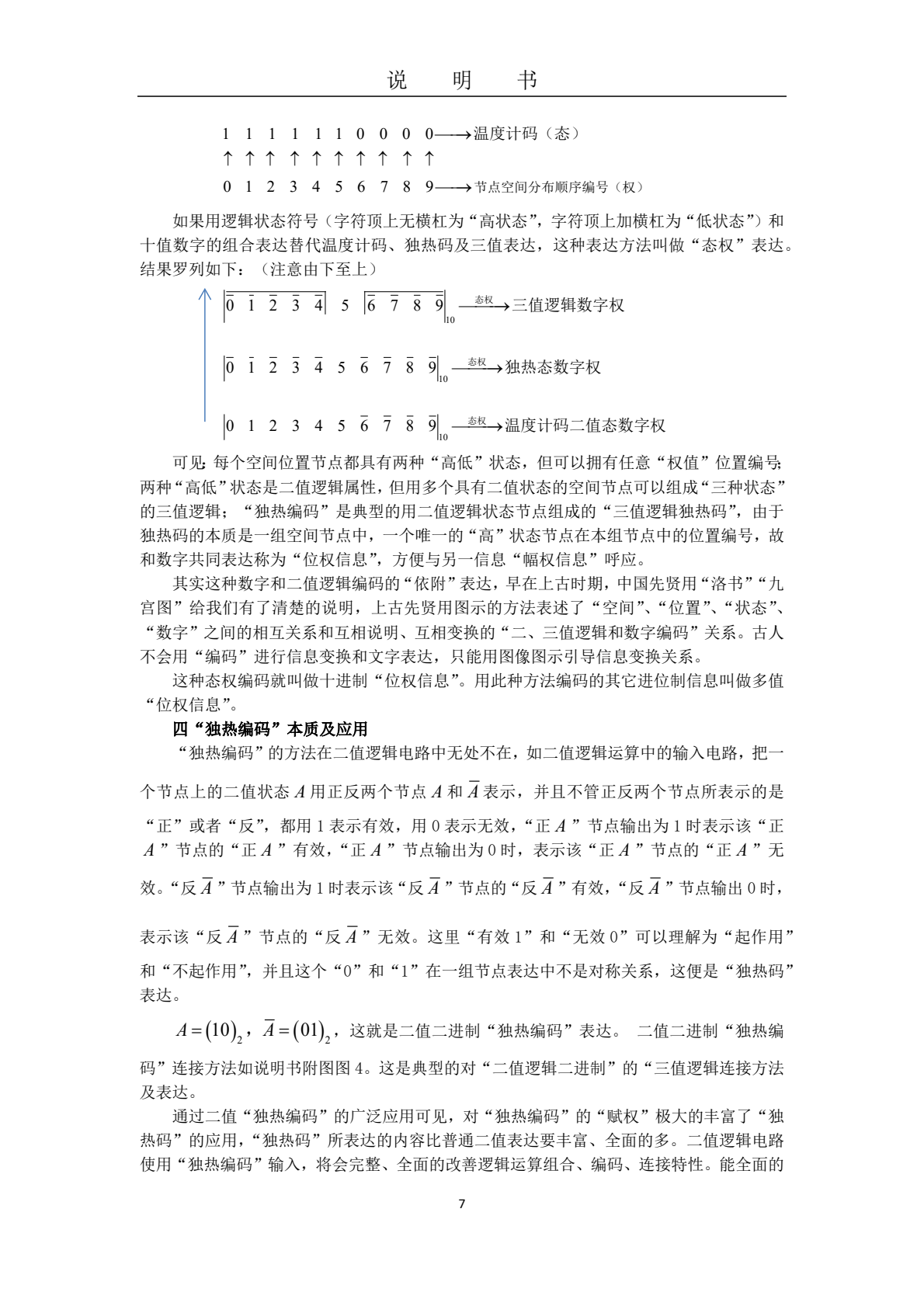

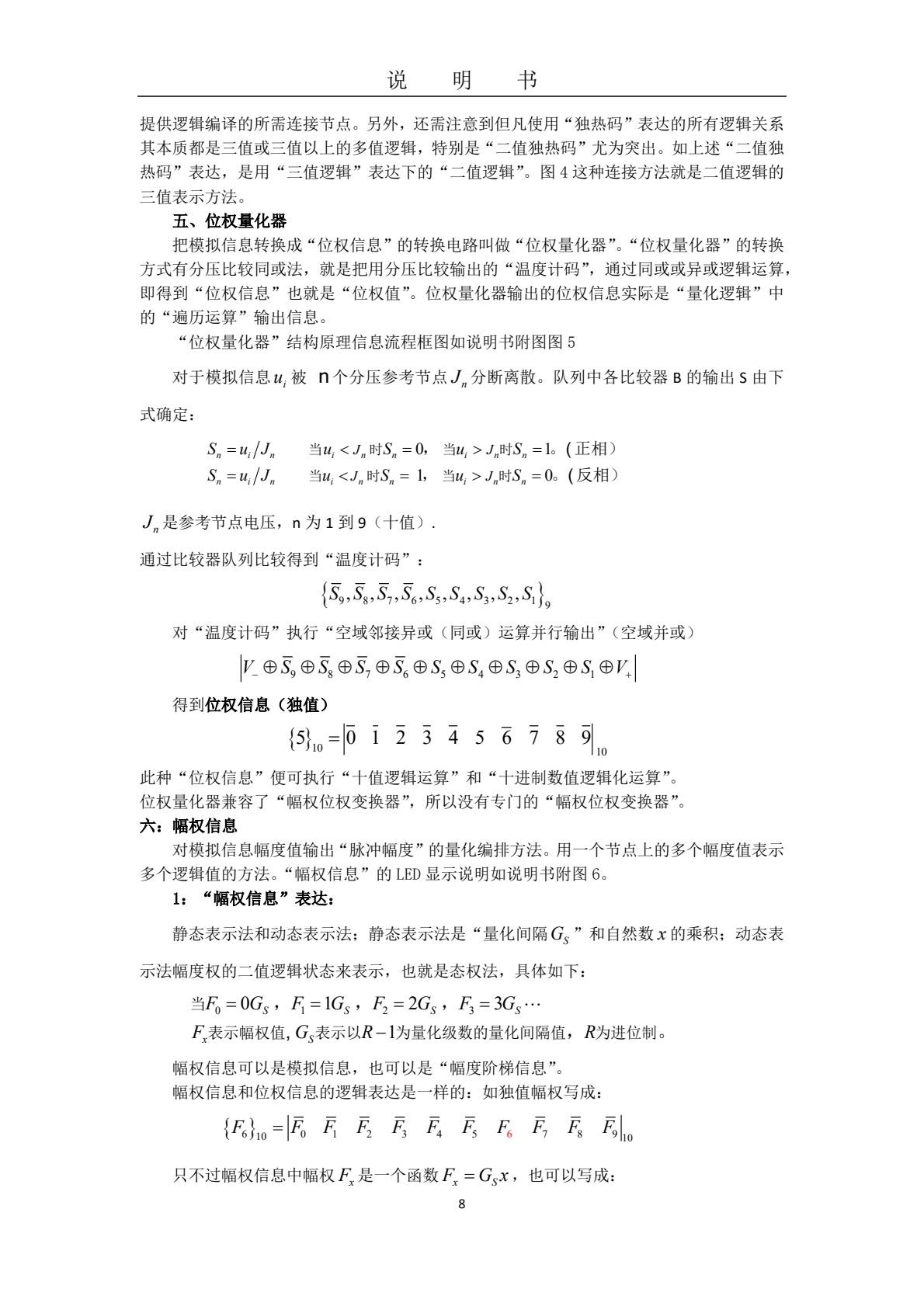

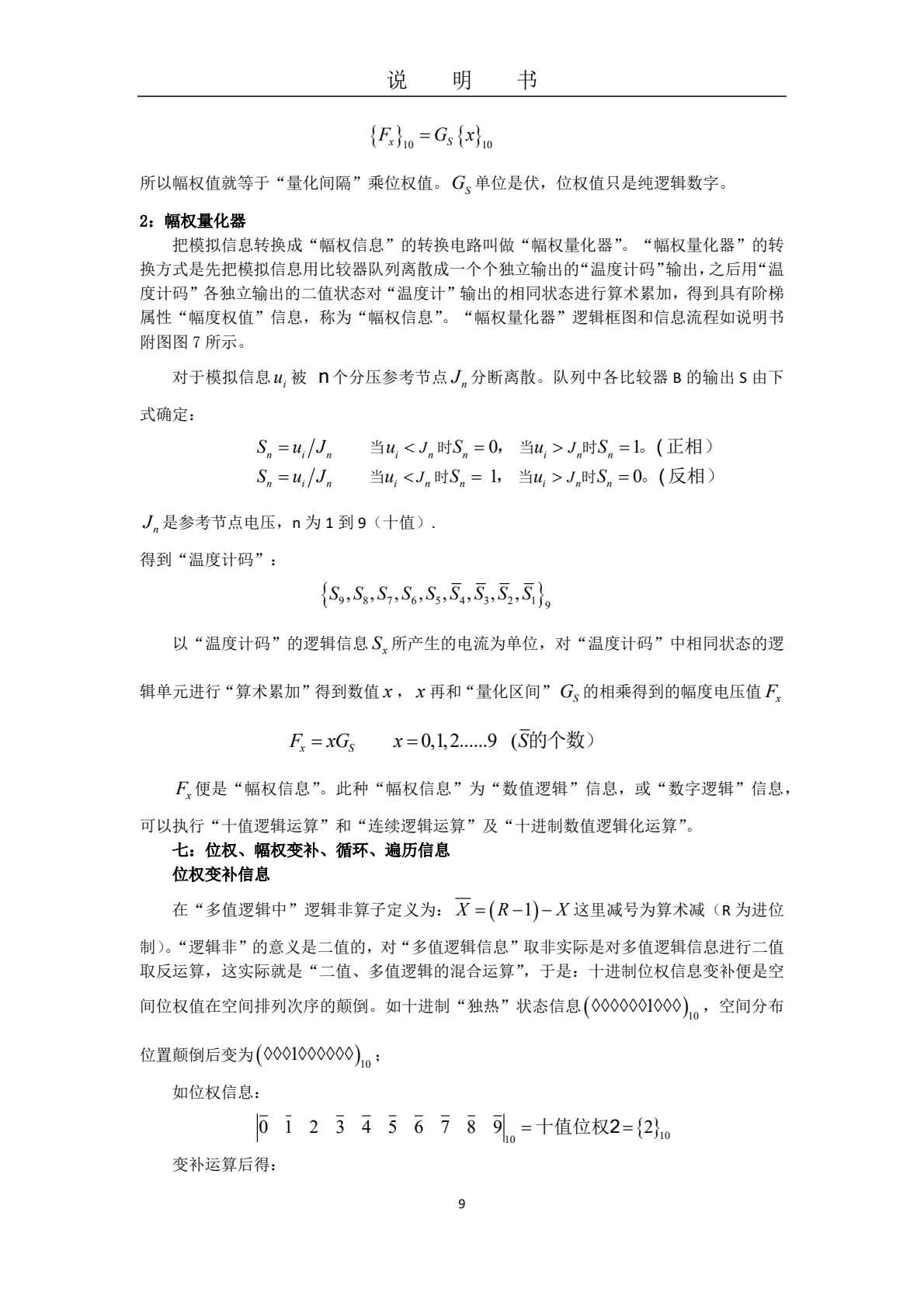

十進(jìn)制數(shù)字計(jì)算機(jī)和多進(jìn)制計(jì)算機(jī)原理:十進(jìn)制數(shù)字計(jì)算機(jī)和多進(jìn)制計(jì)算機(jī)原理本質(zhì)是“獨(dú)值”邏輯運(yùn)算。十進(jìn)制數(shù)字計(jì)算機(jī)和多進(jìn)制計(jì)算機(jī)先把“模擬信息”通過偏置方法轉(zhuǎn)換成“連續(xù)邏輯信息”,之后再通過“量化器”把“連續(xù)邏輯信息”量化成“位權(quán)信息”和“幅權(quán)信息”,由于“幅權(quán)信息”是“獨(dú)值”信息的串行時(shí)序循環(huán)鏈,“位權(quán)信息”是“獨(dú)值”信息的并行秩序遍歷環(huán)。

因此在電路實(shí)現(xiàn)中“位權(quán)信息”是用“一條線路表示一個(gè)邏輯值”或“一個(gè)連接節(jié)點(diǎn)表示一個(gè)邏輯值”,因此可以用“十條線路為一組表示十個(gè)邏輯值”,用N條線路表示N個(gè)邏輯值,所以“位權(quán)信息”可以在不產(chǎn)生“新的邏輯器件”的前提下,用現(xiàn)有的二值元件進(jìn)行“十值數(shù)字運(yùn)算”和多值數(shù)字運(yùn)算,因?yàn)椤坝檬畻l線路表示十個(gè)邏輯值”的方法和用N條線路表示N個(gè)邏輯值的方法,把“串行運(yùn)行”的十個(gè)及N個(gè)邏輯值用“并行的方式”在空間展開,針對(duì)每個(gè)邏輯值的運(yùn)算不是通過時(shí)間步驟和復(fù)雜的十值和N值邏輯門實(shí)現(xiàn),而是通過對(duì)空間分布的十值十條線路和二值邏輯元件進(jìn)行并行編碼連接實(shí)現(xiàn)邏輯運(yùn)算和數(shù)值編碼運(yùn)算。此種運(yùn)算方法在駁回專利申請(qǐng)201710023530.1,1201711119713.X,201910156036.1,201910155703.4,等多件專利申請(qǐng)都是這樣運(yùn)算的。

十進(jìn)制計(jì)算機(jī)是基于“獨(dú)值”量化邏輯理論而實(shí)現(xiàn)的獨(dú)值邏輯計(jì)算機(jī),有十進(jìn)制數(shù)字計(jì)算機(jī),十進(jìn)制網(wǎng)絡(luò)計(jì)算機(jī),十進(jìn)制模擬計(jì)算機(jī),十進(jìn)制模糊計(jì)算機(jī)等;十進(jìn)制計(jì)算機(jī)實(shí)現(xiàn)了計(jì)算機(jī)類型多樣化,計(jì)算機(jī)進(jìn)位系統(tǒng)的多值化;方便用戶有更大的類型選擇空間,使用戶實(shí)現(xiàn)更專業(yè)的更高效多值運(yùn)算體驗(yàn)。計(jì)算機(jī)類型的多樣化,使用戶精準(zhǔn)的選擇適合自己的計(jì)算機(jī)類型,從而事半功倍;計(jì)算機(jī)運(yùn)算邏輯值的多值化,使用戶可以選擇適合自己專業(yè)的運(yùn)算系統(tǒng),使工作更高效;這些實(shí)質(zhì)的應(yīng)用徹底打破了二值邏輯計(jì)算機(jī)的壟斷,更突破了數(shù)據(jù)安全的屏障,建立起數(shù)據(jù)壁壘,使計(jì)算機(jī)數(shù)據(jù)更為安全專業(yè),使運(yùn)算系統(tǒng)朝著運(yùn)算多值化、運(yùn)算類型多樣化、信息安全專業(yè)化的時(shí)代發(fā)展。

本次公開展示的是“十進(jìn)制量化邏輯門電路”,“十進(jìn)制量化邏輯門電路”包含:十值取大門,十值取小門,十值取逆門,十值求同門,十值取異門等。申請(qǐng)附圖的每張圖參數(shù)齊全,讀者可依圖中參數(shù)直接仿真、搭建實(shí)驗(yàn)電路。各邏輯門電路邏輯關(guān)系正確,說明書附圖中亦有“狄摩根律”驗(yàn)證仿真。讀者可自行仿真或?qū)嶒?yàn)制作驗(yàn)證。

審核編輯 黃宇

-

邏輯門電路

+關(guān)注

關(guān)注

2文章

69瀏覽量

12522

發(fā)布評(píng)論請(qǐng)先 登錄

由順序主導(dǎo)的計(jì)算機(jī)體系

十進(jìn)制計(jì)算機(jī)硬件體系結(jié)構(gòu)及“獨(dú)值”量化邏輯運(yùn)算革命

十進(jìn)制計(jì)算機(jī)硬件體系結(jié)構(gòu)及“獨(dú)值”量化邏輯運(yùn)算革命(一)

解析SN54145、SN54LS145、SN74145、SN74LS145 BCD-十進(jìn)制解碼器/驅(qū)動(dòng)器

操作系統(tǒng)體系結(jié)構(gòu)

長(zhǎng)晶科技邏輯芯片產(chǎn)品矩陣介紹

定點(diǎn)數(shù)表示實(shí)數(shù)的方法以及定點(diǎn)數(shù)在硬件上的運(yùn)算驗(yàn)證

多值電場(chǎng)型電壓選擇晶體管結(jié)構(gòu)

咨詢符合國(guó)標(biāo)GB/T 4728.12-2022的邏輯門電路設(shè)計(jì)軟件

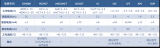

DPU核心技術(shù)論文再次登陸體系結(jié)構(gòu)領(lǐng)域旗艦期刊《IEEE Transactions on Computers》

睿創(chuàng)微納AI芯片技術(shù)登上國(guó)際計(jì)算機(jī)體系結(jié)構(gòu)領(lǐng)域頂級(jí)會(huì)議

基于LockAI視覺識(shí)別模塊:C++圖像的基本運(yùn)算

多值電場(chǎng)型電壓選擇晶體管結(jié)構(gòu)

多值電場(chǎng)型電壓選擇晶體管結(jié)構(gòu)

CMOS邏輯IC是如何構(gòu)成的

十進(jìn)制計(jì)算機(jī)硬件體系結(jié)構(gòu)及“獨(dú)值”量化邏輯運(yùn)算革命 (二) 十值量化邏輯門電路

十進(jìn)制計(jì)算機(jī)硬件體系結(jié)構(gòu)及“獨(dú)值”量化邏輯運(yùn)算革命 (二) 十值量化邏輯門電路

評(píng)論