SiC MOSFET的溝槽柵(Trench)物理與可靠性研究

1. 緒論:功率半導體物理的范式轉移

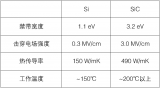

全球能源結構的電氣化轉型,從電動汽車(EV)的牽引逆變器到可再生能源的并網接口,正在推動功率半導體器件向更高效率、更高功率密度和更極端工作環(huán)境的方向發(fā)展。作為第三代寬禁帶半導體的代表,碳化硅(Silicon Carbide, SiC)憑借其約為硅(Si)10倍的臨界擊穿場強、3倍的熱導率以及更高的飽和電子漂移速度,已成為高壓(650V-3300V)功率轉換領域的基石材料。然而,材料的優(yōu)越性僅僅是基礎,器件的微觀結構設計才是釋放其理論性能極限的關鍵。在SiC MOSFET的技術演進路線圖中,從平面柵(Planar Gate)向溝槽柵(Trench Gate)的架構轉型,代表了物理層面的根本性變革。這一轉型并非簡單的幾何形狀改變,而是對溝道遷移率物理、靜電場分布控制以及可靠性工程的全面重構。

傳統(tǒng)的平面柵SiC MOSFET雖然制造工藝相對成熟且具備較高的短路耐受能力(SCWT),但其性能正逼近物理極限。其主要瓶頸在于為了屏蔽柵氧化層而在漂移區(qū)頂部形成的JFET(結型場效應管)區(qū)域所帶來的寄生電阻,以及在SiC(0001)硅面上形成的MOS反型層較低的溝道遷移率。溝槽柵技術通過挖掘垂直溝道,不僅消除了JFET電阻效應,還能夠利用高遷移率的晶體面(如a面或m面)進行導電,從而大幅降低比導通電阻(Ron,sp)。然而,這種幾何結構的改變在帶來導通性能飛躍的同時,也引入了極其嚴峻的電場管理挑戰(zhàn),特別是溝槽底角的電場擁擠效應,直接威脅到柵氧化層(Gate Oxide)的長期可靠性。

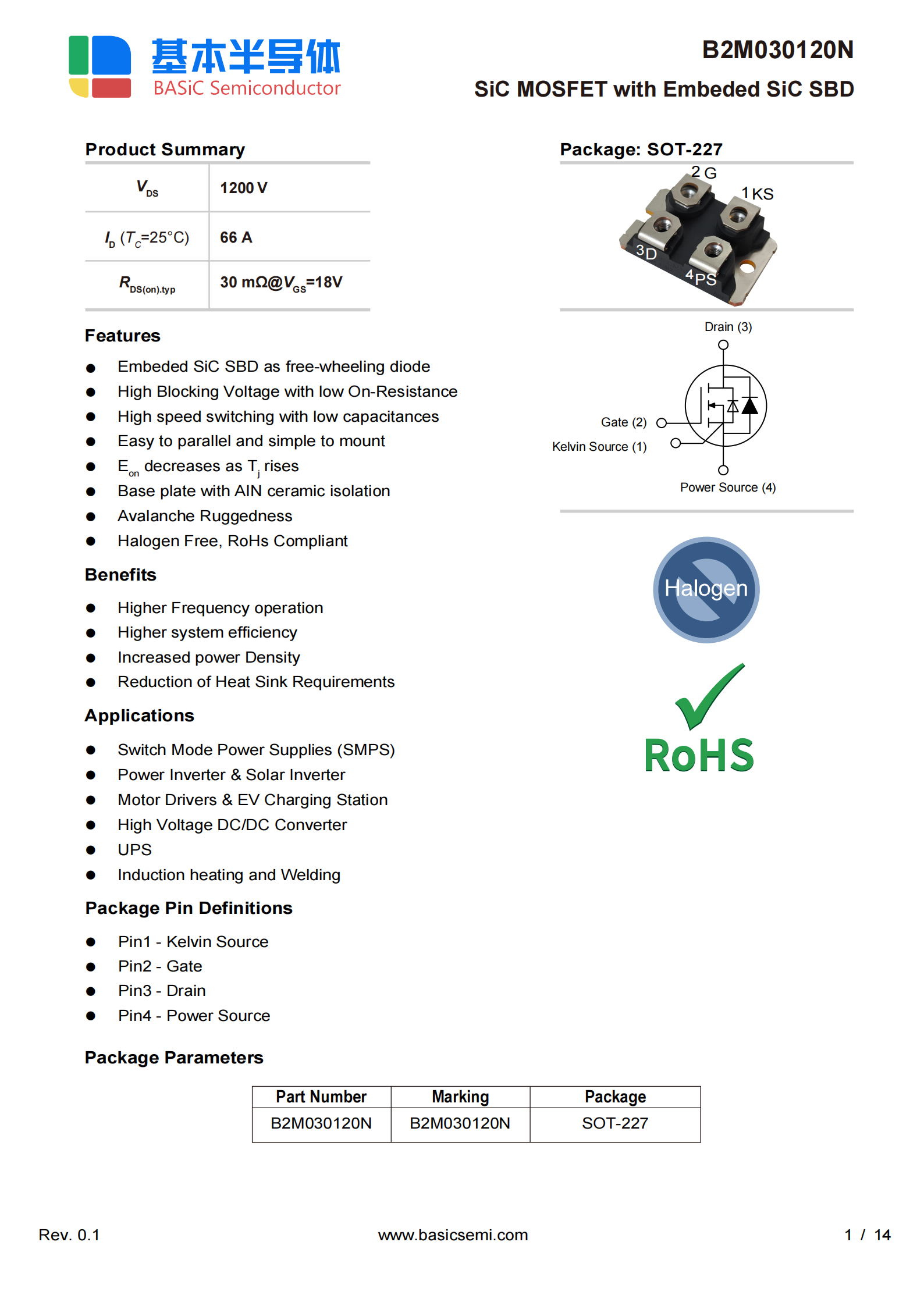

傾佳電子楊茜將從半導體物理學的底層原理出發(fā),對SiC溝槽柵MOSFET進行全方位的深度剖析。我們將探討晶體各向異性對溝道傳輸特性的影響,解構非對稱溝槽(Asymmetric Trench)與雙溝槽(Double Trench)等主流架構的電場屏蔽機制,并深入研究時間依賴性介質擊穿(TDDB)、短路耐受能力(SCWT)以及體二極管雙極性退化等關鍵可靠性失效模式的物理根源。此外,結合基本半導體(BASIC Semiconductor)等行業(yè)領先企業(yè)的最新技術成果與測試數(shù)據(jù),將為理解當前SiC功率器件的技術前沿與未來趨勢提供詳實的理論與實證依據(jù)。

2. SiC溝槽柵結構的物理驅動力與挑戰(zhàn)

要理解溝槽柵SiC MOSFET的可靠性物理,首先必須剖析驅動這一架構演進的物理動因及其引發(fā)的靜電場邊界條件變化。

2.1 晶體各向異性與溝道遷移率物理

4H-SiC作為一種六方晶系材料,具有顯著的各向異性(Anisotropy),這意味著其物理性質(如載流子遷移率、氧化速率等)沿不同晶軸方向表現(xiàn)出顯著差異。這是理解溝槽柵優(yōu)勢的物理起點。

平面柵的物理局限:傳統(tǒng)的平面SiC MOSFET通常在(0001)Si面上生長熱氧化層以形成MOS界面。然而,物理研究表明,在(0001)Si面與SiO2的界面處,在氧化過程中容易產生高密度的碳團簇殘留和界面態(tài)陷阱(Interface Traps, Dit)。這些界面態(tài)在禁帶中捕獲電子,不僅導致閾值電壓(Vth)的不穩(wěn)定性,更通過庫侖散射(Coulomb Scattering)嚴重降低了反型層的電子遷移率(μch)。典型的平面SiC MOSFET溝道遷移率僅為20-40 cm2/V?s,遠低于體材料約900 cm2/V?s的電子遷移率 。在低壓(650V-1200V)器件中,溝道電阻(Rch)在總導通電阻(RDS(on))中占比極高,成為性能瓶頸。

溝槽柵的晶面優(yōu)勢:溝槽架構通過干法刻蝕(如ICP-RIE)在漂移層中挖掘垂直溝槽,使得MOS溝道形成于溝槽的側壁上。通過精確控制溝槽的刻蝕方向,可以使側壁顯露為(112ˉ0) a面或(11ˉ00) m面。研究證實,這些非極性面(Non-polar faces)在氧化后的界面態(tài)密度顯著低于Si面,且表面粗糙度散射較小。這使得溝槽側壁的溝道遷移率可提升至80-100 cm2/V?s甚至更高 。這種基于晶體物理學的優(yōu)化,直接將溝道電阻降低了50%以上,是溝槽柵實現(xiàn)超低Ron,sp的核心物理機制之一。

2.2 幾何結構的重構:消除JFET效應

除了改善遷移率,溝槽柵在幾何結構上的最大貢獻在于消除了平面器件中固有的JFET電阻。

平面器件的JFET瓶頸:在平面結構中,電子流經水平溝道后,必須向下折彎進入漂移區(qū)。為了在高壓阻斷狀態(tài)下保護薄弱的柵氧化層,兩個相鄰的P-body阱必須靠得很近,以形成對柵極下方的靜電屏蔽。這兩個P-body之間的狹窄通道即為JFET區(qū)域。電流流經此處時受到兩側耗盡層的擠壓,產生顯著的JFET電阻(RJFET)。為了提高阻斷電壓,必須縮小JFET寬度,但這反過來又急劇增加了RJFET,形成了Ron與BV(擊穿電壓)之間的強耦合制約 。

垂直流動的自由度:溝槽柵結構將柵極埋入漂移層內部,形成的垂直溝道直接將電子注入漂移層,完全繞過了P-body之間的頸部區(qū)域。物理上,這意味著電流路徑中不再存在橫向收縮的JFET電阻分量 。這一改變不僅直接降低了總電阻,更重要的是它解除了單元尺寸(Cell Pitch)縮小的幾何限制。溝槽器件可以采用極高密度的單元排列(Cell Density),從而大幅降低單位面積的比導通電阻(Ron,sp)。例如,三菱電機和羅姆(Rohm)等廠商的溝槽器件展示了低于2.0 mΩ?cm2的比導通電阻,而同代平面器件通常在3.0-5.0 mΩ?cm2之間 。

2.3 靜電場挑戰(zhàn):介電常數(shù)失配與邊角效應

然而,上帝在打開一扇門的同時,往往會關閉一扇窗。溝槽柵結構引入了一個極其危險的靜電物理問題——電場擁擠(Electric Field Crowding)。

在阻斷狀態(tài)下(VGS

根據(jù)高斯定理的邊界條件,在電介質分界面上,電位移矢量(D=?E)的法向分量是連續(xù)的。即:

?SiCESiC⊥=?SiO2ESiO2⊥

由于4H-SiC的相對介電常數(shù) ?SiC≈9.7,而二氧化硅的相對介電常數(shù) ?SiO2≈3.9,兩者的比值約為2.5。這意味著,如果溝槽底部SiC一側的電場強度達到2 MV/cm(遠未達到SiC的擊穿極限),氧化層內部的電場強度將理論上被放大到:

ESiO2≈2.5×ESiC≈5MV/cm

對于SiO2而言,長期可靠運行的安全電場上限通常被認為是3-4 MV/cm(以保證20年的TDDB壽命)。如果不采取特殊的屏蔽措施,溝槽底部的氧化層將在極短時間內發(fā)生擊穿或因Fowler-Nordheim隧穿電流導致嚴重退化。這就是溝槽柵SiC MOSFET設計的核心矛盾:如何利用溝槽結構帶來的導通優(yōu)勢,同時從物理上解決氧化層電場超標的問題 。

3. 電場屏蔽架構的物理機制與演進

為了解決上述電場擁擠問題,業(yè)界發(fā)展出了多種復雜的屏蔽結構。其核心物理思想均是引入深層的P型摻雜區(qū),利用PN結耗盡層的擴展來“抬升”電勢屏障,從而將高電場峰值從氧化層界面推移至體硅內部。

3.1 非對稱溝槽架構(Asymmetric Trench):英飛凌的可靠性哲學

英飛凌(Infineon)的CoolSiC?系列采用了一種非對稱溝槽結構,這反映了其“可靠性優(yōu)先”的設計哲學 。

結構特征:在這種設計中,溝槽的一側側壁被用作MOS溝道(通常對齊高遷移率的a面),而溝槽的另一側及底部則被一個深P-well(P阱)注入區(qū)所包裹。這個P阱同樣連接至源極。

屏蔽物理機制:深P-well在這里扮演了核心的電場阻擋角色。由于P阱完全覆蓋了溝槽底部的一半并延伸至溝槽下方,它在阻斷狀態(tài)下如同避雷針一般吸引并終結電力線。仿真結果表明,這種非對稱屏蔽結構能將氧化層內的電場強度嚴格限制在安全范圍內,即使在器件承受雪崩擊穿時,電場峰值也位于P-well的曲率半徑處,而非氧化層界面 。

設計權衡:這種設計的代價是犧牲了一半的溝道密度(因為每個微元只有一個側壁導電),從而略微增加了比導通電阻。然而,它換取了極高的柵氧化層可靠性和短路耐受能力,使其在工業(yè)應用中表現(xiàn)出類似IGBT的魯棒性。

3.2 下一代結構前瞻:Fin-MOS與超級結

前沿研究指出了溝槽技術的未來演進方向。Fin-MOS(鰭式場效應晶體管)結構通過在極窄的SiC鰭片側壁形成溝道,并利用深P屏蔽區(qū)完全夾斷鰭片底部的電場,理論上可以將氧化層電場降至幾乎為零,同時極小化Crss 。此外,**超級結(Superjunction)**概念也被嘗試引入溝槽SiC,旨在打破硅極限下的電阻-耐壓折衷關系(Trade-off),盡管目前SiC深層摻雜工藝的難度限制了其商業(yè)化進程 。

4. 可靠性物理深度剖析:溝槽與平面的對決

器件結構的物理差異直接導致了其在極端應力下的失效模式和壽命預測模型的根本不同。以下是對關鍵可靠性指標的深度對比分析。

4.1 柵氧化層可靠性(TDDB):反直覺的物理真相

時間依賴性介質擊穿(TDDB)是評估柵氧化層壽命的核心指標。直覺上,溝槽器件由于底角電場應力,其TDDB壽命似乎應弱于平面器件。然而,大量實測數(shù)據(jù)和物理分析揭示了相反的結論。

本征壽命優(yōu)勢:研究表明,先進的溝槽柵SiC MOSFET(如英飛凌CoolSiC)往往表現(xiàn)出比平面器件更長的本征氧化層壽命 。其物理原因在于:

屏蔽的有效性:如前所述,深P阱或源極溝槽的屏蔽作用極其有效,使得在關斷高壓狀態(tài)下,氧化層承受的電場實際上微乎其微(<1?MV/cm)。

氧化層增厚:為了抵御開通狀態(tài)下的電場應力,溝槽器件通常在溝槽底部和拐角處采用比平面器件更厚(例如50-70nm vs 40-50nm)的氧化層(通常通過沉積工藝而非熱生長)。根據(jù)E=V/d,更厚的氧化層在相同柵壓下承受的電場更低,且更能抵抗Fowler-Nordheim隧穿電子的轟擊 。

測試方法的陷阱:對于溝槽器件的TDDB評估,傳統(tǒng)的**恒壓應力(Constant Voltage Stress, CVS)**測試可能會給出誤導性的樂觀結果。這是因為溝槽氧化層(特別是沉積氧化層)中可能存在較多的電子陷阱。在CVS測試初期,電子被捕獲在氧化層中,形成內建負電場,實際上降低了陽極附近的有效電場,導致漏電流減小,從而延長了實測擊穿時間。為了獲得真實的物理壽命,**恒流應力(Constant Current Stress, CCS)**測試被證明是更準確的方法,因為它強制恒定電流流過氧化層,不受電荷捕獲導致的電場松弛影響 。在150°C下,現(xiàn)代溝槽器件的預測壽命通常超過107小時,遠超汽車級20年的要求 。

4.2 短路耐受能力(SCWT):熱力學的阿喀琉斯之踵

如果說TDDB是溝槽器件的強項,那么短路能力(Short-Circuit Withstand Time)則是其物理上的短板。

能量密度物理:短路發(fā)生時,器件同時承受母線電壓(如800V)和飽和電流(Isat)。溝槽器件由于極高的溝道密度和高跨導(gm),其Isat密度遠高于同規(guī)格的平面器件。這意味著在微秒級的短路脈沖內,溝槽元胞內產生的熱功率密度(P=V×I)是驚人的。

失效模式差異:

平面器件:通常由于熱容量相對較大,能承受更長時間(>5μs甚至>8μs)的短路。其失效模式往往是柵極破裂或鋁金屬層熔化導致的源-漏短路 。

溝槽器件:由于熱生成極快且熱容小,其SCWT通常僅為2-3 μs(1200V器件)。其失效模式更為復雜,除了熱失控(Thermal Runaway)外,還常見軟失效(Soft Failure)。軟失效是指在器件徹底燒毀前,柵氧化層因高溫和高電場協(xié)同作用(熱電子注入)而發(fā)生局部損傷,導致柵極漏電流(IGSS)急劇增加,柵壓無法維持,最終導致器件關斷失效或特性漂移 。

結構對比:非對稱溝槽(Asymmetric)由于擁有較大的P-well體積,相比雙溝槽(Double Trench)具有稍大的熱容,因此在SCWT上表現(xiàn)出微弱優(yōu)勢(例如多承受0.5-1 μs),但這并不改變其整體短路能力弱于平面的物理事實 。這要求驅動電路必須具備極快(<2 μs)的去飽和檢測與保護能力。

5. 動態(tài)穩(wěn)定性與寄生參數(shù)效應

除了靜態(tài)可靠性,溝槽柵獨特的寄生參數(shù)特性也深刻影響著動態(tài)開關過程的可靠性。

5.1 米勒電容與開關震蕩

如前所述,屏蔽結構大幅降低了Crss。雖然這降低了開關損耗,但也使得Ciss/Crss比率變得極高。

物理影響:極小的Crss意味著柵極對漏極電壓變化的耦合極弱,這本是好事(抗米勒效應能力強)。然而,過快的dV/dt(可達100 V/ns以上)配合極小的寄生電容,極易在柵極回路中激起高頻寄生震蕩。

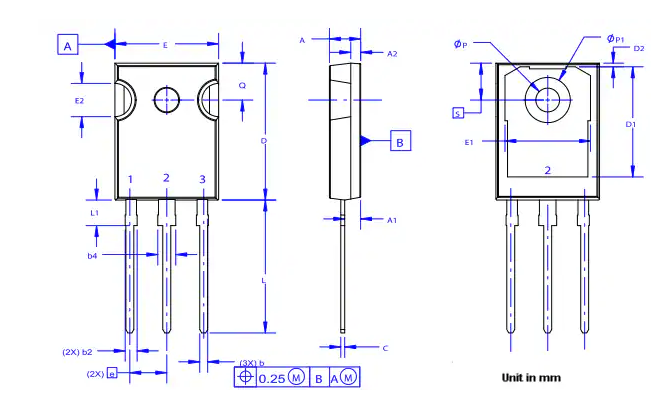

應用挑戰(zhàn):在半橋拓撲中,這種震蕩可能導致柵極電壓瞬時超過正向或負向的安全極限(VGS,max),造成柵氧化層累積損傷。此外,溝槽器件的高跨導特性使得其對柵極噪聲極為敏感。因此,應用端往往需要采用開爾文源極(Kelvin Source)封裝,并精心設計柵極驅動電阻(Rg)和PCB布局以抑制震蕩 。

5.2 閾值電壓不穩(wěn)定性(BTI)

偏置溫度不穩(wěn)定性(BTI)是指在高溫和柵偏壓下Vth發(fā)生漂移的現(xiàn)象。

晶面依賴性:溝槽側壁的不同晶面具有不同的氧化速率和界面態(tài)密度。雖然a面遷移率高,但其界面態(tài)分布與Si面不同。研究發(fā)現(xiàn),在交流(AC)動態(tài)應力下,溝槽器件的Vth漂移往往比直流(DC)應力下更復雜,這是因為界面陷阱在快速開關過程中不斷捕獲和釋放電荷。

對比分析:雖然平面器件的Dit絕對值較高,但經過數(shù)十年的工藝優(yōu)化(如NO退火),其Vth漂移行為已相對可控。溝槽器件由于涉及多個晶面的復雜氧化工藝,其BTI特性(特別是負偏壓下的NBTI)仍是各廠商工藝控制的重點 。

6. 工業(yè)界案例分析:基本半導體(BASIC Semiconductor)的技術路線

通過分析基本半導體的產品與技術文檔,我們可以看到一家典型的主流廠商如何在平面與溝槽之間進行戰(zhàn)略布局與技術優(yōu)化。

6.1 B3M技術路線:極致優(yōu)化的平面柵

根據(jù)提供的資料,基本半導體的B3M(第三代)技術被明確為一種先進的**平面柵(Planar Gate)**技術 。這反映了一種務實的工業(yè)策略:在溝槽工藝良率和復雜性完全成熟之前,通過挖掘平面結構的物理潛力來抗衡溝槽器件。

性能對標:B3M系列通過優(yōu)化JFET區(qū)域摻雜和縮減單元尺寸,實現(xiàn)了極具競爭力的性能。例如,其1200V分立器件實現(xiàn)了低至13.5 mΩ的導通電阻 ,車規(guī)級模塊(Pcore系列)甚至達到了1.7 mΩ 。這表明,通過精細的工藝控制,平面器件在Ron,sp上仍有與早期溝槽器件一戰(zhàn)的實力。

FOM提升:雖然具體百分比數(shù)據(jù)在摘要中未詳盡,但通常從二代到三代平面器件,通過減薄漂移層和優(yōu)化柵極設計,品質因數(shù)(FOM = Ron×Qg)通常能提升20%-30%以上,從而縮小與溝槽器件在開關損耗上的差距。

6.2 可靠性驗證:DGS與DRB實測

基本半導體針對B3M系列進行的可靠性測試報告(編號RC20251120-1)提供了極具價值的實證數(shù)據(jù),驗證了其在動態(tài)應力下的魯棒性 。

6.3 模塊級優(yōu)化

在模塊層面(如ED3、E2B系列),基本半導體通過封裝技術進一步彌補芯片層面的物理限制 。例如,采用高性能的Si3N4(氮化硅)AMB陶瓷基板,利用其高熱導率和高機械強度來應對SiC器件高功率密度帶來的熱應力。

7. 結論與展望

通過對SiC溝槽柵物理與可靠性的深度剖析,本報告得出以下核心結論:

物理優(yōu)勢的確立:溝槽柵架構憑借垂直溝道對JFET電阻的消除和對高遷移率晶面的利用,在導通效率(Ron,sp)和開關速度(低Crss)上確立了對平面柵的物理優(yōu)勢。這是SiC技術發(fā)展的必然方向。

可靠性的結構解:電場擁擠不再是溝槽器件的致命傷。通過**雙溝槽(Double Trench)或非對稱溝槽(Asymmetric Trench)**等深P屏蔽結構,電場峰值已被成功移出柵氧化層。現(xiàn)代溝槽器件的柵氧化層本征壽命已能滿足汽車級與工業(yè)級嚴苛要求。

短路能力的物理短板:由于極高的電流密度和較小的熱容,溝槽器件的短路耐受時間(SCWT)物理上短于平面器件(約2-3 μs vs >5 μs)。這要求系統(tǒng)設計必須匹配更靈敏的驅動保護方案,而非單純依賴器件本身的魯棒性。

技術路線的共存:平面柵技術并未終結。如基本半導體B3M所示,經過極致優(yōu)化的平面器件在可靠性(特別是短路能力和工藝成熟度)和成本上仍具有強大競爭力。未來市場將呈現(xiàn)分化:溝槽柵將統(tǒng)治對效率和功率密度要求極致的電動汽車主驅市場,而先進平面柵將在光伏、儲能和工業(yè)驅動等對魯棒性和成本敏感的領域繼續(xù)占據(jù)重要地位。

融合趨勢:未來的器件結構將趨向融合。我們已經看到“溝槽輔助平面”結構的出現(xiàn),以及溝槽器件通過調整單元密度來換取短路能力的嘗試。物理學的邊界正在被工程師的創(chuàng)造力不斷拓寬,SiC功率器件正步入一個性能與可靠性完美平衡的黃金時代。

8. 數(shù)據(jù)圖表匯總

表1:SiC柵極架構物理特性對比

表2:基本半導體B3M可靠性驗證數(shù)據(jù)摘要

測試項目

測試條件

物理意義與結果解讀

動態(tài)柵極應力 (DGS)

VGS=?10/+22V, f=250kHz 300h (1.08×1011 次循環(huán)) dVGS/dt>0.6V/ns

物理意義:高頻開關會激活慢響應的界面陷阱,導致Vth漂移。此測試頻率極高(250kHz),嚴苛考驗了柵氧化層界面的穩(wěn)定性。

結果:Pass。證明了B3M的平面柵氧化工藝在抑制界面態(tài)捕獲方面達到了極高水準,解決了平面器件常見的動態(tài)Vth漂移問題。

動態(tài)反偏應力 (DRB)

VDS=960V, f=50kHz 556h (1011 次循環(huán)) dv/dt≥50V/ns

物理意義:模擬逆變器實際工況下的高dv/dt沖擊。高dv/dt會產生位移電流,若屏蔽不當可能導致寄生BJT導通(Latch-up)或邊緣終端場強超標。結果:Pass。證明了器件的JFET區(qū)和終端結構設計能有效抑制dv/dt引發(fā)的失效,且屏蔽結構有效阻斷了米勒反饋導致的誤導通。

特性參數(shù)

平面柵 (Planar Gate)

非對稱溝槽 (Asymmetric Trench)

雙溝槽 (Double Trench)

物理主導機制

導電晶面

Si-face (0001)

a-plane (112ˉ0)

a-plane / m-plane

晶體各向異性導致遷移率差異 (μch)

JFET電阻

存在 (顯著占Ron)

消除

消除

垂直電流路徑消除了橫向頸部收縮

阻斷電場分布

應力集中在P-well曲率處

深P-well屏蔽,氧化層場強極低

源極溝槽耗盡層Pinch-off屏蔽

高斯定理與PN結耗盡區(qū)成形

米勒電容 (Crss)

中等/較高

低

極低

屏蔽結構實現(xiàn)了柵極與漏極電位的解耦

短路耐量 (SCWT)

高 (>5μs)

低 (2?3μs)

低 (2?3μs)

電流密度與有效熱容體積的反比關系

失效模式

柵極破裂 / 硬失效

熱失控 / 軟失效 (漏電增加)

熱失控 / 軟失效

局部過熱導致的氧化層退化機制不同

測試項目

條件

持續(xù)時間/循環(huán)

結果

物理意義

DGS

VGS=?10/+22V, 250kHz

1.08×1011 Cycles

Pass

驗證高頻開關下的界面態(tài)穩(wěn)定性

DRB

VDS=960V, 50kHz, dv/dt≥50V/ns

1011 Cycles

Pass

驗證阻斷狀態(tài)下的電場屏蔽與抗干擾能力

HTRB

Tj=175°C, VDS=1200V

1000 Hours

Pass

驗證邊緣終端與漏電流穩(wěn)定性

HTGB

Tj=175°C, VGS=22V/?10V

1000 Hours

Pass

驗證柵氧化層的TDDB壽命與Vth穩(wěn)定性

-

MOSFET

+關注

關注

151文章

9646瀏覽量

233454 -

場效應管

+關注

關注

47文章

1292瀏覽量

71321 -

逆變器

+關注

關注

303文章

5160瀏覽量

216534 -

SiC

+關注

關注

32文章

3720瀏覽量

69375 -

半導體器件

+關注

關注

12文章

807瀏覽量

34119

發(fā)布評論請先 登錄

什么是高可靠性?

派恩杰深度解讀SiC MOSFET柵氧可靠性問題

三菱電機推出四款全新溝槽柵型SiC-MOSFET裸芯片

三菱電機SiC MOSFET的可靠性測試

安森美SiC MOSFET NTBG025N065SC1:高效能與可靠性的完美結合

探索 onsemi NVHL015N065SC1 SiC MOSFET:高效能與可靠性的完美結合

CoolSiC? 2000V SiC 溝槽柵MOSFET定義新能源應用中功率密度增強的新基準

B2M030120N SiC碳化硅MOSFET完美契合半導體射頻電源對效率、可靠性和緊湊化的嚴苛需求

理想汽車自研SiC團隊成果:提高SiC MOSFET可靠性的方式

SiC MOSFET的溝槽柵(Trench)物理與可靠性研究

SiC MOSFET的溝槽柵(Trench)物理與可靠性研究

評論