降低成本的設計注意事項

設計人員一直在尋找降低系統成本的方法,同時繼續保持或增強功能。與此同時,市場對擴展功能和更短產品周期的需求,也給MCU行業帶來了新的挑戰。平衡這些相互沖突的需求需要創新的系統設計方法。

降低成本的一種有效策略是通過減少元件數量和使用更具成本效益的IC來簡化系統架構。但是,任何更改都必須確保系統功能保持不變,理想情況下還應有所提升。

降低系統成本的挑戰

降低成本的一種方法是消除外部元件,例如用片上振蕩器代替外部振蕩器,或者用嵌入式數據閃存代替外部EEPROM。這可以通過減少元件數量和電路板尺寸來降低系統成本。此外,它還釋放了額外的引腳,可以將其重新分配給其他功能。

但是,這些優化帶來了技術挑戰。例如,UART通信通常需要時鐘頻率誤差在2%到3%以內,以確保可靠的數據傳輸。如果一個通信設備的頻率誤差為2%,則MCU必須保持1%或更低的誤差范圍,以保持在3%的總限制內。許多低端MCU并未配備此類高精度振蕩器,即使數據表中提供了規格,它們也可能需要外部電阻器進行調諧。同樣,具有類似EEPROM的嵌入式存儲器的低端MCU也沒有得到廣泛應用。

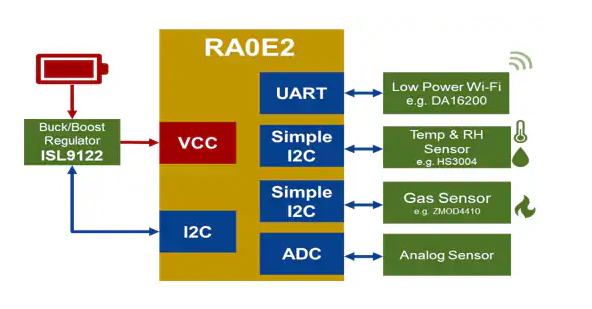

RA0E2 MCU的優勢

RA0E2 MCU有效地解決了這些挑戰。它具有一個片上高速振蕩器,在所有工作溫度(-40°C至125°C)下保證±1%最大誤差。此外,它還集成了Data Flash,無需外部EEPROM。這些特性可以減少元件數量,從而降低系統成本并簡化設計。此外,釋放的引腳可用于GPIO或其他功能,在相同的封裝尺寸內提供更大的靈活性。

圖1:降低系統BOM成本

快速原型設計

為了加速RA0E2 MCU的開發,我們提供了快速原型板(FPB)。該評估板旨在簡化評估過程,使設計人員能夠更高效地開發和測試原型產品。

圖 2:RA0系列快速原型開發板(FPB)

總結

RA0E2 MCU系列提供有價值的功能,可幫助設計人員在不犧牲性能的情況下降低成本。RA0系列與之前發布的RA0E1 MCU一起,提供一系列ROM大小(32kB至128kB)和引腳數選項(16至64引腳),使其適用于各種應用。此外,FPB-RA0E2評估板為快速原型設計提供了經濟實惠的解決方案,進一步簡化了開發過程。

圖 3:RA0E2組產品陣容

有關評估板的更多信息,請點擊閱讀原文查看

(有關RA0E1和RA0E2特性和優勢的更多詳細信息,您可識別下方二維碼或復制鏈接至瀏覽器中打開查閱)

RA0E1

https://www.renesas.cn/zh/products/ra0e1

RA0E2

https://www.renesas.cn/zh/products/ra0e2

需要技術支持?

如您在使用瑞薩MCU/MPU產品中有任何問題,可識別下方二維碼或復制網址到瀏覽器中打開,進入瑞薩技術論壇尋找答案或獲取在線技術支持。

-

mcu

+關注

關注

147文章

18923瀏覽量

397966 -

振蕩器

+關注

關注

28文章

4172瀏覽量

142872 -

瑞薩

+關注

關注

37文章

22481瀏覽量

90845

原文標題:選擇瑞薩入門級MCU以降低系統成本

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RA0E2微控制器:低功耗設計的理想之選

Renesas FPB-RA0E2 v1快速原型開發板使用指南

【瑞薩RA6E2地奇星開發板試用】使用`RA6E2`驅動 `ESP8266 WiFi模塊`,調試AT指令。

【瑞薩RA6E2】瑞薩E2S軟件安裝過程,等待過程玩下97_e2 studio_ZGZZ

【瑞薩RA6E2】開箱測試報告_ZGZZ

新品 | RA0系列MCU喜添新成員RA0E2,0.25uA超低功耗待機,支持5v、125c

使用瑞薩電子RA0E2 MCU降低系統設計成本

使用瑞薩電子RA0E2 MCU降低系統設計成本

評論