PCI Express是一種使用時鐘數據恢復(CDR)技術的高速串行I/O互連機制。PCI Express第一代規范規定的線速率為每通道2.5Gbps,可以讓您建立具備單通道(x1)鏈路2Gbps(經8B/10B編碼)直至32通道64Gbps吞吐量的應用。這樣就能在保持或改進吞吐量的同時,顯著減少引腳數量。另外,還可以減小PCB的尺寸、降低印制線和層的數量,并簡化布局和設計。引腳數量減少,也就意味著噪聲和電磁干擾(EMI)降低。CDR消除了寬并行總線中普遍存在的時鐘-數據歪斜問題,簡化了互連實現。

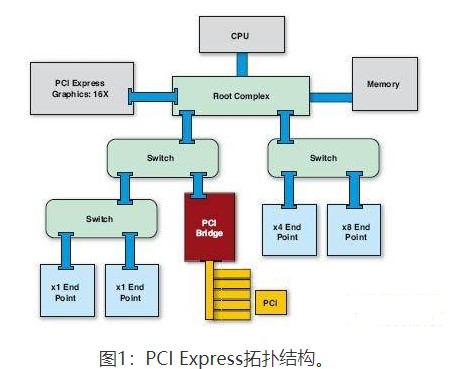

PCI Express互連架構主要針對基于PC的系統,但就像PCI一樣,PCI Express也很快轉移到其他系統類型,如嵌入式系統。它規定了三種類型器件:根聯合體(root complex)、交換器件和端點(圖1)。根聯合體大致等同于PCI主機,CPU、系統存儲器和圖形控制器與之相連接。由于PCI Express的點對點特性,必須使用交換器件來增加系統功能的數量。PCI Express交換器件將上游端的根聯合體器件連接到下游端的端點。

端點功能類似于PCI/PCI-X器件。最常用的端點器件有以太網控制器或存儲主機總線適配器(HBA)。FPGA最常用于數據處理和橋接功能,所以其最大目標功能就是端點。FPGA實現非常適合于視頻、醫療影像、工業、測試和測量、數據采集和存儲應用。

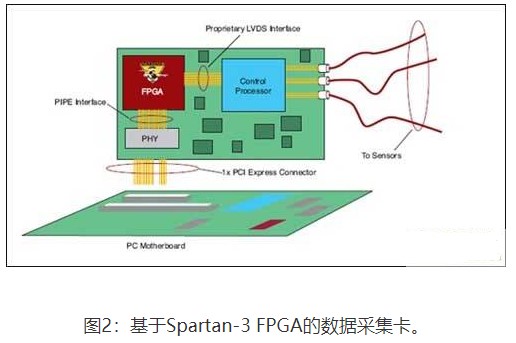

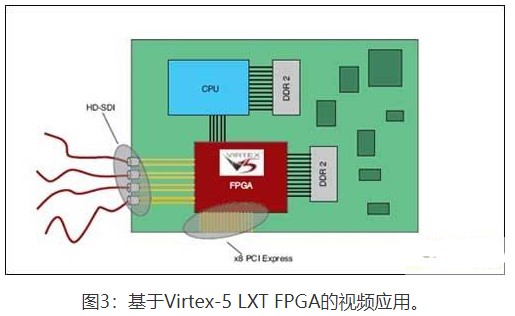

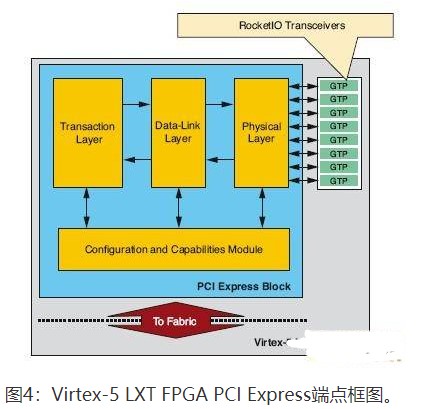

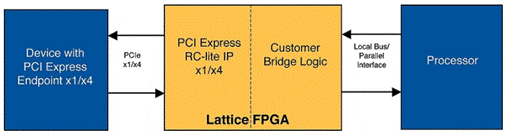

PCI-SIG(PCI特別興趣小組)采用的PCI Express規范規定每個PCI Express器件使用三個不同的協議層:物理層、數據鏈路層和事務層。您可以使用單芯片或雙芯片解決方案來構建PCI Express端點。例如,使用Xilinx Spartan-3器件之類的低成本FPGA,您可以用商用離散PCI Express PHY(圖2)來構建數據鏈路和事務層。此選項最適合于x1通道應用,如總線控制器、數據采集卡和提高性能的PCI32/33器件。或者,您可以使用類似Virtex-5 LXT或SXT FPGA的單芯片解決方案,它們具備集成的PCI Express PHY。此選項最適合于通訊或高清晰音頻/視頻端點器件(圖3),它們對性能的要求更高:x4(8Gbps吞吐量)鏈路或x8(16Gbps吞吐量)鏈路。

在選擇一種技術來實現PCI Express設計之前,必須仔細考慮應用的IP選擇、鏈路效率、兼容性測試及資源可用性。本文中,我們將簡要介紹使用最新的FPGA技術構建單芯片x4和x8通道PCI Express設計的一些因素。

IP的選擇

作為設計人員,您可以選擇構建自己的軟IP或者向第三方或FPGA供應商購買IP。構建自己的IP的難題在于,您不光得從零開始創建設計,還得擔心驗證、批準、兼容性和硬件評估等環節。向第三方或FPGA供應商購買的IP,已經過所有嚴格的兼容性測試和硬件評估,可以即插即用。如果使用商用的、已驗證的兼容性PCI Express接口,您可以把精力集中在設計中最有附加值的部分:用戶應用。使用軟IP的難題在于應用的資源可用性。軟IP核的PCI Express MAC層、數據鏈路層和事務層通過可編程架構實現,因此您必須特別注意剩余的Block RAM、查找表和架構資源的數量。

另一選擇是使用最新技術的FPGA。Virtex-5 LXT和SXT的專用門電路(圖4)中實現了集成x8通道PCI Express控制器。這種實現極具優勢,因為設計是在硬硅片中實現的,所以需要的FPGA邏輯資源數量達到了最小。例如,在Virtex-5 LXT FPGA中,一個x8通道軟IP核可占用多達10,000個邏輯單元,而硬實現只需要大約500個邏輯單元,多數用于接口。這樣的資源節省有時候能允許您選擇更小的器件,而器件越小通常就會越便宜。集成實現通常具有更高的性能、更寬的數據通路,并且可通過軟件配置。

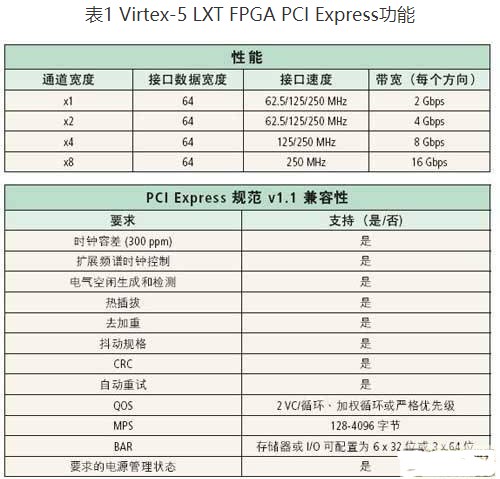

軟IP實現的另一難題是功能的數量。通常,此類核僅實現滿足性能或兼容性目標規范所要求的最少功能。相反,硬IP可以支持基于客戶要求的全面功能列表,并提供完全的兼容性(表1),且不存在嚴重的性能或資源相關的問題。

延遲問題

盡管PCI Express控制器的延遲不會對總體系統延遲有很大的影響,但卻會影響接口的性能。使用較窄的數據通路有助于減少延遲。

對PCI Express來說,延遲就是發送包并穿過物理層、邏輯層和事務層接收包所需的周期數。典型的x8通道PCI Express端點的延遲為20-25周期,在250MHz下對應80-100ns的延遲時間。如果使用128位的數據通路實現接口來簡化時序(如125MHz),延遲會加倍為160-200ns。在最新的Virtex-5 LXT和SXT器件中,無論是軟IP實現還是硬IP實現,都采用250MHz下的64位數據通路實現x8。

鏈路效率

鏈路效率是延遲、用戶應用設計、有效載荷大小和額外開銷的函數。隨著有效載荷大小(通常稱為最大有效載荷)的增加,有效鏈路效率也會增加。這是由包的額外開銷固定不變這一事實造成的;如果有效載荷大,效率就提高。一般情況下,256字節的有效載荷可提供93%的理論效率(256有效載荷字節+12包頭字節+8幀字節)。盡管PCI Express允許的包大小可達4KB,但如果有效載荷大小大于256或512字節,大多數系統的性能都無法提高。由于鏈路協議額外開銷(ACK/NAK、包重新發送)和流程控制協議,在Virtex-5 LXT FPGA中實現x4或x8PCI Express的鏈路效率為88-89%。

利用FPGA實現可以更好地控制鏈路效率,因為它允許您選擇與端點實現對應的接收緩沖器尺寸。如果鏈接雙方不是采用相同的方式實現數據通路,則二者的內部延遲會不同。例如,如果一號鏈接方使用64位、250MHz實現,延遲為80ns,而二號鏈接方使用128位、125MHz實現,延遲為160ns,該鏈路的組合延遲即為240ns。現在,如果一號鏈接方的接收緩沖器設計成160ns的延遲(即期待其鏈接對方也是64位、250MHz實現),那么鏈路效率就會降低。如果采用ASIC實現,就不可能改變接收緩沖器的尺寸,效率損失將是實實在在的,而且是永久性的。

用戶應用程序設計也會對鏈路效率有所影響。用戶應用程序必須設計成定期排空PCI Express接口的接收緩沖器,并保持發送緩沖器時刻充滿。如果用戶應用程序不立即使用接收的包(或者不立即響應發送請求),無論接口的性能如何,總鏈路效率都會受到影響。

使用某些處理器設計時,如果處理器不能執行大于1 DWORD的突發,則需要實現一個DMA控制器。這將造成鏈路利用不充分,效率不佳。大多數嵌入式CPU可以發送長于1 DWORD的突發,所以通過良好的FIFO設計就可以有效地管理這些設計的鏈路效率。

PCI Express兼容性

兼容性是經常被遺漏和低估的重要細節。如果要構建必須與其他應用和設備一起工作的PCI Express應用,則必須確保設計的兼容性。

兼容性不只針對IP,而是針對整個解決方案,包括IP、用戶應用、半導體器件和硬件板。如果整個解決方案已經過PCI-SIG PCI Express兼容性工作組的驗證,就能很好地保證您設計的PCI Express部分會一直有效工作。

本文結論:

PCI Express已替代PCI成為事實上的系統互連標準,并且已從PC轉移到其他系統市場,包括嵌入式系統設計。FPGA非常適合于構建PCI Express端點器件,因為它允許您創建帶有用戶所需的附加定制功能的兼容性PCI Express器件。

類似Virtex-5 LXT和SXT系列的新65nm FPGA完全符合PCI Express v1.1規范,并為用戶應用提供廣泛的邏輯和器件資源。使用外部PHY的Spartan-3系列FPGA提供了低成本解決方案。這些因素,加上內在的可編程邏輯優勢(靈活性、可再編程性和低風險)使FPGA成為PCI Express的最佳平臺。

-

FPGA

+關注

關注

1660文章

22415瀏覽量

636541 -

控制器

+關注

關注

114文章

17795瀏覽量

193367 -

存儲器

+關注

關注

39文章

7739瀏覽量

171699

發布評論請先 登錄

基于PCI Express的數據采集卡設計

PCI Express Endpoint Master DMA

PCI Express Endpoint Master DMA設計實現

PCI Express標準技術性概述

PC通過PCI Express與FPGA通信

PCI Express的基本工作原理

針對可編程PCI Express解決方案的評估方法

采用中檔FPGA設計面向PCI Express系統的解決方案

IDT宣布推出PCI Express Gen2 系統互連交換

基于FPGA的PCI+Express傳輸設計

FPGA中實施PCI Express橋接解決方案

采用用FPGA構建基于PC系統的PCI Express互連架構平臺

采用用FPGA構建基于PC系統的PCI Express互連架構平臺

評論