18.1.2

協議層

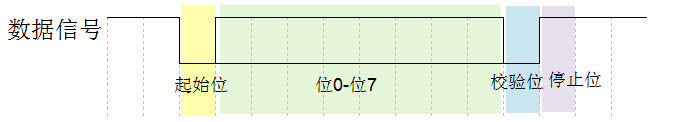

串口通訊的數據包由發送設備通過自身的TXD接口傳輸到接收設備的RXD接口。在串口通訊的協議層中,規定了數據包的內容,它由啟始位、主體數據、校驗位以及停止位組成,通訊雙方的數據包格式要約定一致才能正常收發數據,其組成見圖 19_6。

圖 19-6 串口數據包的基本組成

18.1.2.1

波特率

本章中主要講解的是串口異步通訊,異步通訊中由于沒有時鐘信號(如前面講解的DB9接口中是沒有時鐘信號的),所以兩個通訊設備之間需要約定好波特率,即每個碼元的長度,以便對信號進行解碼,圖19_6中用虛線分開的每一格就是代表一個碼元。常見的波特率為4800、9600、115200等。

18.1.2.2

通訊的起始和停止信號

串口通訊的一個數據包從起始信號開始,直到停止信號結束。數據包的起始信號由一個邏輯0的數據位表示,而數據包的停止信號可由0.5、1、1.5或2個邏輯1的數據位表示,只要雙方約定一致即可。

18.1.2.3

有效數據

在數據包的起始位之后緊接著的就是要傳輸的主體數據內容,也稱為有效數據,有效數據的長度常被約定為5、6、7或8位長。

18.1.2.4

數據校驗

在有效數據之后,有一個可選的數據校驗位。由于數據通信相對更容易受到外部干擾導致傳輸數據出現偏差,可以在傳輸過程加上校驗位來解決這個問題。校驗方法有奇校驗(odd)、偶校驗(even)、0校驗(space)、1校驗(mark)以及無校驗(noparity)。

奇校驗要求有效數據和校驗位中“1”的個數為奇數,比如一個8位長的有效數據為:01101001,此時總共有4個“1”,為達到奇校驗效果,校驗位為“1”,最后傳輸的數據將是8位的有效數據加上1位的校驗位總共9位。

偶校驗與奇校驗要求剛好相反,要求幀數據和校驗位中“1”的個數為偶數,比如數據幀:11001010,此時數據幀“1”的個數為4個,所以偶校驗位為“0”。

0校驗是不管有效數據中的內容是什么,校驗位總為“0”,1校驗是校驗位總為“1”。

18.2

SCI簡介

SCI(Serial Communications Interface),意為串行通信接口,是相對與并行通信的概念,是串行通信技術的一種總稱,包括了UART,SPI等串行通信技術。RA6M5的SCI模塊是一個有10個通道的異步/同步串行接口,RA4M2有6個通道,RA2L1有5個通道。

SCI模塊包含如下功能(根據具體型號有所不同):

UART

8位時鐘同步接口

簡易IIC(只能用作主機)

簡易SPI

智能卡接口(符合ISO/IEC 7816-3國際標準)

曼徹斯特接口

增強的串行接口

另外,RA6M5的SCI0、SCI3~SCI9有獨立的FIFO緩沖區;RA4M2的SCI0、SCI3、SCI4、SCI9有獨立的FIFO緩沖區;RA2L1僅SCI0有獨立的FIFO緩沖區。

18.3

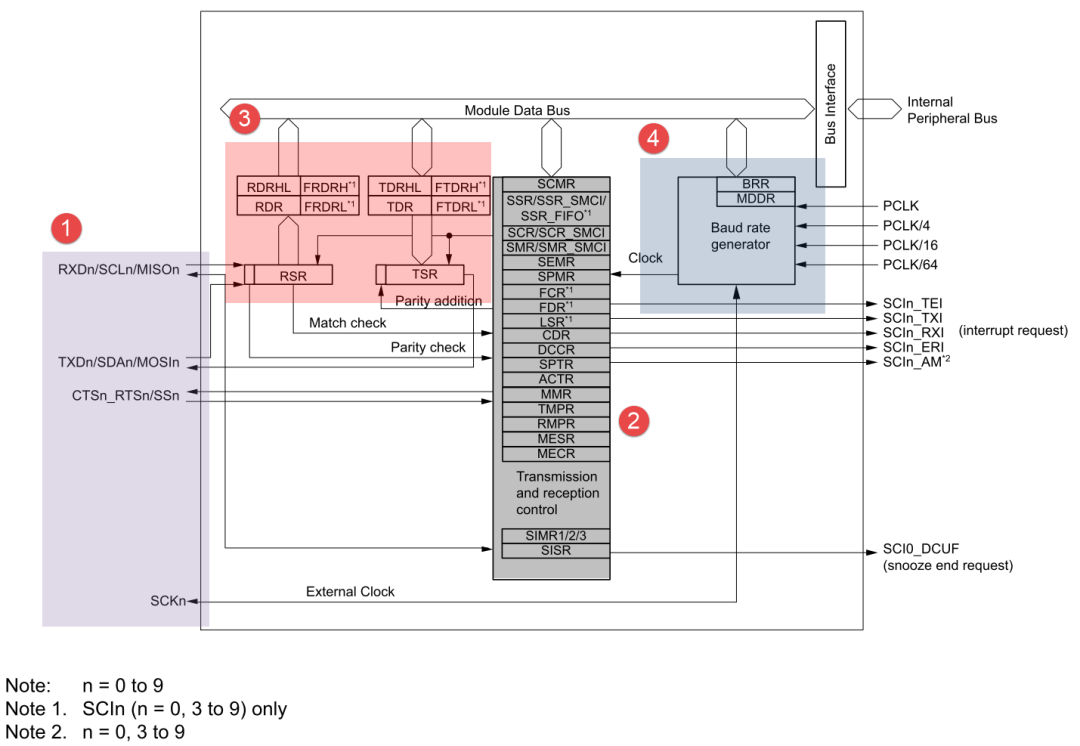

SCI的結構框圖

以RA6M5為例,SCI的結構框圖如下圖所示。接下來我們大致地研究一下它的結構和功能。

18.3.1

功能引腳

見圖中標注①處。

RXDn/SCLn/MISOn:

RXDn:UART接收數據輸入。

SCLn:I2C時鐘信號輸入或輸出。

MISOn:SPI主機信號輸入,從機信號輸出。

TXDn/SDAn/MOSIn:

TXDn:UART發送數據輸出。

SDAn:I2C數據輸入或輸出。

MOSIn:SPI從機信號輸入,主機信號輸出。

SSn/CTSn_RTSn:

SSn:片選信號輸入,低電平有效。

CTSn_RTSn:清除以發送(Clear to Send)或請求以發送(Request to Send)。低電平有效。如果使能RTS流控制,當UART接收器準備好接收新數據時就會將RTS變成低電平;當接收寄存器已滿時,RTS將被設置為高電平。如果使能CTS流控制,發送器在發送下一幀數據之前會檢測CTS引腳,如果為低電平,表示可以發送數據,如果為高電平則在發送完當前數據幀之后停止發送,該引腳只適用于硬件流控制。

CTSn(n = 0,3 to 9):

清除以發送(Clear to Send),適用于硬件流控制。

SCKn:

時鐘輸出或輸入引腳,適用于同步通信。

18.3.2

發送和接收控制

見圖中標注②處。

通信模式和通信參數設置。

FIFO模式設置。

波特率生成器的時鐘輸入選擇。

18.3.3

數據寄存器和移位寄存器

見圖中標注③處。

RSR接收移位寄存器將RXDn引腳接收到的串行數據轉為并行數據。當接收到一幀數據,數據會被自動傳入RDR/RDRHL或FRDRHL寄存器(在FIFO模式下),并允許RSR繼續接收更多數據,CPU無法直接訪問RSR。

TSR傳輸移位寄存器用于傳輸串行數據。要進行數據傳輸,SCI首先自動將數據從TDR/TDRHL或FTDRHL寄存器(在FIFO模式下)傳入到TSR中,然后將數據發送到TXDn引腳,CPU無法直接訪問TSR。

18.3.4

波特率發生器

見圖中標注④處。

用于控制波特率,具體由BRR(Bit Rate Rigister),MDDR(Modulation Duty Register)和SMR(Serial Mode Register)寄存器控制。SMR在這里對波特率生成器的輸入時鐘進行選擇,可以選擇PCLK,PCLK/4,PCLK/16,PCLK/64,即PCLK/4n(n=0-3)。

-

接口

+關注

關注

33文章

9538瀏覽量

157159 -

串口通訊

+關注

關注

2文章

266瀏覽量

26403 -

波特率

+關注

關注

2文章

320瀏覽量

35586

原文標題:串口通信協議層&SCI簡介————瑞薩RA系列FSP庫開發實戰指南(45)

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

串行通信接口的結構和功能

串行通信接口的結構和功能

評論