在電子設備的設計中,晶振作為提供穩定時鐘信號的關鍵元件,其選型的正確性直接關系到整個系統的性能與穩定性。而在晶振選型過程中,激勵電平與頻差之間的微妙平衡常常被工程師們所忽視,然而這一細節卻可能對電路的正常運行產生深遠影響。

激勵電平:晶振穩定工作的關鍵動力

激勵電平,又稱激勵功率或驅動電平,主要針對無源晶振而言。它是指施加在石英晶片上的電流所對應的功率參數,代表著驅動晶振(振蕩電路)所需的功率大小,單位通常為微瓦(μW)。以常見的無源貼片晶振為例,其激勵功率設計參數一般為10μW,最大值可達100μW。

激勵電平對晶振性能有著至關重要的影響。當激勵電平過大時,晶振內部的石英晶片會因過度驅動而產生額外的機械應力與熱量。這不僅可能導致晶振的頻率發生漂移,偏離其標稱頻率,影響電路的時序精度,還會加速晶振的老化,大幅縮短其使用壽命,嚴重時甚至可能直接損壞晶振,致使整個電路系統癱瘓。

相反,若激勵電平過小,晶振可能無法獲得足夠的能量來維持穩定的振蕩,導致振蕩幅度不足,容易受到外界干擾的影響,出現停振或頻率抖動等問題,同樣無法為電路提供穩定可靠的時鐘信號。

在實際電路設計中,可通過調整電路中的串聯電阻Rd來調節激勵電平。當需要降低激勵電平時,可適當增大Rd的阻值,從而減小流經晶振的電流,降低激勵功率;反之,若要提高激勵電平,則減小Rd的阻值。但需要注意的是,這種調整并非無限制的,必須在晶振所允許的激勵電平范圍內進行操作,以確保晶振的正常工作。

頻差:決定系統精度的核心指標

頻差是衡量晶振輸出頻率準確性的關鍵指標,它反映了晶振在實際工作中的頻率與標稱頻率之間的偏差程度,通常以百萬分之幾(ppm)來表示。晶振的頻差主要包括調整頻差和溫度頻差等。

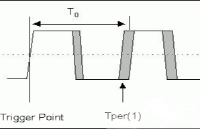

調整頻差是指在25℃基準溫度下,晶振工作頻率相對于標稱頻率所允許的偏差。例如,在石英晶體諧振器的規格書中,常見到調整頻差標注為±30ppmmax,這意味著在25℃時,該晶振的實際工作頻率與標稱頻率的偏差最大不會超過±30ppm。

溫度頻差則是由于環境溫度變化而導致的晶振頻率漂移。晶振的頻率會隨著溫度的波動而發生變化,不同類型的晶振對溫度的敏感程度各異。一般來說,普通的石英晶體諧振器受溫度影響較大,而溫補晶振(TCXO)和恒溫晶振(OCXO)等則通過特殊的溫度補償或恒溫控制技術,能夠有效減小溫度對頻率的影響,在較寬的溫度范圍內保持較高的頻率穩定性。

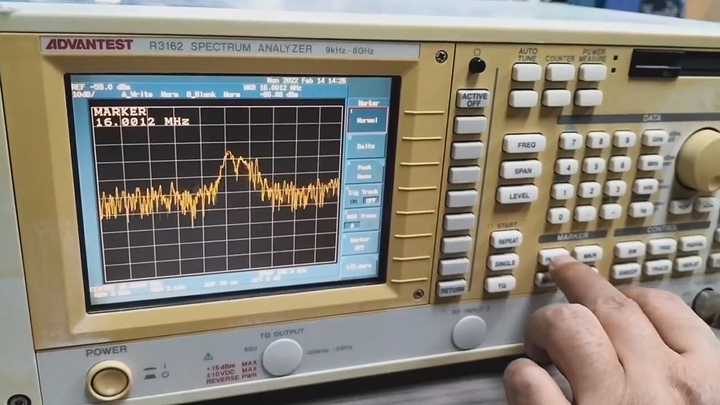

對于許多對時鐘精度要求極高的應用場景,如通信設備中的射頻電路、高精度的測量儀器以及計算機的內存時鐘等,晶振的頻差必須嚴格控制在極小的范圍內。哪怕是極其微小的頻差,都可能在長時間的運行過程中積累,導致信號傳輸錯誤、數據處理偏差等嚴重問題,進而影響整個系統的性能和可靠性。

激勵電平與頻差的微妙平衡

激勵電平和頻差之間并非相互獨立,而是存在著微妙的關聯。當激勵電平發生變化時,晶振內部的物理特性也會隨之改變,從而間接影響其頻差。例如,過大的激勵電平可能會使晶振的石英晶片產生非線性的機械振動,進而導致頻率漂移,增大頻差。

在晶振選型過程中,必須綜合考慮激勵電平和頻差這兩個因素,以達到二者之間的最佳平衡。一方面,要根據電路的實際需求,選擇具有合適頻差指標的晶振,確保其能夠滿足系統對時鐘精度的要求。另一方面,在設計振蕩電路時,要合理設置激勵電平,避免因激勵不當而影響晶振的頻率穩定性。

為了實現這一微妙平衡,工程師們需要在多個方面進行細致的考量與調試。首先,在選擇晶振時,應仔細研讀其規格書,了解其推薦的激勵電平范圍以及在不同激勵條件下的頻差特性。同時,要充分考慮電路的工作環境,如溫度變化范圍、電源穩定性等因素,因為這些環境因素會對晶振的激勵電平需求和頻差表現產生影響。

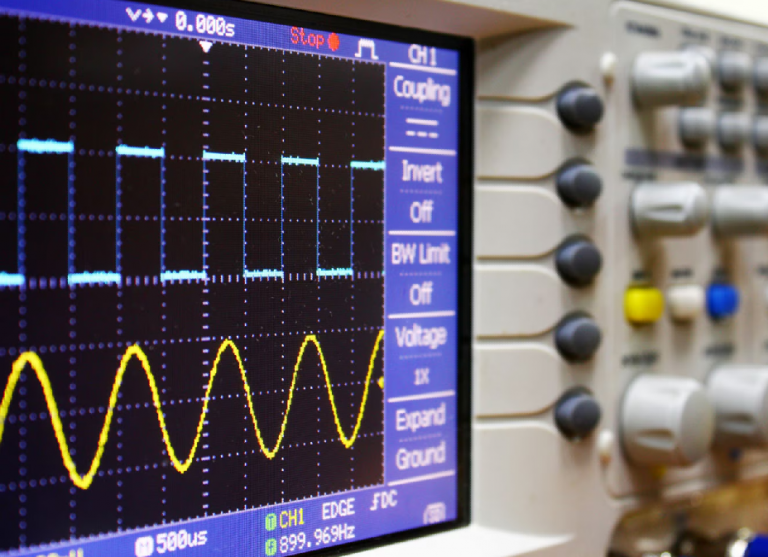

在電路設計階段,需要通過精確的電路計算和模擬仿真,確定合適的振蕩電路參數,如匹配電容C1、C2的取值以及串聯電阻Rd的大小等,以保證在滿足晶振激勵電平要求的同時,將頻差控制在可接受的范圍內。此外,在實際的電路板布局布線過程中,也要注意減少雜散電容和電磁干擾對晶振的影響,因為這些因素可能會改變晶振的實際負載條件,進而影響激勵電平和頻差。

在電子設備的晶振選型過程中,激勵電平與頻差之間的微妙平衡是一個不可忽視的重要細節。只有充分認識到這兩個因素的相互關系,并通過合理的選型和精心的電路設計來實現二者的最佳平衡,才能確保晶振為整個電路系統提供穩定、精確的時鐘信號,從而保障電子設備的高性能、高可靠性運行。

審核編輯 黃宇

-

晶振

+關注

關注

35文章

3610瀏覽量

73710

發布評論請先 登錄

常用晶振的技術指標有哪些

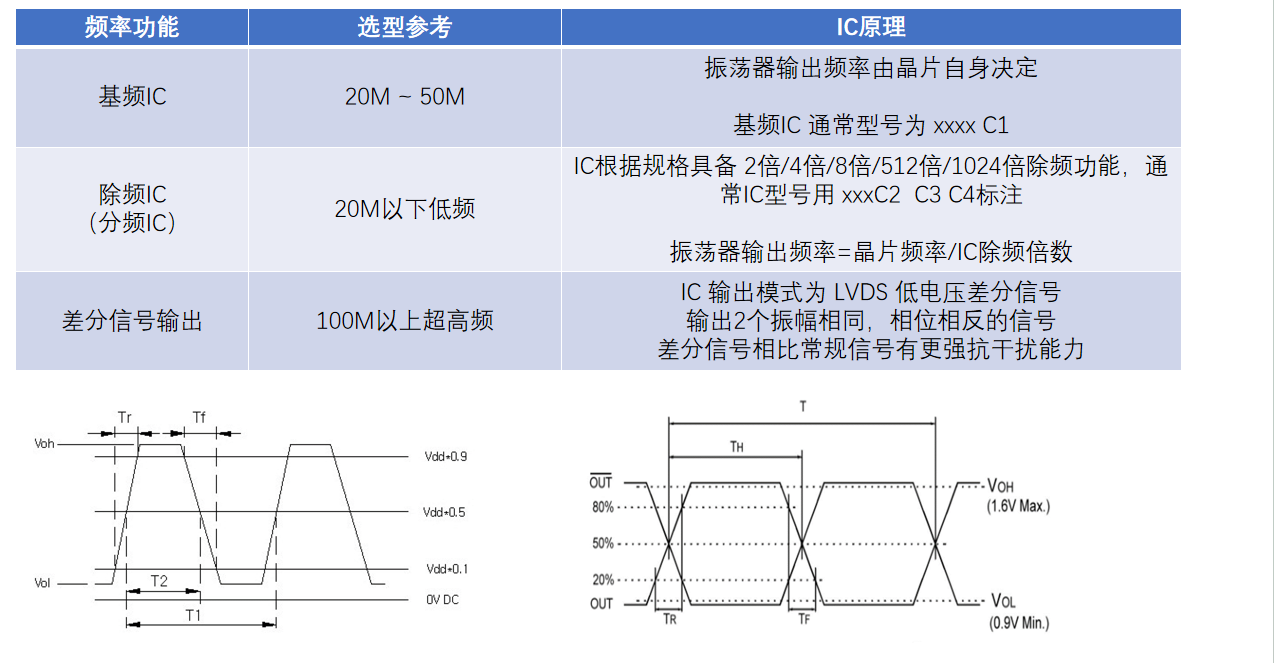

一探究竟差分晶振

展頻晶振有哪些特點和應用

晶振頻偏超差?這5個核心因素正在悄悄改變你的時鐘精度

激勵電平與頻差的微妙平衡:晶振選型不可忽視的細節

激勵電平與頻差的微妙平衡:晶振選型不可忽視的細節

評論