這是由常用的電路結構所決定的,低電平時電路往往有較高電平時更低的環路阻抗,而低阻抗則意味著抗干擾能力更強。

結合實際講一個有用的例子來加深印象:

有的同學可能已經學習了這樣的一條PCB布線規則:在條件許可的情況下,高電平有效線要盡量縮短,低電平有效的線則盡量延長。這一條規則的存在基礎就是基于低電平時環路阻抗比較低,抗干擾能力比較強才起來的。

如OC或OD電路要控制一個電平就是通過它這個開關的通斷來實現的。

有在上拉電阻的情況下,開關接通,得低電平;開關切斷,得高電平。這樣,為了防止電路失控的情況下仍然是有效電平,那么當然是低電平有效才更“保險”了。結構上,象OC電路那樣,由于集電極更難擊穿,所以,也更不容易損壞。

對于其它圖騰柱輸出的電路,雖然0和1都有同樣的風險,但應用中還是有人愿意加一個上拉電阻,以取得類似OC或OD輸出的效果。至于為什么不采用下拉電阻而用上拉電阻,大家也可以分析一下。

另一個方面是OC或OD輸出的電路,使用上拉電阻后具有節能的效果。因為關斷后它是具有獲得高電平時的電流幾乎為0。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

單片機

+關注

關注

6076文章

45495瀏覽量

670383 -

上拉電阻

+關注

關注

5文章

366瀏覽量

31667 -

低電平

+關注

關注

1文章

238瀏覽量

13987

原文標題:為什么單片機管腳設計成低電平才有效?

文章出處:【微信號:mcugeek,微信公眾號:MCU開發加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

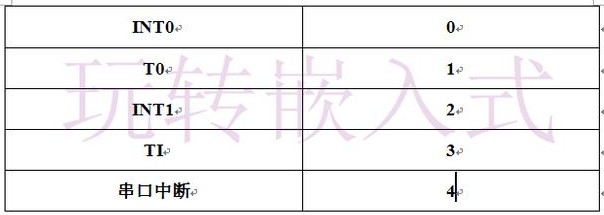

51單片機中斷用法實例解析

51單片機的外部中斷0引腳接一只按鍵,該按鍵通過上拉電阻接到電源,即沒有按鍵發生時單片機檢測到的是高電平,當按鍵按下時單片機檢測到的是低電平

發表于 12-12 15:31

?2.6w次閱讀

C語言單片機等待詢問_51單片機編程實例大全(下部)

P1.0輸出低電平}// 實例 2:用單片機控制一個燈閃爍:認識單片機的工作頻率#include //包含單片機寄存器的頭文件/ 函數功能

發表于 11-21 09:51

?10次下載

單片機IO口低電平不為0V

,高電平正常,低電平都是0.7V左右。原因分析:出現這樣的問題讓我有點懷疑人生,在網絡上一直沒有查到答案。我一度以為是LPC1778這種片子使用了三極管而非MOS管作為IO輸出電路。第二天請教了一個同事后,幫我細看了一下圖紙,發

發表于 12-04 10:51

?6次下載

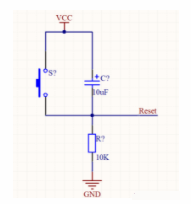

電子設計(4)高電平、低電平復位電路

初學51單片機,可能不太理解復位電路,復位電路有高電平和低電平兩種,C51是高電平復位,現在一般的MCU都是低電平復位。

發表于 12-08 11:51

?15次下載

為什么單片機管腳設計成低電平才有效

它是由常用的電路結構所決定的,低電平時電路往往有較高電平時更低的環路阻抗,而低阻抗則意味著抗干擾能力更強。結合實際講一個有用的例子來加深印象:我們有的同學可能已經學習了這樣的一條PCB布線

發表于 01-14 14:44

?2次下載

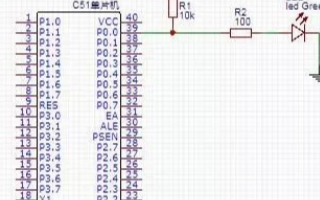

利用單片機點亮流水燈實例解析

首先我們規劃好硬件電路部分,在這里使用三個流水燈做簡單講解吧。單片機使用簡單基礎的51單片機。利用單片機P3.0~P3.2 三個I0口,假如外部電源給LED供電,IO口就輸出低電平時(

單片機實例100例

/實例3:用單片機控制第一個燈亮

#include //包含51單片機寄存器定義的頭文件

void main(void)

{

P1=0xfe; //P1=1111 1110B,即P1.0輸出

發表于 01-03 14:32

?4次下載

stm8和stc單片機比較 單片機的輸出信號是什么電平 stm8s單片機采用那種電平

單片機的輸出信號電平可以是高電平(通常為Vcc電壓,即正電源電壓)或低電平(通常為GND電壓,即接地電壓),具體取決于單片機的設計

發表于 04-01 15:55

?5551次閱讀

單片機中的外部中斷低電平觸發和下降沿觸發有什么區別

單片機中的外部中斷低電平觸發和下降沿觸發有什么區別? 外部中斷是單片機中的一種功能,在特定條件下,外部信號的變化可以引發中斷,從而改變程序的執行流程。外部中斷可以通過不同的觸發方式來激活,包括

基于單片機管腳設計成低電平的原因以及實例解析

基于單片機管腳設計成低電平的原因以及實例解析

評論