可編程片上系統( SoPC)是在可編程邏輯器件的基礎上發展起來的一種靈活、高效的嵌入式系統設計解決方案,系統設計者可以從傳統的板級系統設計轉換到芯片級系統設計,將系統設計中所需要的各個功能單元以IP ( Intellectual Property)的形式集成到FPGA中,實現集成度更高的嵌入式系統。

Virtex-4系列FPGA是由Xilinx公司推出的包含多個面向特定領域平臺的FPGA產品,各個系列的FPGA通過對嵌入式處理器、高性能DSP功能單元、增強時鐘管理、存儲器、并行和串行I/O、混合信號以及其它功能模塊等的優化組合使其可以滿足特定領域的應用需求。Virtex-4系列的三個平臺分別是:針對邏輯應用的Virtex-4 LX,針對超高性能信號處理的Virtex-4SX,針對嵌入式處理和高速串行連接的Virtex-4 FX。其中Virtex-4 FX系列FPGA主要是為復雜系統應用提供優化,特別是網絡、存儲、電信和嵌入式應用中的高速串行連接和嵌入式處理,在其配套的EDK環境中還為系統設計者提供豐富的總線、時鐘、外設、JTAG口等IP資源,使設計者能夠方便的搭建自己的嵌入式系統。

1Virtex-4 FX系列FPGA介紹

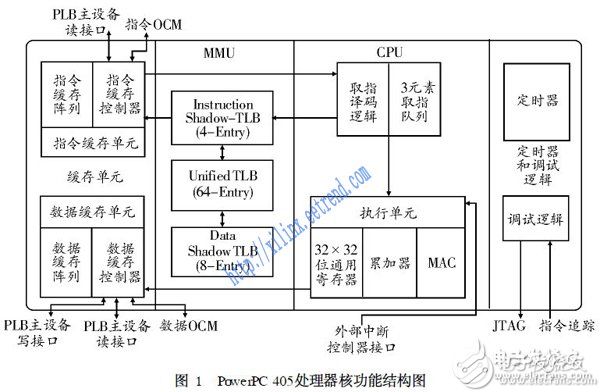

Virtex-4 FX系列FPGA芯片內至少包含一個PowerPC405處理器核,其功能結構如圖1所示,該處理器核為32位哈佛結構的R ISC硬核,最高工作頻率為400MHz。PowerPC405處理器包括以下功能單元: ( 1)5級數據通道流水線,包括取指、譯碼、執行、寫回、裝入寫回5 級流水段; ( 2 ) 一個虛擬內存管理單元(MMU) ,支持可變頁面大小和寫保護、控制訪問選項;(3)獨立的指令Cache和數據Cache; ( 4)支持調試和跟蹤,包含一個JTAG接口; ( 5)三個可編程計時器。另外, PowerPC 405硬核還具有如下特點: ( 1)支持硬件乘法和除法; ( 2) 32個32位通用寄存器; ( 3) 16KB兩路組相聯方式指令緩存( set-associave) ; (4) 16KB兩路組相聯方式數據緩存、寫回/寫直達; ( 5 ) 實現PowerPC用戶指令集架構(U ISA) ; ( 6)專用的片上存儲器接口(OCM) ; ( 7 )支持IBM CoreConnect總線架構。

CoreConnect總線架構是由IBM開發的一種片上總線通信連接技術。CoreConnect總線包括處理器局部總線( PLB) 、片上外設總線(OPB)和設備控制寄存器總線(DCR) 。PLB總線為主設備和從設備之間提供高帶寬、低延遲的連接,OPB總線為連接具有不同總線寬度和時序要求的外設提供了一條途徑,減少了對PLB性能的影響,DCR總線用來控制PowerPC405處理器中的通用寄存器和設備寄存器之間的數據傳輸。

2基于SoPC的嵌入式系統設計技術

2. 1平臺技術

在平臺的基礎上來構建嵌入式系統為設計者提供了極大的便利, Xilinx 推出的嵌入式開發工具包( EDK)集成了諸如硬件平臺產生器(platgen) 、硬件仿真模型產生器( SimGen) 、軟件平臺產生器( libgen) 、應用軟件編譯工具(GNU Compiler) 、軟件調試工具(GNU Debugger) 等一系列工具。設計者可以通過集成在EDK環境下的Xilinx平臺工作室(XPS)方便的調用各種工具進行基于SoPC的嵌入式系統設計。EDK環境下為系統設計者提供了豐富的IP資源,可利用現有的資源迅速搭建自己的嵌入式系統,完成整個PowerPC系統硬件的開發。如果開發工具包提供的IP庫不能滿足系統設計者的需求,設計者也可定制自己的IP。圖2所示為EDK開發環境圖形界面。

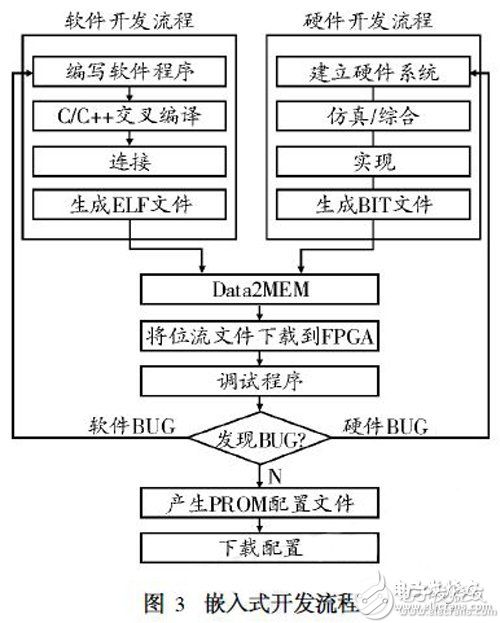

EDK環境為其自帶的IP提供了相應的驅動程序及相關的函數,設計者可以通過調用這些函數加快應用程序的開發。對于設計者自行研制的IP,則需要編寫相應的驅動程序。應用程序編寫完成后,調用EDK下的GNU工具,編譯連接生成可執行文件,再將硬件、軟件文件結合在一起,產生可下載的位流文件下載到FPGA,使用Xilinx微處理器調試工具(XMD ) 連接GNU調試工具進行應用程序調試,在確認應用程序正確無誤,能實現系統功能之后,即可將位流文件轉換成PROM的配置文件(MCS文件) 下載到目標板上的PROM,從而完成整個設計開發。圖3為利用EDK工具進行嵌入式系統開發的流程。

2. 2系統架構及硬件設計

基于SoPC的嵌入式系統設計過程中,系統設計者首先要明確設計需求,這對于整個設計具有指導性作用,也是將來設計完成后檢驗設計是否可用的標準之一。系統設計者根據設計需求來確定其系統架構,定義系統主要模塊組成,決定其接口類型、總線結構、硬件功能及軟件功能,完備的系統架構定義要能滿足基本的設計需求,并能最大限度的提高系統整體性能。

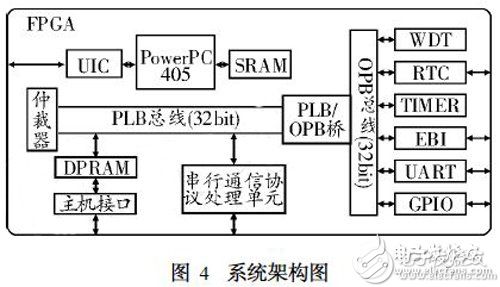

基于SoPC的多路傳輸數據總線接口的設計需求是在板級多路傳輸數據總線接口模塊的基礎上提出的,通過對板級器件的IP化,將原有板上芯片以IP的形式集成到FPGA中,用單片集成電路實現原板級電路的設計。根據板級多路傳輸數據總線接口模塊的系統結構,提出了如圖4所示的基于SoPC的嵌入式系統架構圖,該嵌入式系統集成了PowerPC405處理器、串行通信總線協議處理器,具有實時時鐘(RTC) 、看門狗(WDT) 、計時器( TIMER)功能,可實現GJB289A-97(數字式時分制指令/響應型多路傳輸數據總線)中規定的RT/BC功能,支持實現ISBC協議(改進的靜態總線控制協議) ,通過方式選擇分別支持LBE總線訪問、VME總線訪問、PC I總線訪問(通過PLX9054 橋接器) 、PCI-Express總線訪問(通過PEX8311橋接器)四

種主機接口訪問方式。

硬件設計過程中,系統設計者在XPS圖形界面下調用現成的IP庫,搭建SoPC的硬件環境,通過硬件平臺產生器(p latgen)生成硬件文件,其中PowerPC405處理器、雙口存儲器、SRAM、串行通信總線協議處理單元掛接在PLB總線上;實時時鐘(RTC) 、看門狗(WDT) 、計時器(TIMER) 、外部總線接口( EB I) 、通用輸入輸出接口( GPIO) 、串口控制器(UART)掛接在OPB 總線上;通用中斷控制器(UIC) 、仲裁器和PLB /OPB 橋的寄存器通過DCR總線訪問。硬件架構搭建起后通過硬件仿真模型產生器( SimGen)對硬件的功能進行仿真。

2. 3軟件設計

基于SoPC的嵌入式系統軟件設計過程中,軟件設計者要明確嵌入式系統的相關硬件配置,諸如內存地址映射關系,硬件寄存器配置等,這將決定開發出的嵌入式軟件是否具備實用性。嵌入式軟件的設計通常包括CPU啟動代碼,系統初始化代碼,硬件自測試程序,設備驅動程序,實時操作系統及應用軟件等,根據不同的系統需求,軟件包含的內容稍有差異。軟件設計階段,設計者將選擇出編譯和調試工具并完成編程。

基于SoPC的多路傳輸數據總線接口的軟件由初始化程序、自測試程序、BC /RT控制程序組成。基于SoPC的嵌入式軟件開發是在EDK環境下采用C語言編程實現的,通過軟件平臺產生器( libgen) 、應用軟件編譯工具(GNU Compiler)編譯連接得到可執行文件,該文件可與生成的硬件位流文件通過JTAG接口一起下載到FPGA 運行,也可先將位流文件固化到外部PROM中,應用軟件的可執行文件轉換成二進制文件固化到外部FLASH中,系統上電后自動加載硬件邏輯并將應用軟件搬家到SRAM運行。各部分軟件完成如下的功能:初始化程序完成CPU初始化及相關功能單元的初始化;自測試程序完成系統的上電自測試和內部自檢; BC /RT控制程序完成該嵌入式系統作為BC或RT時的數據傳輸控制。基于SoPC的嵌入式系統硬件設計和軟件設計可以并行開展,利用軟硬件協同設計的思想,可加快整個嵌入式設計的速度。

2. 4測試驗證

基于SoPC的嵌入式系統設計的測試驗證用來保證系統不存在軟件和硬件上的缺陷。軟件測試驗證旨在通過執行軟件并觀察其行為是否滿足設計要求,而硬件測試驗證則包括了確保硬件能夠對外在的激勵作出正確的響應并能正確的執行軟件。

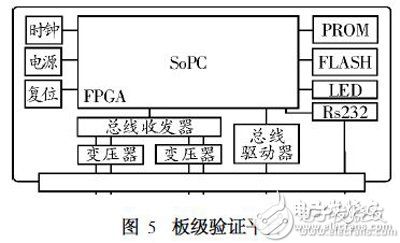

基于SoPC的多路傳輸數據總線接口中復雜的軟硬件結構及其種類繁多的IP資源,使得該系統的測試驗證工作也變得復雜。在測試驗證過程中,采用多級測試驗證技術,首先對各單一模塊進行仿真測試,進行軟硬件協同驗證,再通過集成各個功能模塊進行系統集成驗證,最后進行板級驗證。在進行系統各模塊功能驗證時,軟件可以作為硬件測試的信號源,針對各個模塊都編寫相應的C語言測試向量,進行功能覆蓋率測試。在單一功能模塊驗證測試的基礎上,將各模塊集成為一個完整的系統,對整個系統進行集成測試。進行板級驗證時,可以運行更為完整、更接近實際應用的C程序測試向量,使得測試更全面、更可靠。圖5所示為板級驗證平臺示意圖。

3結束語

本文通過對Xilinx公司Virtex-4 FX系列FPGA的介紹,分析了其內嵌的PowerPC405處理器的體系結構及CoreConnect總線的特點,通過基于SoPC的多路傳輸數據總線接口的硬、軟件設計技術和驗證技術的介紹,更好地闡述了基于SoPC的嵌入式系統設計方法。在基于SoPC的嵌入式系統設計中,通過單片FPGA實現多片專用芯片的功能,減少器件數目,縮小系統面積,增加系統可靠性,達到了對板級多路傳輸數據總線接口模塊小型化、集成化的目的。基于SoPC的嵌入式系統設計以其數據處理速度快、集成度高、開發周期短、應用靈活方便等特點,相信在航空航天領域將會得到廣泛的應用。

-

FPGA設計

+關注

關注

9文章

431瀏覽量

28196 -

SOPC技術

+關注

關注

2文章

23瀏覽量

14417

發布評論請先 登錄

系統嵌入式的學習路線

高云半導體助力2025全國大學生嵌入式與系統設計大賽FPGA賽段圓滿落幕

嵌入式與FPGA的區別

嵌入式開發的關鍵點介紹

盤點嵌入式就業所需要的技能有哪些?

怎么結合嵌入式,Linux,和FPGA三個方向達到一個均衡發展?

探討基于sopc技術的fpga集成嵌入式系統設計

探討基于sopc技術的fpga集成嵌入式系統設計

評論